50-52刷题

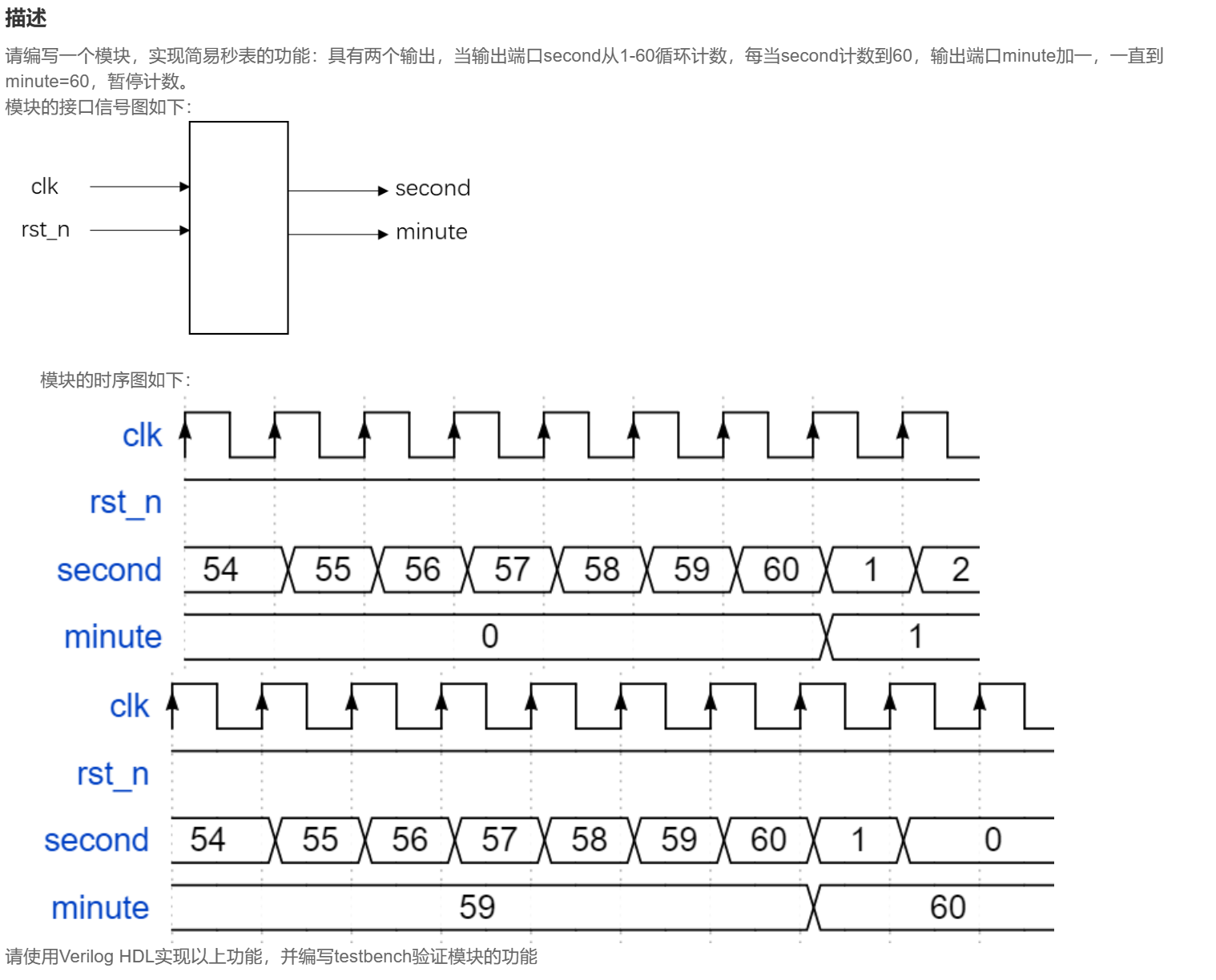

50

`timescale 1ns/1ns

module count_module(

input clk,

input rst_n,

output reg [5:0]second,

output reg [5:0]minute

);

wire add_cnt0;

wire end_cnt0;

wire add_cnt1;

wire end_cnt1;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

second <= 0;

end

else if(add_cnt0)begin

if(end_cnt0)

second <= 1;

else if (minute == 60)

second <= 0;

else

second <= second + 1;

end

end

assign add_cnt0 = 1 ;

assign end_cnt0 = add_cnt0 && second== 60;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

minute <= 0;

end

else if(add_cnt1)begin

if(end_cnt1)

minute <= 60;

else

minute <= minute + 1;

end

end

assign add_cnt1 = end_cnt0;

assign end_cnt1 = add_cnt1 && minute== 60 ;

endmodule

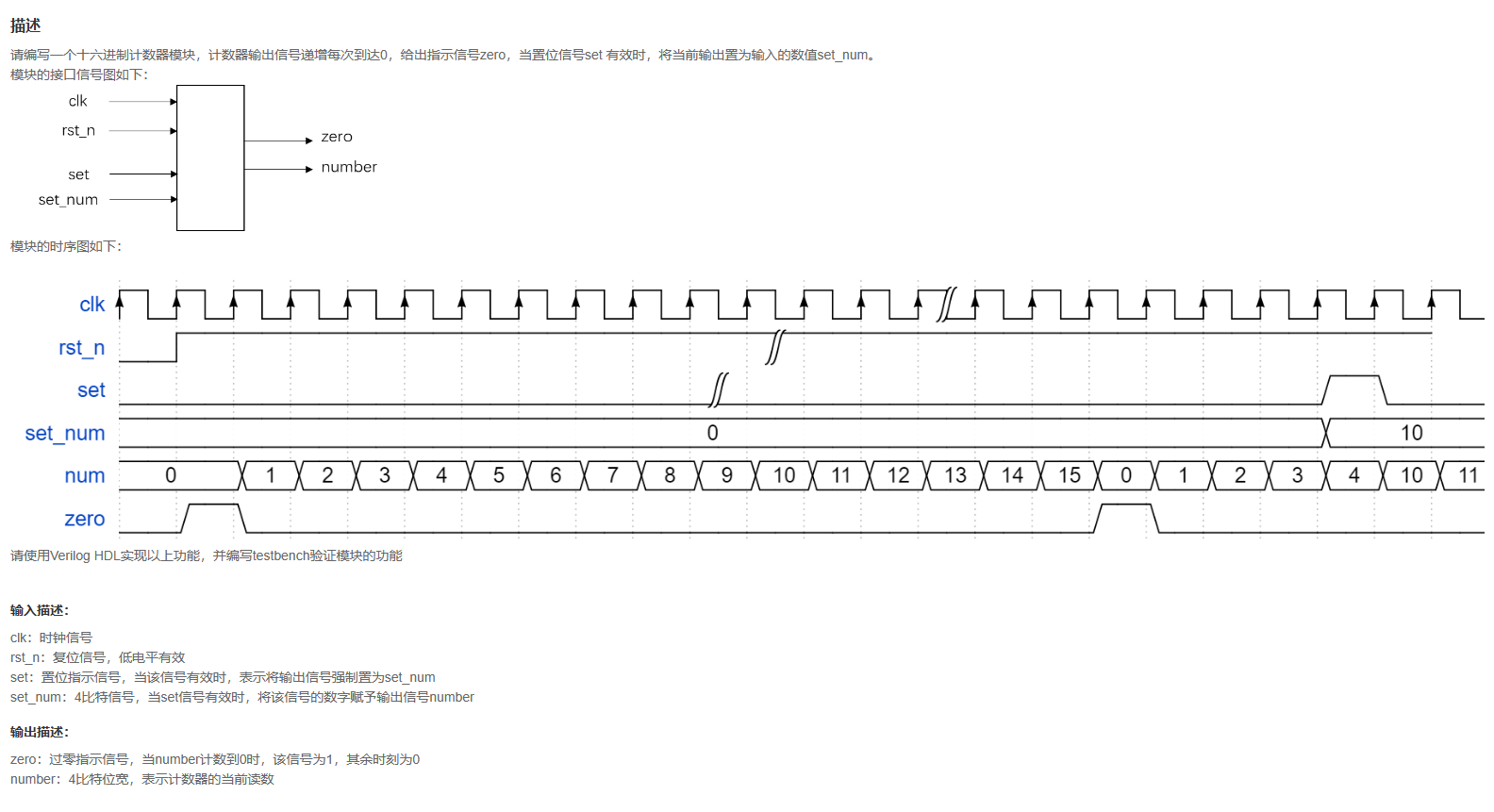

51

可置位计数器_牛客题霸_牛客网 (nowcoder.com)

`timescale 1ns/1ns

module count_module(

input clk,

input rst_n,

input set,

input [3:0] set_num,

output reg [3:0]number,

output reg zero

);

//有问题 需要打一拍 就离谱

wire add_cnt;

wire end_cnt;

reg [3:0]cnt;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt <= 0;

end

else if(add_cnt)begin

if(end_cnt)

cnt <= 0;

else if(set)

cnt <= set_num;

else

cnt <= cnt + 1;

end

end

assign add_cnt = 1;

assign end_cnt = add_cnt && cnt== 15;

//开始有一个 零输出 tip

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

zero <= 0;

end

else if(cnt == 0) begin

zero <= 1;

end

else begin

zero <= 0;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

number <= 0;

end

else begin

number <= cnt;

end

end

endmodule

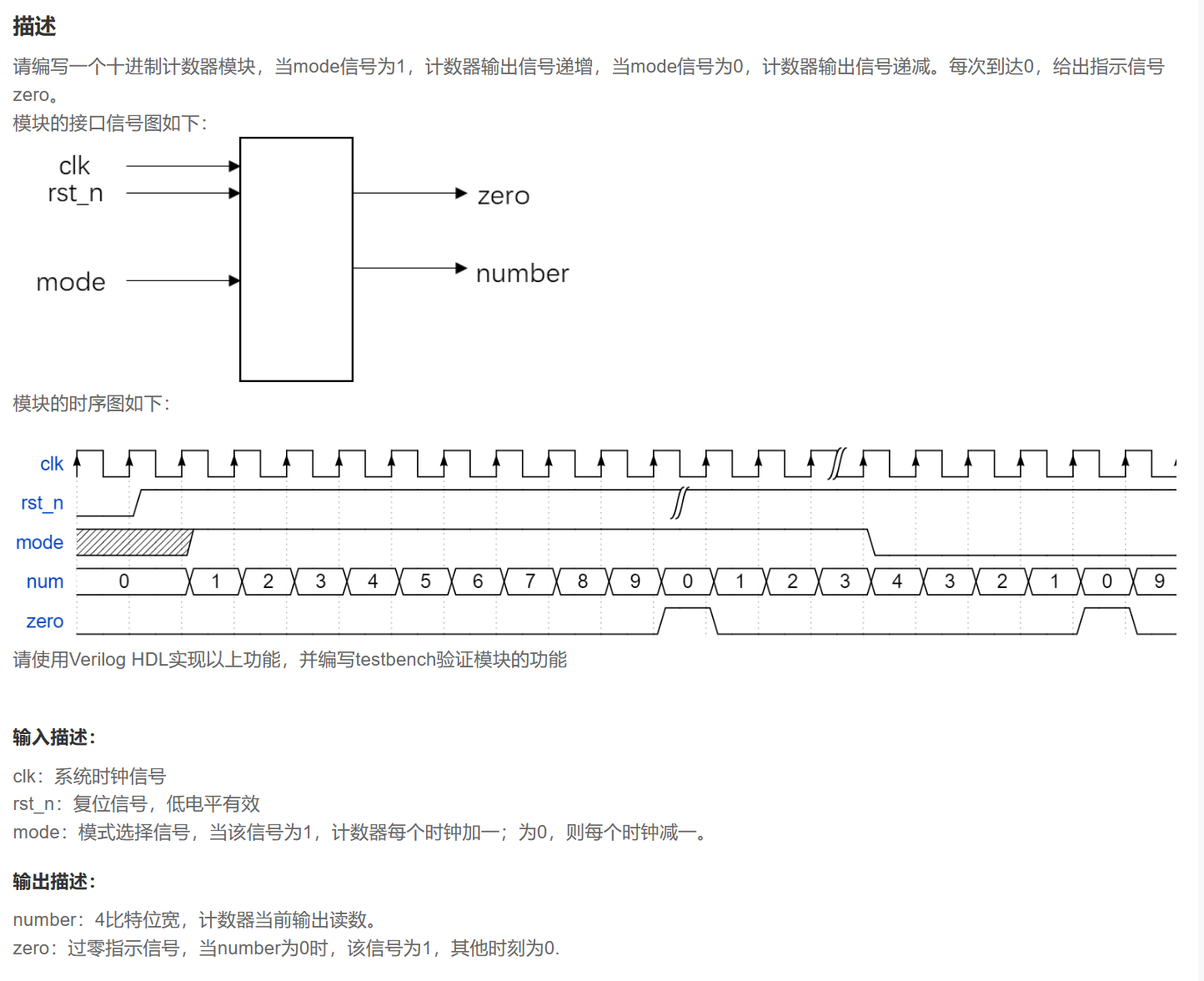

52

`timescale 1ns/1ns

module count_module(

input clk,

input rst_n,

input mode,

output reg [3:0]number,

output reg zero

);

wire add_cnt;

wire end_cnt;

reg [3:0] cnt;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt <= 0;

end

else if(add_cnt)begin

if(end_cnt)

cnt <= 0;

else

cnt <= cnt + 1;

end

else if(dec_cnt)begin

if(dend_cnt)

cnt <= 9;

else

cnt <= cnt - 1;

end

end

assign add_cnt = mode == 1;

assign end_cnt = add_cnt && cnt== 9;

assign dec_cnt = mode == 0;

assign dend_cnt = dec_cnt && cnt== 0;

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

number <= 0;

end

else begin

number <= cnt;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

zero <= 0;

end

else if(cnt == 0)begin

zero <= 1;

end

else begin

zero <= 0;

end

end

endmodule