CCI(Cache Coherent Interconnect)是ARM中的cache一致性控制器。

CCI-400将互连和一致性功能结合到一个模块中。它支持多达两个ACE 主节点的连接,例如:

- Cortex®-A7 processor

- Cortex-A15 processor

- Cortex-A17 processor

- Cortex-A53 processor

- Cortex-A57 processor

CCI-400还支持多达三个ACE-Lite主站,例如,ARM MaliTM-T600系列图形处理器单元(GPU)。

所有这些接口都有可选的DVM消息支持,以管理分布式内存管理单元(MMU),例如CoreLink MMU-400。这些单元可以通过CCI-400与最多三个ACE-Lite从机进行通信。

硬件管理的一致性可以通过共享片上数据来提高系统性能和降低系统功耗。

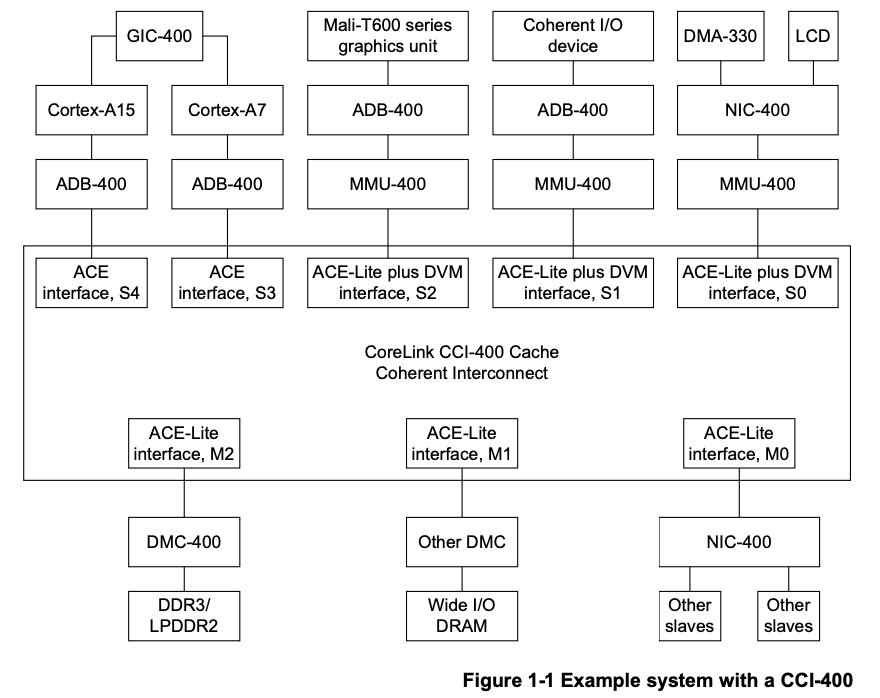

CCI-400cache一致性控制器实现了ACE协议,demo系统框图如下所示:

- CCI-400cache一致性控制器是一个基础设施组件,支持以下内容:

- 在最多两个ACE主站和三个ACE-Lite主站之间的数据一致性,有三个独立的序列化点(PoS)和全屏障支持。

- 主站和最多三个从站之间的高带宽、跨栏互连功能。

- 主站之间的DVM消息传输。

- QoS虚拟网络(QVN)。

- 服务质量(QoS)调节,用于塑造流量曲线。

- 性能监测单元(PMU),统计与性能有关的事件。

- 一个程序员视图(PV),控制一致性和互连功能。