1.1.5 宽摆幅电流镜

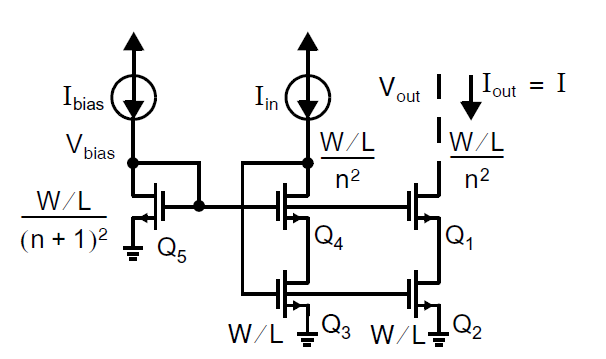

随着更新的工艺使用沟道长度变得更短,由短沟道效应引起的晶体管输出阻抗退化使得获得合理的放大器增益变得更加困难,这就导致设计者经常不得不使用Cascode电流镜,然而不幸的是,传统Cascode电流镜限制了信号摆幅,这在部分应用中是无法容忍的。好在,还是有并不像之前讨论的Cascode或者Wilson电流镜那样限制信号摆幅的电路存在的。一种电路就是如下图所示的宽摆幅Cascode电流镜:

这个电流镜的基本思路是偏置晶体管\(Q_2\)和\(Q_3\)的漏源电压使其尽可能地小到接近线性区。如果使用上图中的晶体管尺寸,并假设平方律对所有的长沟道器件成立,\(Q_2\)和\(Q_3\)将会刚好被偏置在线性区边缘。在看具体这些偏置电压如何产生之前,首先注意\(Q_3\)和\(Q_4\)在为\(Q_3\)产生栅源电压时表现得像一个二极管接法得单管。这两个晶体管得工作状态很像\(Q_3\)得栅极接在漏极上单独工作得状态。之所以引入\(Q_4\)是为了降低\(Q_3\)得漏源电压从而使得其和\(Q_2\)的漏源电压能够匹配。这个匹配使得输出电流\(I_{out}\)能够更精确的匹配上输入电流\(I_{in}\),如果没有\(Q_4\),那么那么输出电流将会由于\(Q_2\)和\(Q_3\)的有限输出阻抗而变得略小于输入电流,除此以外,\(Q_4\)对电路的工作没有什么影响。

为了确定电路的电压偏置,令\(V_{eff}\)为晶体管\(Q_2\)和\(Q_3\)的有效栅源电压(过驱动电压),并假定所有的漏极电流相等,我们有:

进一步的,由于\(Q_3\)有着相同的漏电流但是其尺寸小\((n+1)^2\)倍,我们有:

同样的可以推导出\(Q_1\)和\(Q_4\)有相同的有效栅源电压:

因此:

进一步的有:

漏源电压将\(Q_2\)和\(Q_3\)都置于线性区边缘,因此最小的输出电压为:

一种常见的选择是\(n\)就是1,这种情况下电流镜的工作只需要满足:

一版\(V_{eff}\)的典型值在\(0.2V\)到\(0.25V\)之间,宽摆幅电流镜能够保证所有的晶体管都饱和,即使电流镜上的电压降到了\(0.4V\)到\(0.5V\)。

然而,还有一个必须满足的让所有晶体管饱和的条件是:

为了确保\(Q_4\)在饱和区,我们注意到\(Q_3\)连接在\(Q_4\)的漏极,为了确定\(V_{DS4}\),我们可以推出:

从结果上来看,我们只需要保证\(V_{tn}\)比\(nV_{eff}\)要大,对于\(Q_4\)来说就能保持在饱和区,这并不是一个很困难的要求。

需要注意的是上述的分析假定了偏置电流\(I_{bias}\)等于输入电流\(I_{in}\),然而一般来说\(I_{in}\)是一个变化的电流值,而\(I_{bias}\)需要被选定为一个定值。一种选择是把\(I_{bias}\)置于\(I_{in}\)预期的最大值,这种选择可以确保所有的器件不会离开饱和区,尽管\(Q_2\)和\(Q_3\)的漏源电压会比最大\(I_{in}\)输入时所需要的必要值更大,从结果上来看,会损失一部分的信号摆幅。在宽摆幅放大器中更常见的选择是将\(I_{bias}\)置于\(I_{in}\)的标称值。在这种设置下,一些器件进入线性区,其输出阻抗会随着更大的\(I_{in}\)而下降(比如在压摆率限制期间),但是这种影响在瞬态下往往是可以容忍的。

最后,有一些值得提起的设计建议,在多数应用下,有经验的设计者会将\((W/L)_5\)取得比\((W/L)/(n+1)^2\)更小,使得偏置管\(Q_2\)和\(Q_3\)的漏源电压比所需的最小值略大(大概大\(0.1V\)),增加这个值是因为晶体管实际上在线性区和饱和区之间没有一个很明确的边界,这样能够更好的确保晶体管处于饱和区。这个增加同样帮助抵消了\(Q_1\)和\(Q_4\)的体效应,使得他们的阈值电压增加,更加将\(Q_2\)和\(Q_3\)推向线性区。此外,为了减少耗散功率,\(Q_5\)和\(I_{bias}\)组成的偏置分子可以缩放到更小的电流,同时保持相同的电流密度,因此具有相同的有效栅源电压。另一个常见的修改是将\(Q_2\)和\(Q_3\)的长度比最小允许栅长更大一些(因为他们两端的栅源电压很小),但是\(Q_1\)和\(Q_4\)将比选成更长的栅长,因为输出晶体管(比如\(Q_1\))一般两端的电压更大,一个典型的尺寸是两倍于最小的栅长,这种栅长的选择可以帮助减小有害的短沟道效应,比如\(Q_1\)漏到衬底的漏电流。最小化\(Q_2\)和\(Q_3\)的长度可以最大化频率响应,因为他们的栅源电容是对于高频极点影响最大的电容。