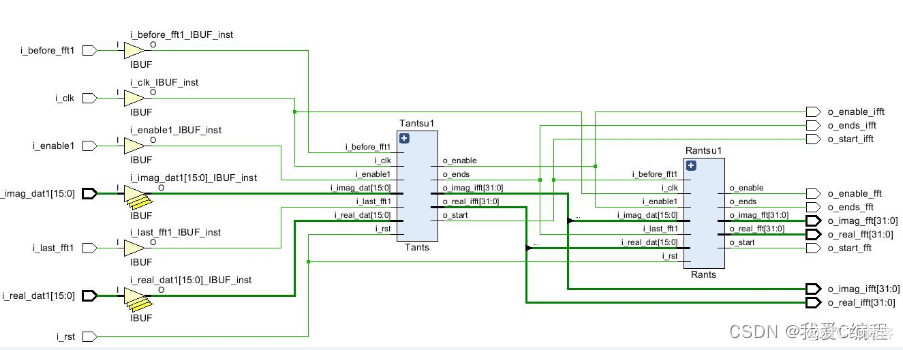

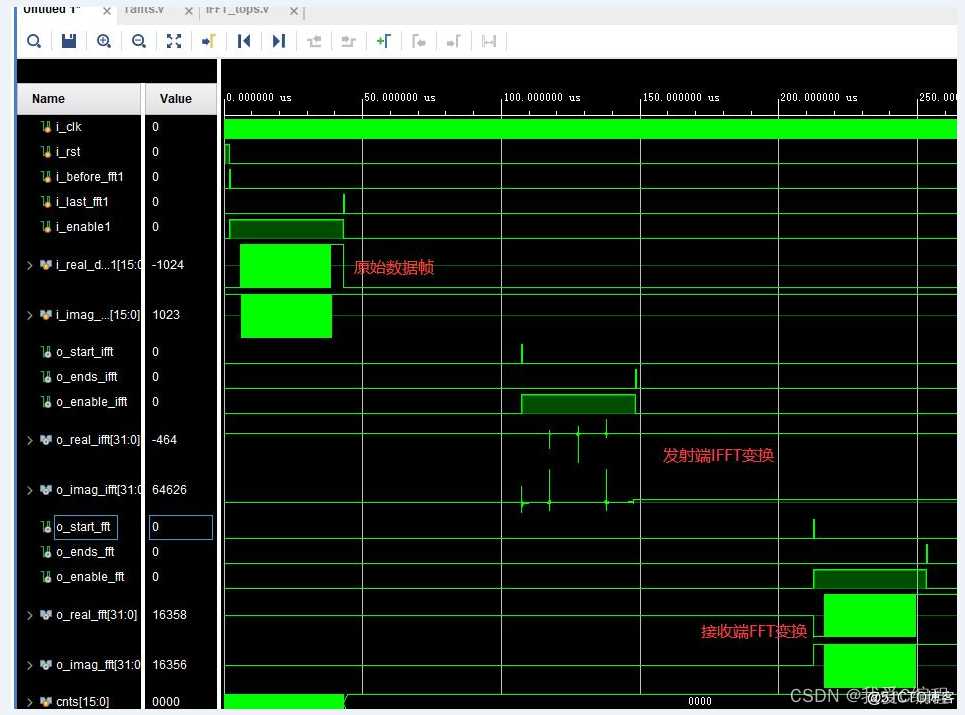

1.算法仿真效果

其中Vivado2019.2仿真结果如下

2.算法涉及理论知识概要

正交频分复用(Orthogonal Frequency Division Multiplexing, OFDM)是一种多载波调制技术,其基本原理是将高速数据信号分成多个低速子载波,在每个子载波上调制数据,将所有子载波叠加在一起形成OFDM信号。OFDM信号具有良好的抗多径衰落和频率选择性衰落能力,因此被广泛应用于无线通信和数字电视等领域。

OFDM主要思想是:将信道分成若干正交子信道,将高速数据信号转换成并行的低速子数据流,调制到在每个子信道上进行传输。正交信号可以通过在接收端采用相关技术来分开,这样可以减少子信道之间的相互干扰(ISI) 。每个子信道上的信号带宽小于信道的相关带宽,因此每个子信道上可以看成平坦性衰落,从而可以消除码间串扰,而且由于每个子信道的带宽仅仅是原信道带宽的一小部分,信道均衡变得相对容易。

OFDM技术是HPA联盟(HomePlug Powerline Alliance)工业规范的基础,它采用一种不连续的多音调技术,将被称为载波的不同频率中的大量信号合并成单一的信号,从而完成信号传送。由于这种技术具有在杂波干扰下传送信号的能力,因此常常会被利用在容易受外界干扰或者抵抗外界干扰能力较差的传输介质中。

一个OFDM符号之内包含多个经过相移键控(PSK)或者正交幅度调制(QAM)的子载波。

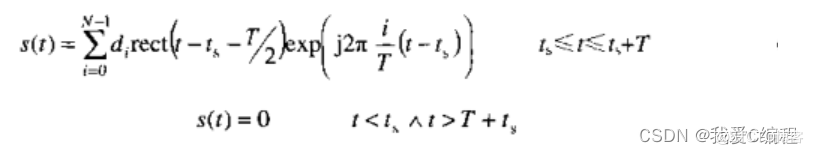

一旦要把传输的比特分配到各个子载波上,某一种调制模式则将他们映射为子载波的幅度和相位,通常采用等效基带信号来描述OFDM的输出信号:

其中信号的实部和虚部分别对应OFDM的同相和正交分量,在实际系统可以分别与对应的c o s coscos分量和s i n sinsin分量相乘。

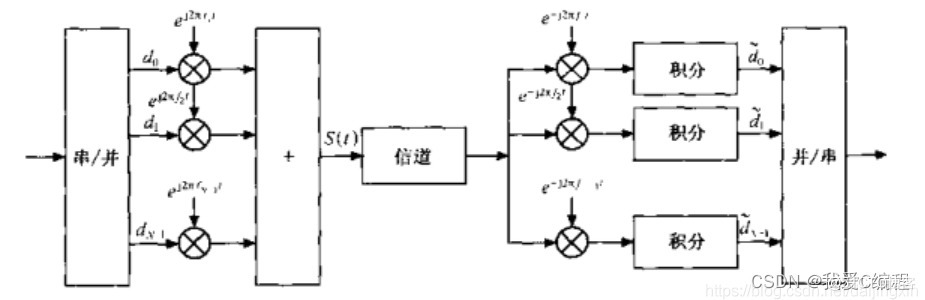

OFDM调制解调系统由发射端和接收端组成。在发射端,输入的数字信号经过调制和IFFT处理后形成OFDM信号,送入射频模块进行射频处理,最后通过天线发送。在接收端,接收到的OFDM信号经过射频前端处理后,经过FFT变换和解调后输出数字信号。

OFDM调制解调系统的设计过程可以分为以下几个步骤:

系统需求分析:根据系统的应用场景和性能要求,确定系统的功能模块、数据处理方式、接口规格和性能指标等。

系统架构设计:设计系统的硬件平台、软件平台、通信接口和数据传输方式等,确定系统的总体架构和模块划分。

功能模块设计:设计系统的各个功能模块,包括OFDM调制模块、IFFT模块、FFT模块、解调模块等。

3.Verilog核心程序

`timescale 1ns / 1ps

module OFDM_tops(

i_clk,

i_rst,

i_before_fft1,

i_last_fft1,

i_enable1,

i_real_dat1,

i_imag_dat1,

o_start_ifft,

o_ends_ifft,

o_enable_ifft,

o_real_ifft,

o_imag_ifft,

o_start_fft,

o_ends_fft,

o_enable_fft,

o_real_fft,

o_imag_fft

);

input i_clk;

input i_rst;

input i_before_fft1;

input i_last_fft1;

input i_enable1;

input signed[15:0]i_real_dat1;

input signed[15:0]i_imag_dat1;

output o_start_ifft;

output o_ends_ifft;

output o_enable_ifft;

output signed[31:0]o_real_ifft;

output signed[31:0]o_imag_ifft;

output o_start_fft;

output o_ends_fft;

output o_enable_fft;

output signed[31:0]o_real_fft;

output signed[31:0]o_imag_fft;