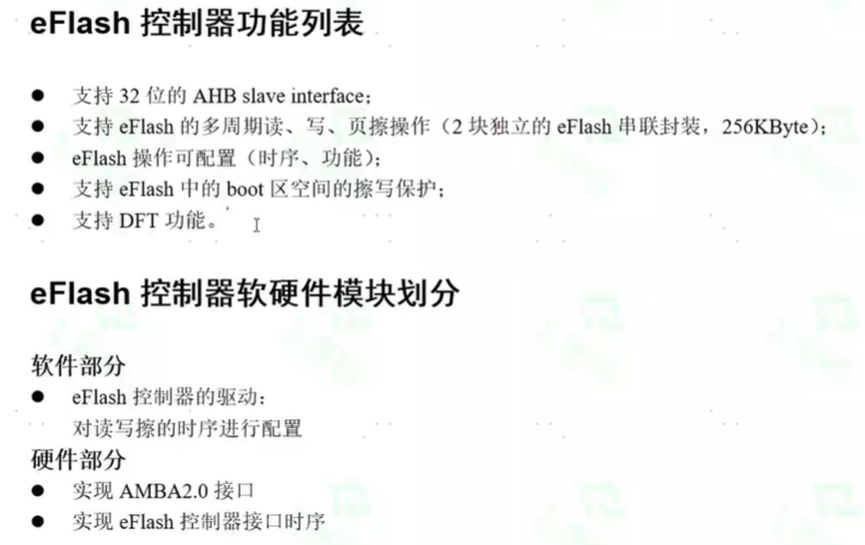

eFlash控制器的架构设计

1.架构设计思路分析

1.1 含有的模块分析

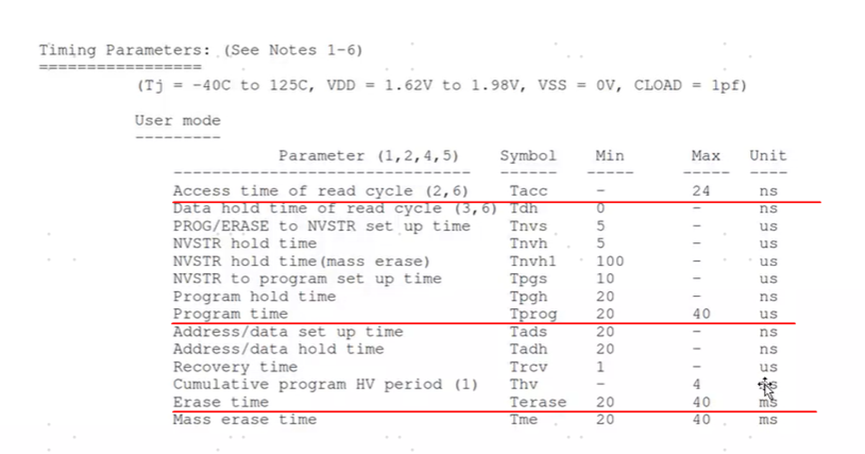

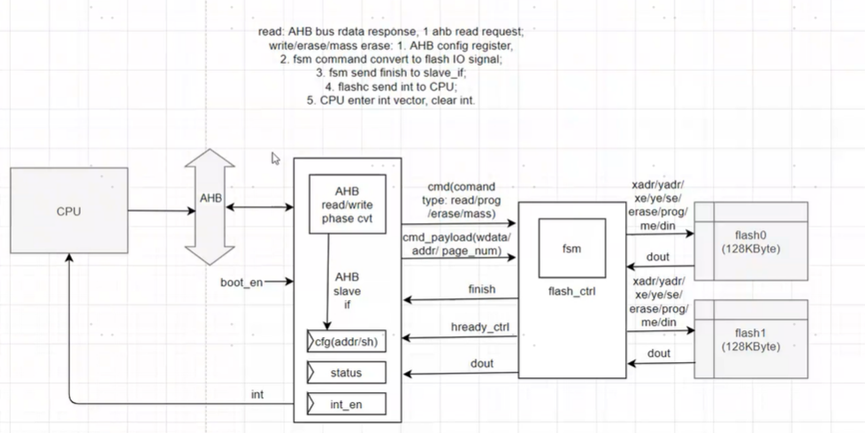

- eFlash控制器是一个基于AHB的slave,所以需要一个AHB_slave_if处理AHB的信号。AHB_slave_if与AHB总线进行交互,对主设备的请求进行处理,还可以设置一些内部的寄存器,对AHB发送过来的信号进行解析。

- AHB_slave_if除了处理AHB总线的信号,还需要配置一些寄存器,这些寄存器的作用是产生一些控制指令发送给Flash_ctrl,Flash_ctrl将指令转换为Flash的控制信号,对Flash进行读写。

- 将256kbyte的eFlash拆分成两块Flash(Flash0和Flash1),每一块Flash都是128kbyte,拆分之后可以通过片选及地址信号,选择性的读写擦除其中一个,有利于低功耗设计。

- 存在两个Flash,所以需要设计一个模块对于两块Flash进行控制,可以将这个控制Flash的模块单独设置一个Flash_ctrl模块。在SRAM控制器中,由于SRAMC的控制信号可以通过AHB信号转换为SRAM的控制信号,控制信号生成和转换的过程集成在AHB_sram_if中;这里Flash的控制信号相对比较复杂,所以单独设置Flash_ctrl进行Flash的控制。

1.2 Flash_ctrl信号分析

- Flash_ctrl接收AHB_slave_if模块发送过来的命令(cmd)和数据(cmd_payloads)。

cmd表示读写擦操作(read/write/prog/page erase/mass erase)。

cmd_payload表示于操作对应的信号,比如cmd是写操作,就要有写数据wdata,写到哪一页page_num,写的地址addr... - Flash_ctrl接收到AHB_slave_if发送的命令之后,生成具体的Flash控制信号发送给Flash0或者Flash1。发送的信号主要有xadr,yard,xe,ye,se,erase,prog,mas1.din等。

- Flash收到Flash_ctrl发送过来的控制信号之后,如果是读操作,Flash0或者Flash1会返回读数据(dout),Flash_ctrl接收到读数据之后,会进行汇总,通过一个mux将dout发送给AHB_slave_if,然后再作为hrdata返回给AHB总线。

1.3 读写操作控制

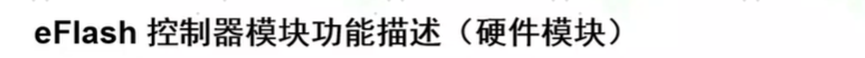

- 读操作,从前门的文档中可以知道,从Flash读取数据速度较快,大概需要24ns的时间,如果使用200M的时钟,时钟周期是5ns,读取Flash的数据需要5个cycle的时间。5个cycle时钟周期相对来说时间比较短,可以通过AHB总线,拉低hready_out(这里使用的是hready_ctrl)信号,延迟5个cycle,就可以将数据读出。

为了延迟5个cycle,Flash_ctrl模块需要返回一个hready_ctrl给AHB_slave_if,表示dout是不是有效的。读的时候,AHB发起请求之后需要5个cycle得到数据,AHB发起请求之后可以进行等待,需要将hready_ctrl拉低5个cycle之后再拉高。读的时候可能只需要几个cycle就可以读出数据。 - Flash_ctrl模块除了要返回dout之外,还需要返回一个标志操作结束的信号finish。

- 对于写操作和擦除操作,操作的时间较长。写的时间单位是微秒级的,擦除的时间单位是毫秒级的,假设对应于200M的时钟频率,时钟周期是5ns,那么写和擦除的操作都要耗费上千个周期。所以不能通过拉低hready_out的方式进行写和擦除,这样会大大降低AHB总线的效率。写和擦除往往是通过发起中断的方式进行操作。

- 如果写或这擦除操作完成之后,Flash_ctrl会发送finish信号给AHB_slave_if,AHB_slave_if接收到finish信号之后,会发送中断给中断控制器(CPU),CPU或者中断控制器之后,就可以根据中断响应程序进行响应。

1.4 读写操作详解

- 读取数据时间需要24ns,200M的时钟频率,5个cycle就可以完成读取数据。针对于读数据操作,如果Flash没有准备好读数据,可以通过拉低hready信号进行延长读数据的时间,但是延迟周期不能超过16个cycle。延迟周期越多会降低总线的利用率,因为hready拉低表示没有有效的数据传输。

对于读取操作(read access),利用AHB总线传输,解析地址,根据地址驱动Flash_ctrl,进行控制Flash。 - 写操作,Tnvs = 5us,200M时钟频率,需要1000个周期进行建立时间,所以写一笔数据耗费的时间非常的长。所以写操作和擦除操作不适合使用读操作的方式。写操作,使用中断的形式进行,配置AHB_slave_if中的一些寄存器,配置的内容主要有:配置写谁(main block or information block),配置写地址,配置写的区间,配置setup time和hold time。所以AHB_slave中存在配置中断的中断寄存器。

配置完成之后,AHB_slave_if发起一个enable信号或者start信号,写命令和数据通过cmd和cmd_payload给到Flash_ctrl,Flash_ctrl根据状态机(Flash_ctrl中的模块)按照时序图将数据写入Flash。写完之后,Flash_ctrl发送一个finish信号给到AHB_slave_if。AHB_slave_if拿到finish信号之后,可能进行额外的判断,比如判断是否开启了中断屏蔽,中断屏蔽开启,AHB_slave_if就不发出中断,如果中断屏蔽关闭,就发出中断。如果发出中断,CPU通过中断服务程序对中断响应,CPU进行下一步操作,此时中断是一直拉高的。如果要CPU需要写寄存器,将中断清除。

3、擦除操作和写操作的执行差不多,都需要进行配置寄存器,配置擦除的地址,页数等。

1.5 寄存器的配置

AHB_slave_if中需要实现一些寄存器

1、config寄存器,其中包括地址,setup时间和hold时间。

2、中断使能寄存器(int_en),将中断开关打开,finish来了之后需要中断打开,让中断能够发出。

3、状态寄存器(status),记录当前是哪个操作完成了。当前如果处于boot模式下,需要进行读写的保护,在boot期间,对于boot区间写擦的操作,就用寄存器将这个错误状态进行记录。后续如果发起中断给CPU,CPU会发现非法操作进行,进入中断服务程序进行排查。

1.6 Flash_ctrl中有一个状态机和计数器

2.eFlash架构设计文档