转载请标明出处:https://www.cnblogs.com/leedsgarden/p/17790320.html

本文介绍的是Quartus的免费版,可以满足基本的教学需要

如果你用的是Xilinx的话,这篇文章不适合你。本文适用于Altera用户

下载安装

在 Lite Edition 一栏,选择你的发行版,点击下载。

(下载可能比较慢,有条件可以挂代理)

下载后解压,双击Setup安装。

基本默认选项即可,会把帮助菜单和器件库全部安装完成。

联合ModelSim仿真

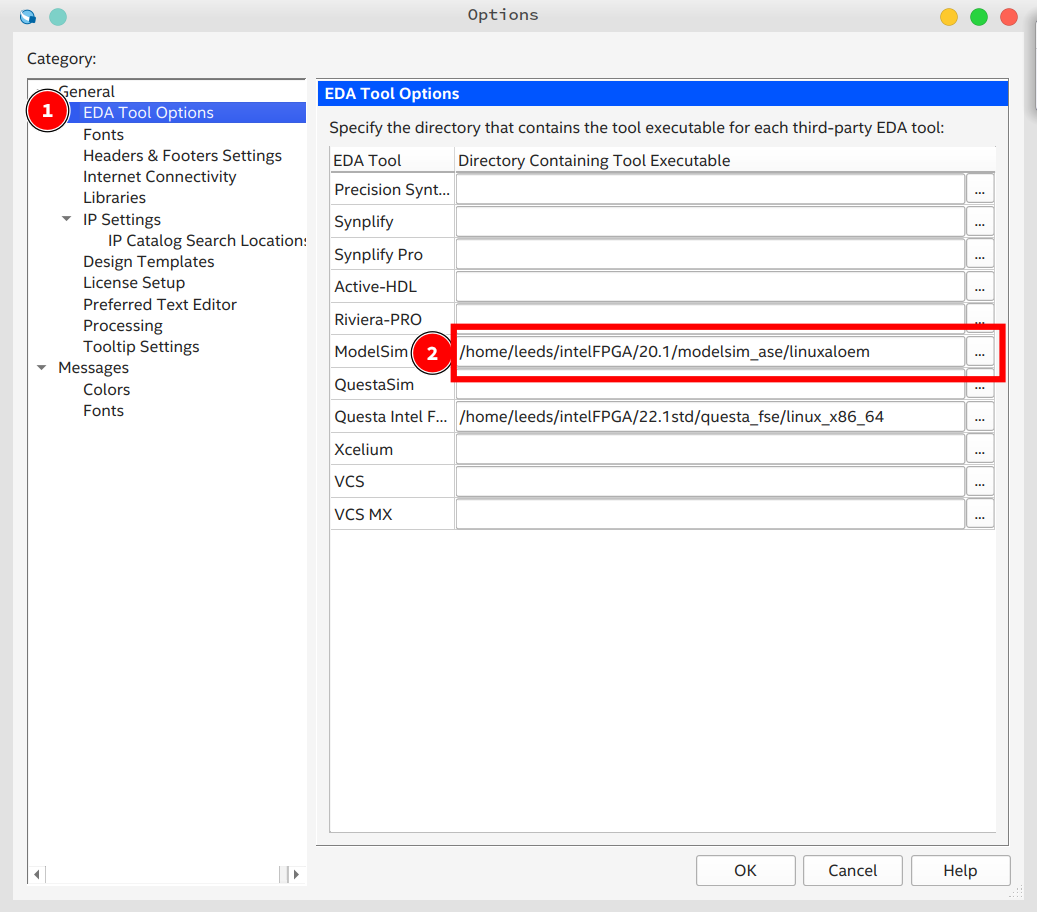

安装完成后,打开 Quartus,在Tools->Options...打开,设置路径,最后点击OK。

示例

# windows

C:\\intelFPGA\20.1\modelsim_ase\win32aloem # 默认

# Linux

~/intelFPGA/20.1/modelsim_ase/linuxaloem # 默认

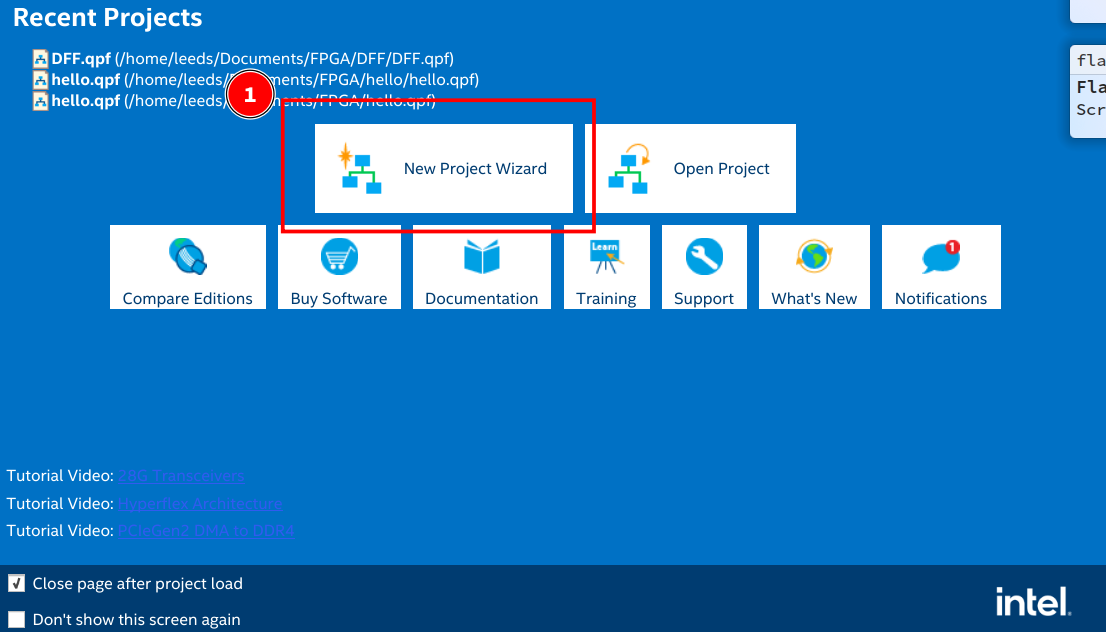

创建工程项目

第一步

或者

File->New Project Wizard

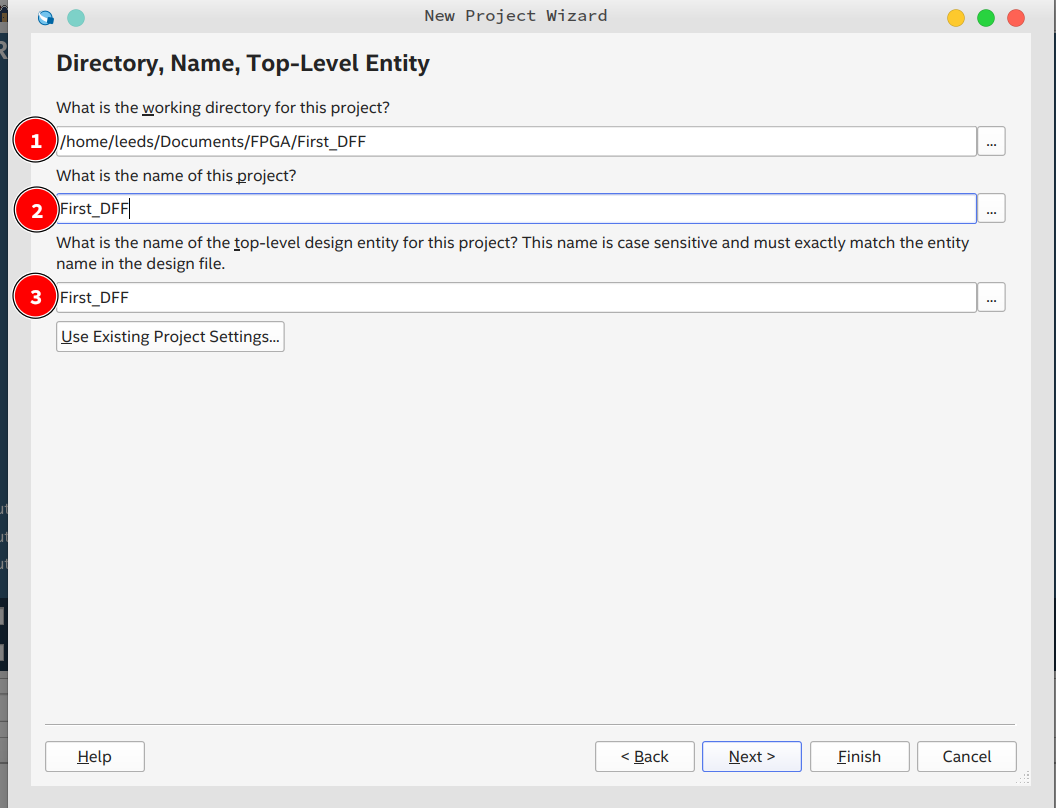

第二步

选择路径加上项目名,在第二栏输入项目名,第三栏会自动补上。

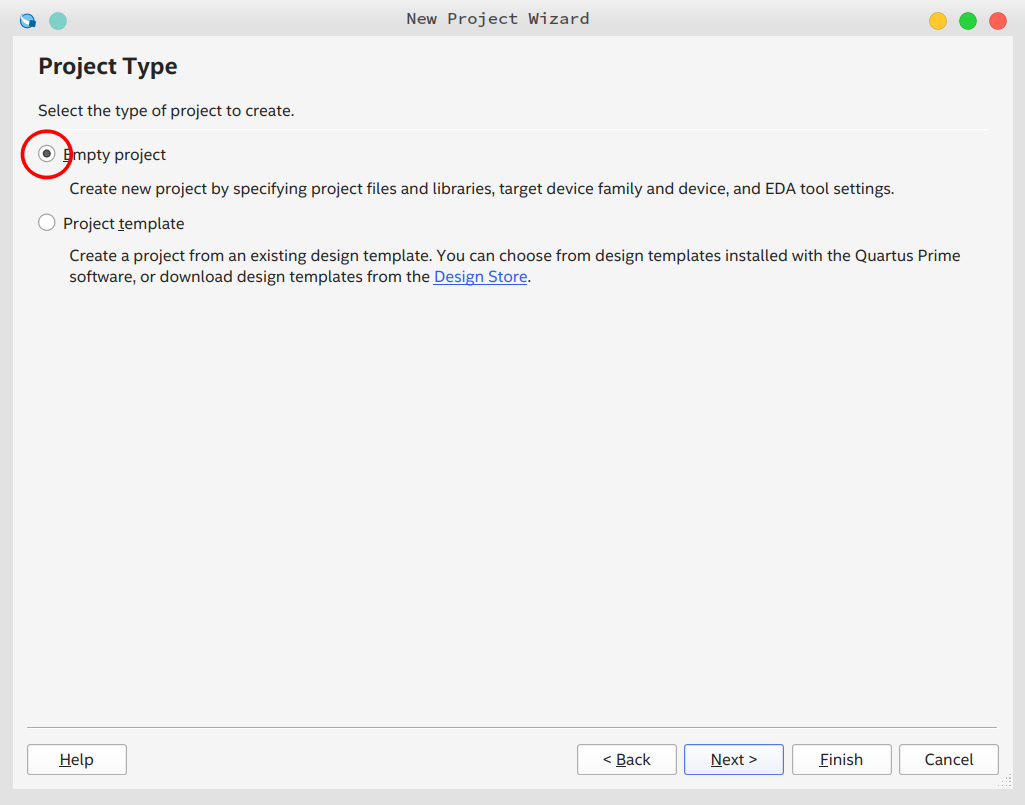

第三步

选择空项目可

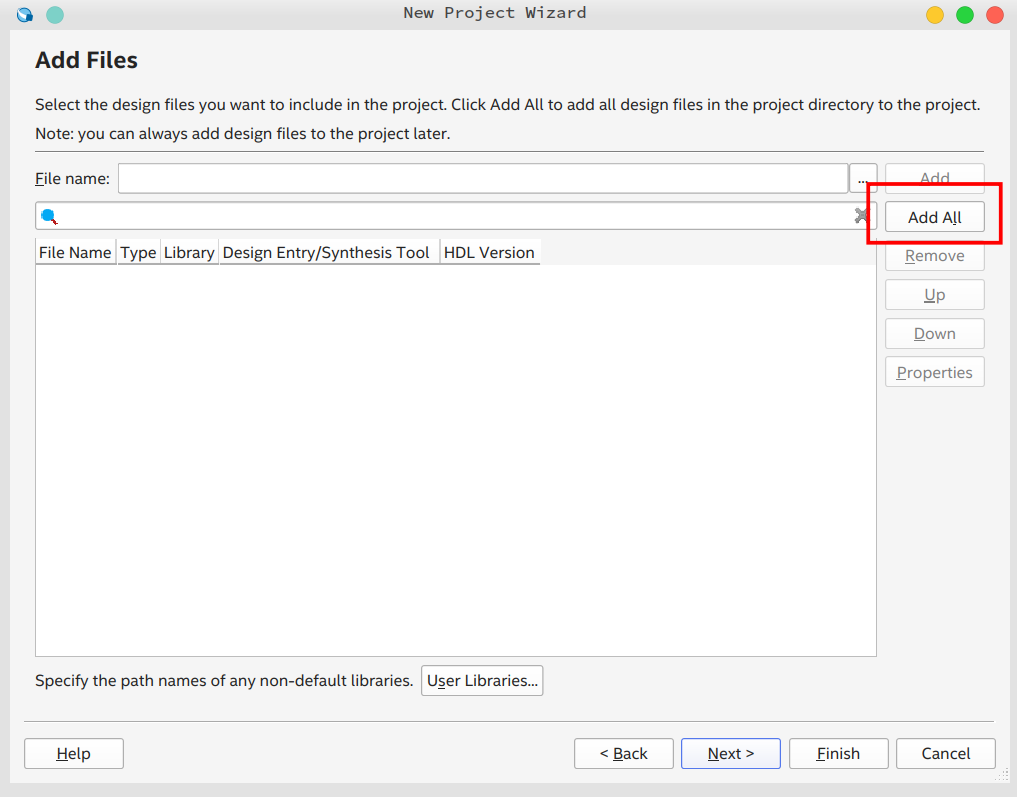

第四步

如果有文件,Add添加即可,我们这里跳过

第五步

这里按照器件选择,示例为 Cyclone IV E EP4CE6F17C8L。

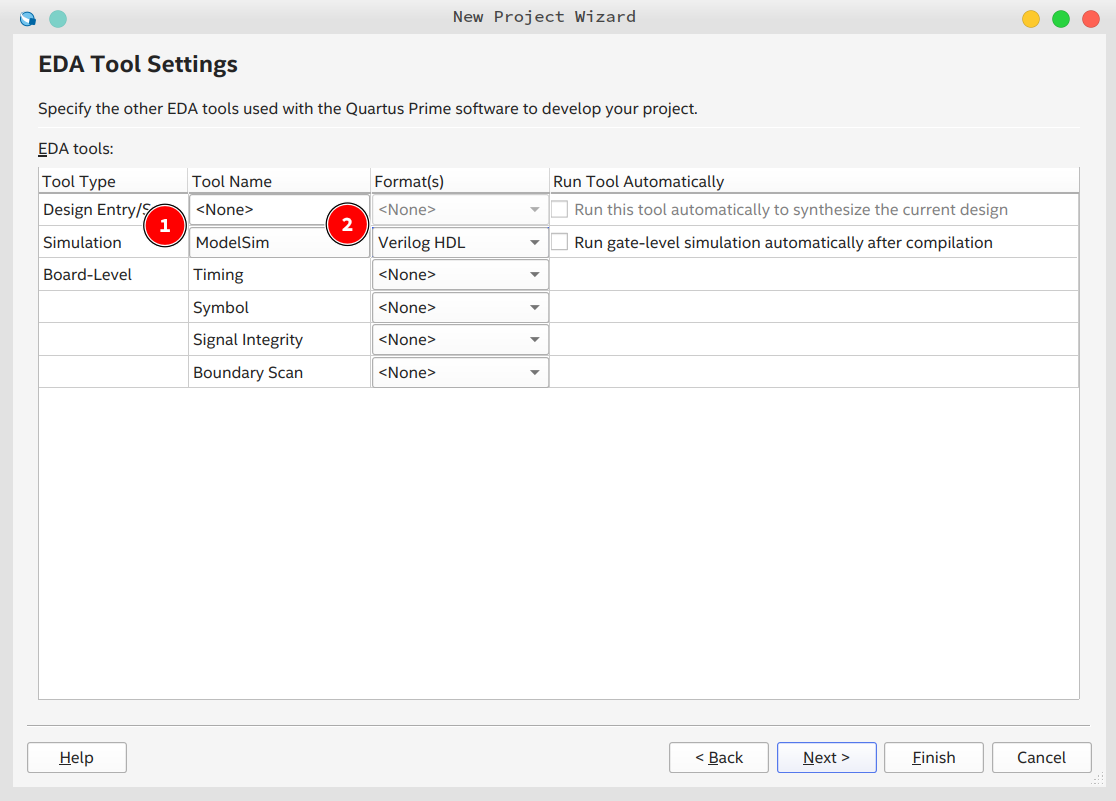

第六步

按照示例把1更改为ModelSim,2更改为Verilog HDL。

第七步

再次确认信息是否正确,点击Finish。

添加 verilog 文件

File->New...

输入模块代码,然后用同样的方式创建testbench。

// First_DFF.v

module First_DFF(D, CLK, Q);

input D, CLK;

output Q;

reg Q;

always @(posedge CLK)

begin

Q <= D;

end

endmodule

// First_DFF_tb.v

`timescale 1ns / 10ps

module First_DFF_tb;

reg clk;

reg D;

wire Q;

First_DFF DFF(

.CLK(clk),

.D(D),

.Q(Q)

);

always #10 clk = ~clk;

initial begin

clk = 1'b0;

D = 1'b0;

#20 D = 1'b1;

#20 D = 1'b0;

#20 D = 1'b1;

#20 $stop;

end

endmodule

编译并通过

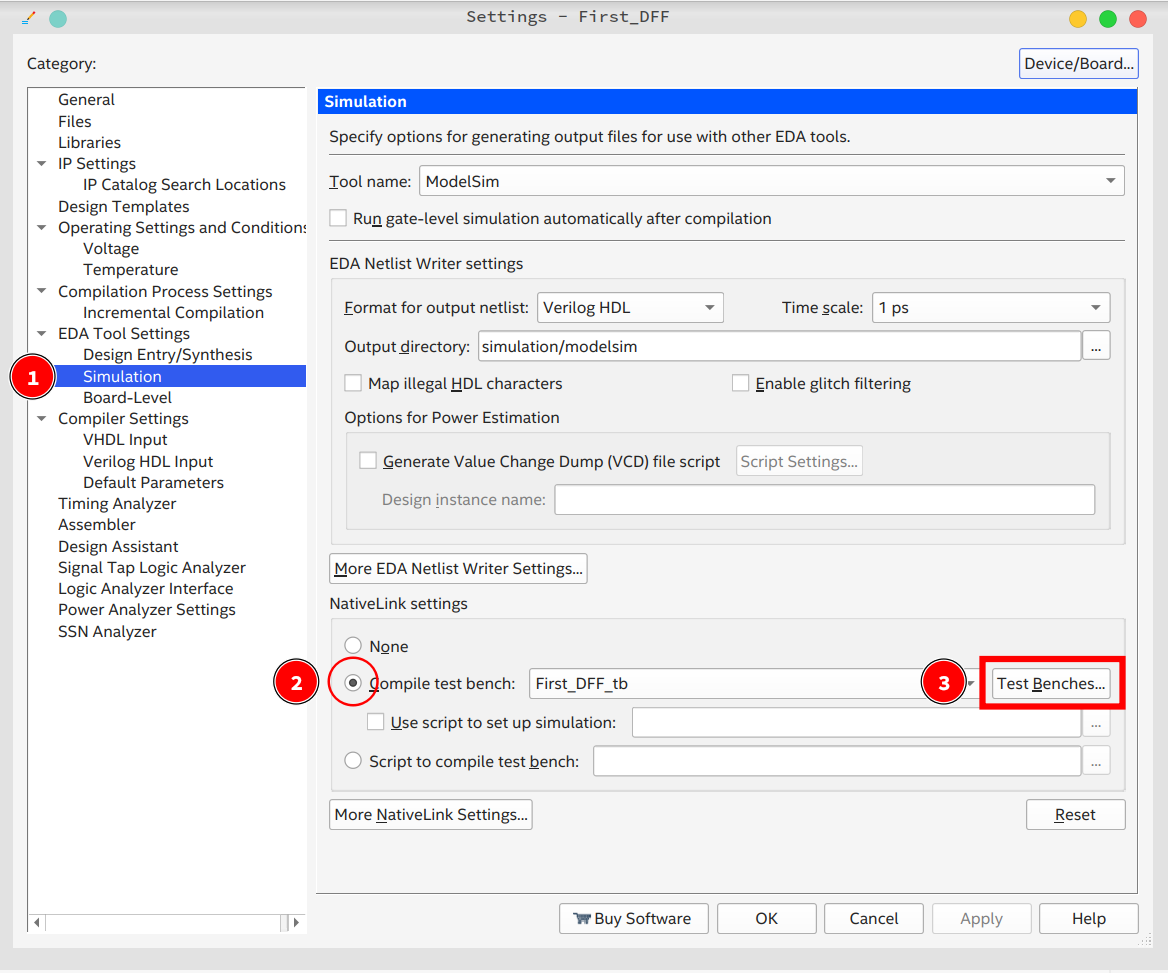

选择 testbench

Assignment->Setting...

勾选2,点击 testbench

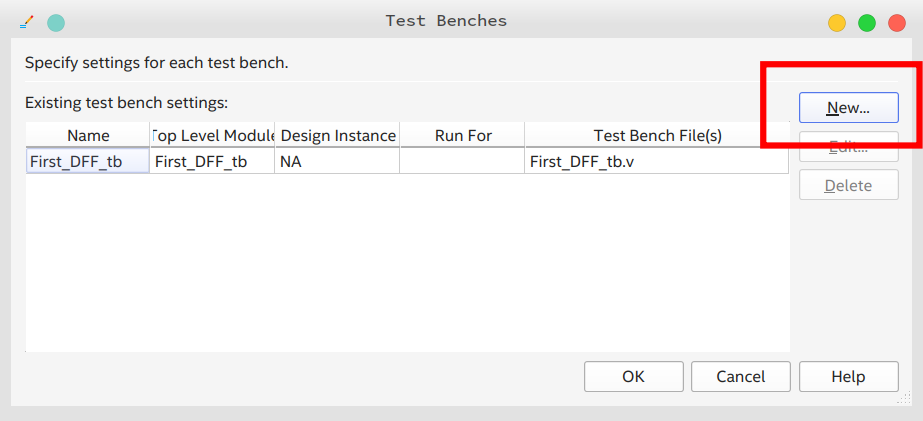

点击New。(表格空白不要慌,我的是已经添加好了的)

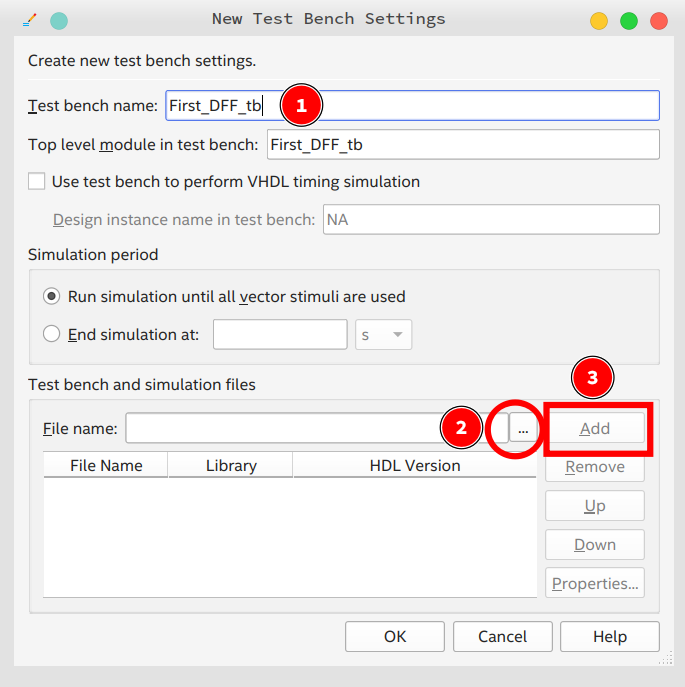

在1输入testbench文件名,2中选择文件,点击Add添加即可。

然后一路 OK 回到主界面。

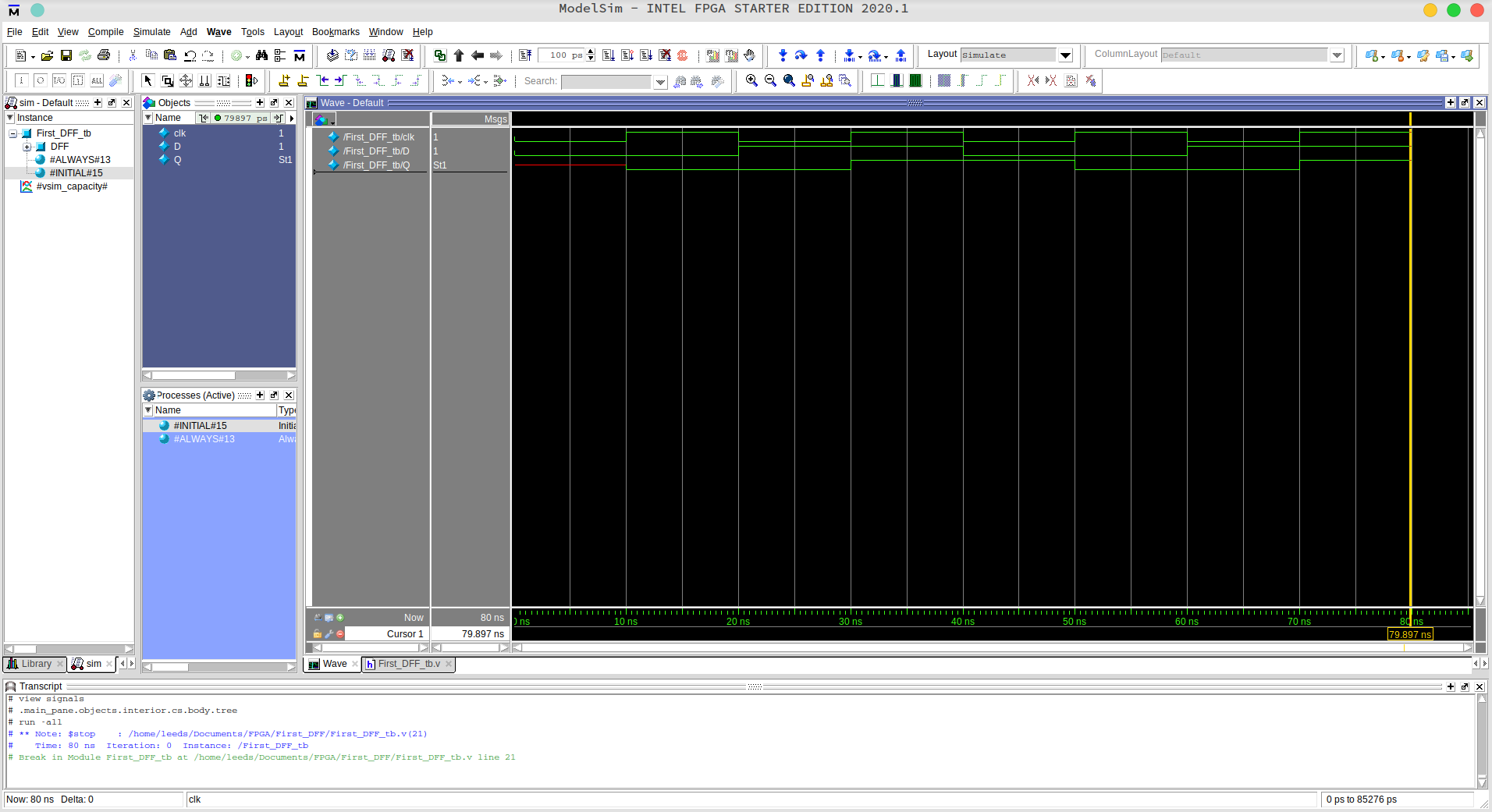

ModelSim 模拟

Tools->Run Simulation Tool->RTL Simulation

弹出 ModelSim 就算成功。