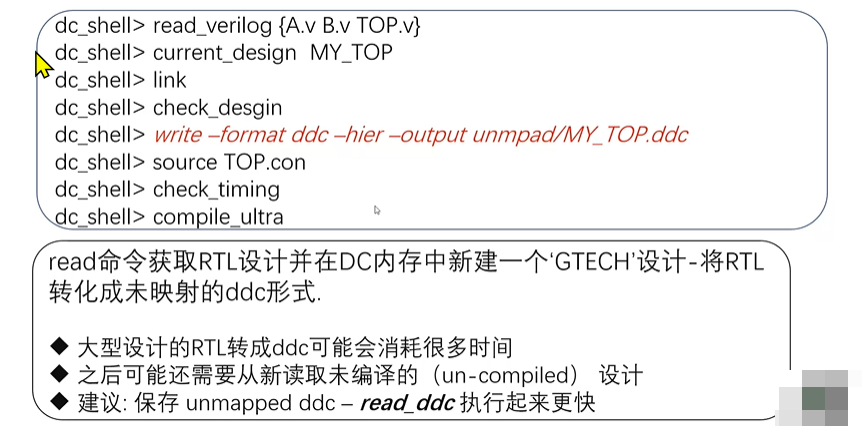

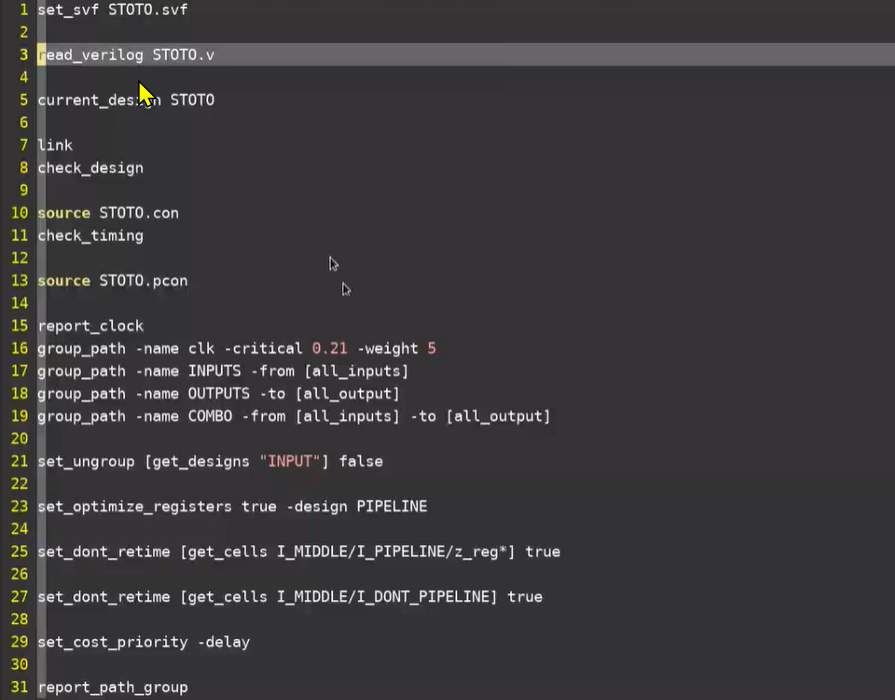

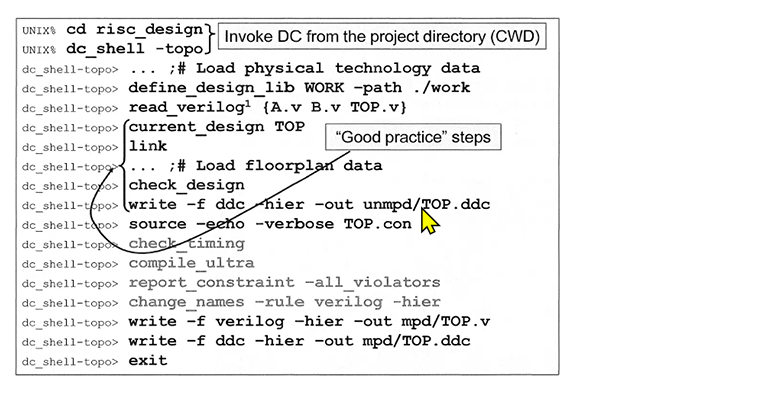

在 compile之前保存ddc设计文件

- check design - 检查文件的连接性和物理性

- check design之后可以将未映射的网表写出,如果是几十万级的RTL,如果不写出,设置约束出现问题,更改之后,前面的流程需要重新进行,花费时间

- check design之后写出未映射的网表,再读入约束,方便进行调整约束,可以直接读入ddc文件,节省时间

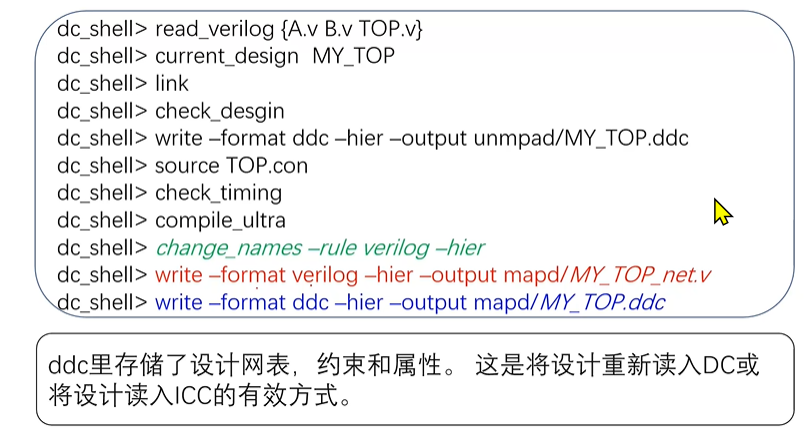

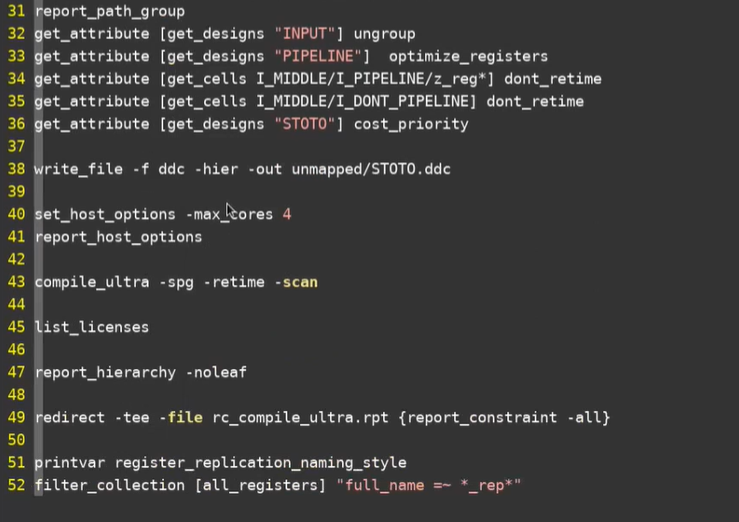

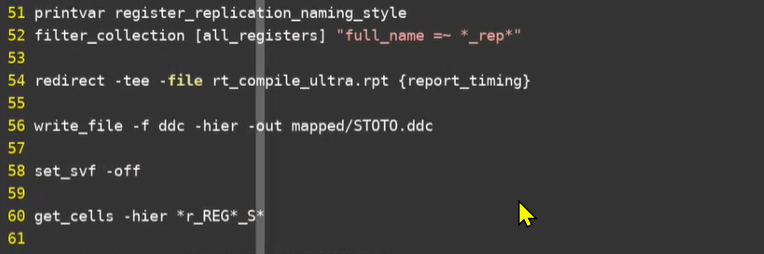

在compile之后保存ddc

- ddc - 二进制文件,存储网表,约束,属性

测试

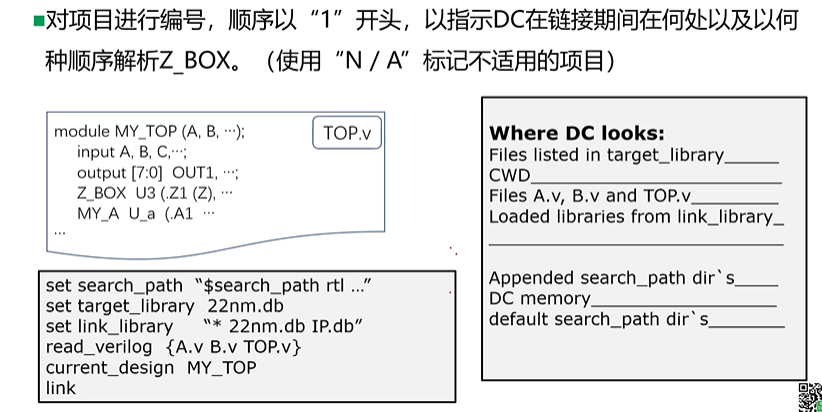

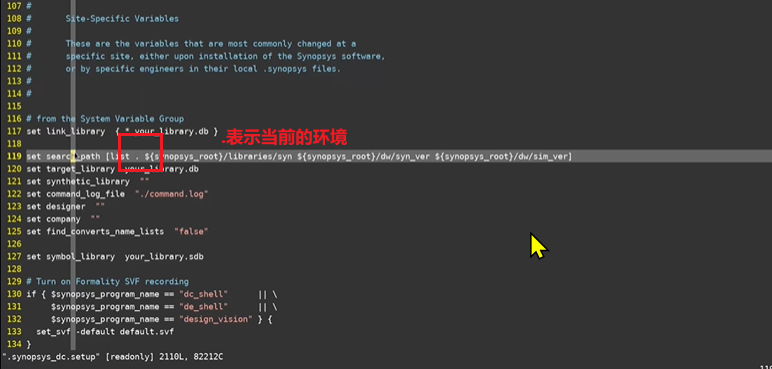

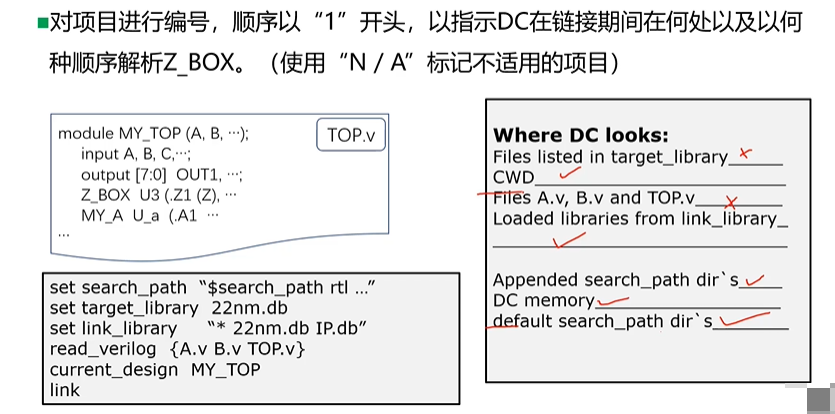

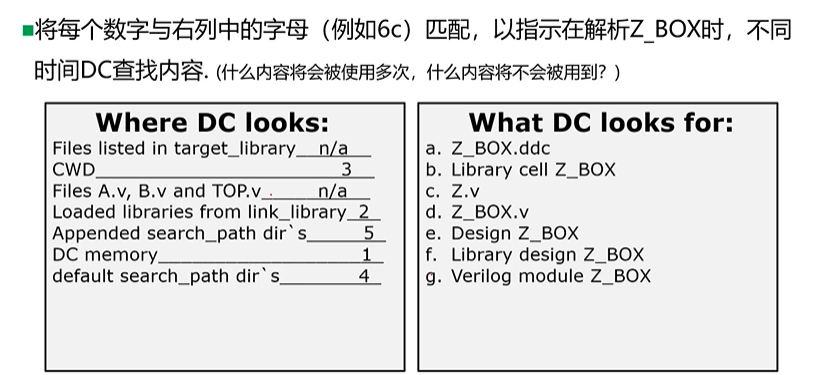

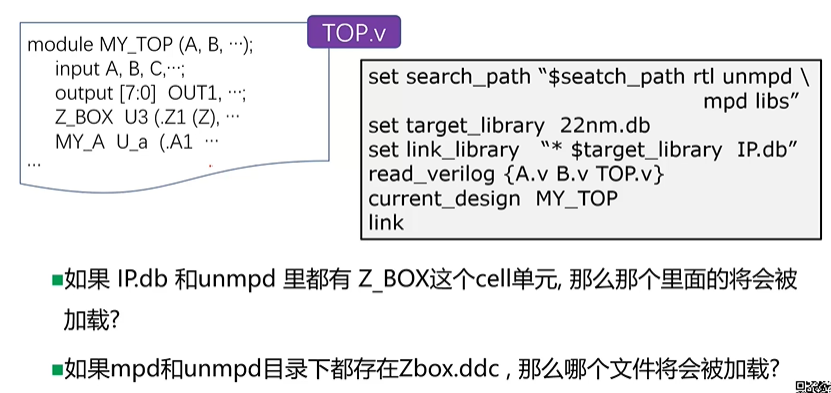

- 链接期间不会找目标库,目标库是在映射期间进行查找的

- CWD - 当前项目的路径(包含rtl,cons...),也是当前的dc启动的路径,link的时候会查找

- link libraries - 会解析

- search path - 会解析

- DC memory - dc内存

- 在进行link之前需要读入rtl,read_verilog命令作用:读入GTECH网表,读入RTL将其转换为未映射的网表;将RTL添加到DC内存;加载link库

- 查找顺序:DC memory --> .db

- 查找不到,ddc会自动加载

- ddc文件可以自动进行添加,添加的路径搜素顺序:search path中的顺序:CWD-->default search path --> appended search path

- z_box是ddc形式的,那么会在search path找

- lib cell z_box是库文件 - 在link library找

- z_box.v - read_verilog读入,在dc memory中进行寻找

- design z_box - 已经加载到dc内存中的z_box文件

- library design z_box - link library中进行寻找

- DC memory --> link_library --> search path,使用IP.db中的z_box

- .ddc文件自动加载,文件名必须和RTL中一致

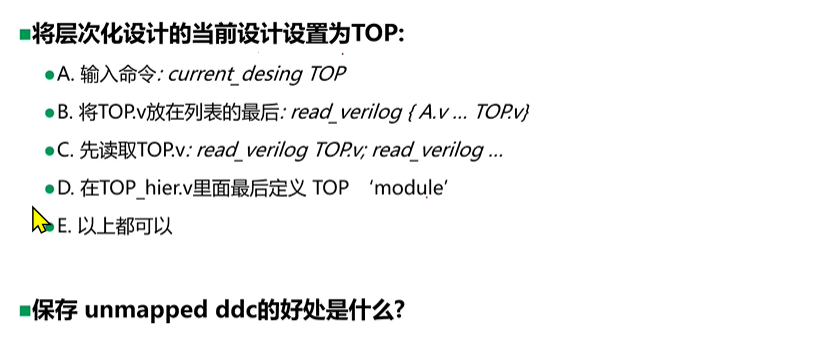

- B选型 - 使用文件列表,默认第一个作为current_design

- C - 依次读取design - 默认最后一个作为current_design

- D - 所有design在一个文件中,第一个module作用current design

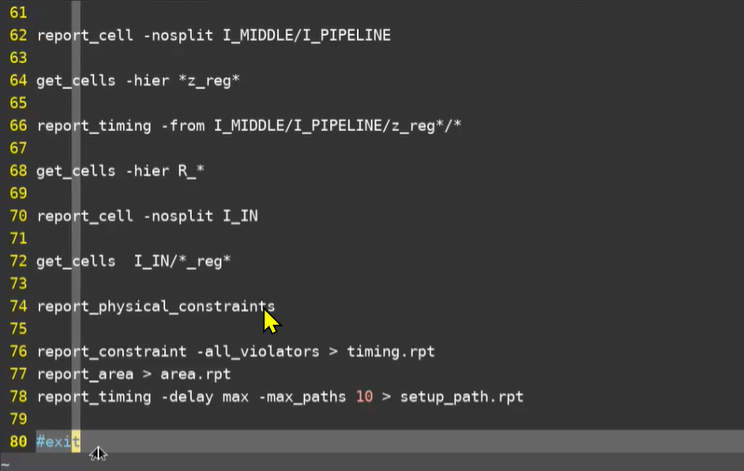

- 保留unmapped ddc文件方便修改时序后的约束

- ddc文件 - 包含网表和约束

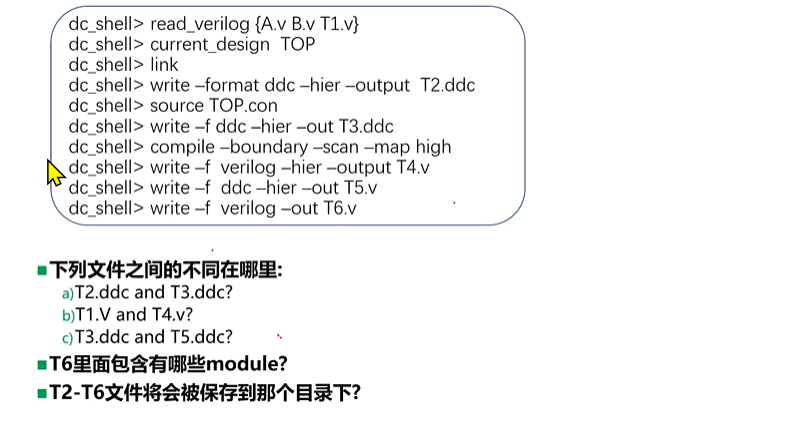

- T2不含约束,T3包含约束

- T1是未综合的RTL,T4是综合之后的网表

- T3是未映射的网表,T5是映射的网表

- T6中保存的module,就是current design,top

- -hier:加这个选项,会保留设计层级

- 保存在当前路径下

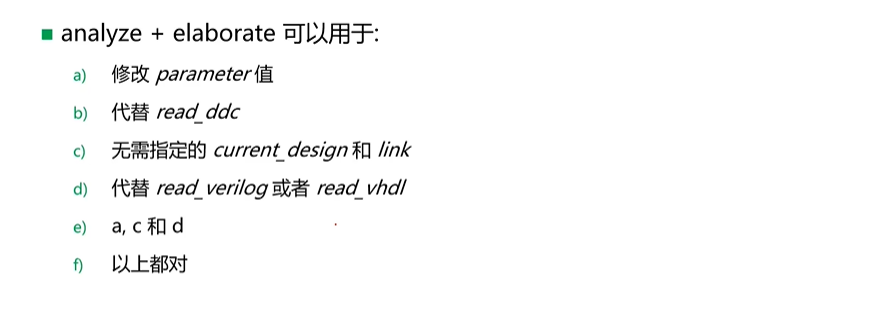

- 可以修改parameter值

- analyze+elaborate - 不能读取ddc

- a,c,d

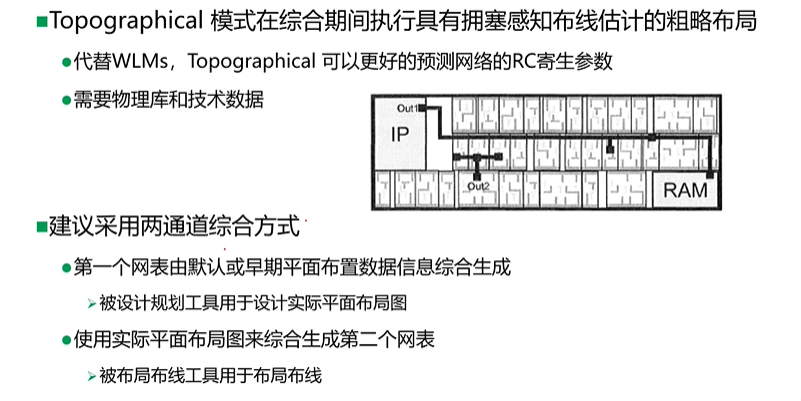

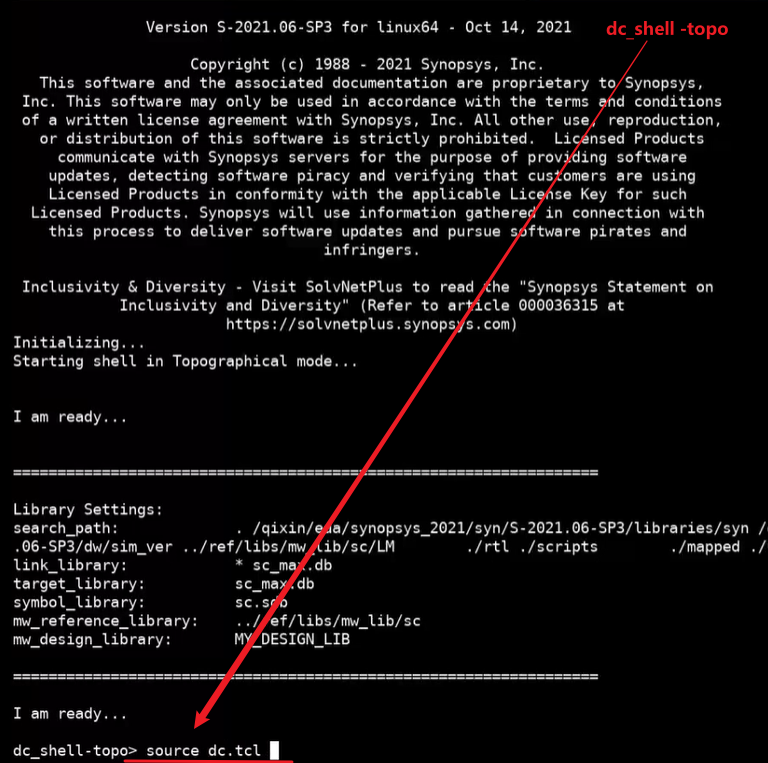

使用拓扑模式进行综合

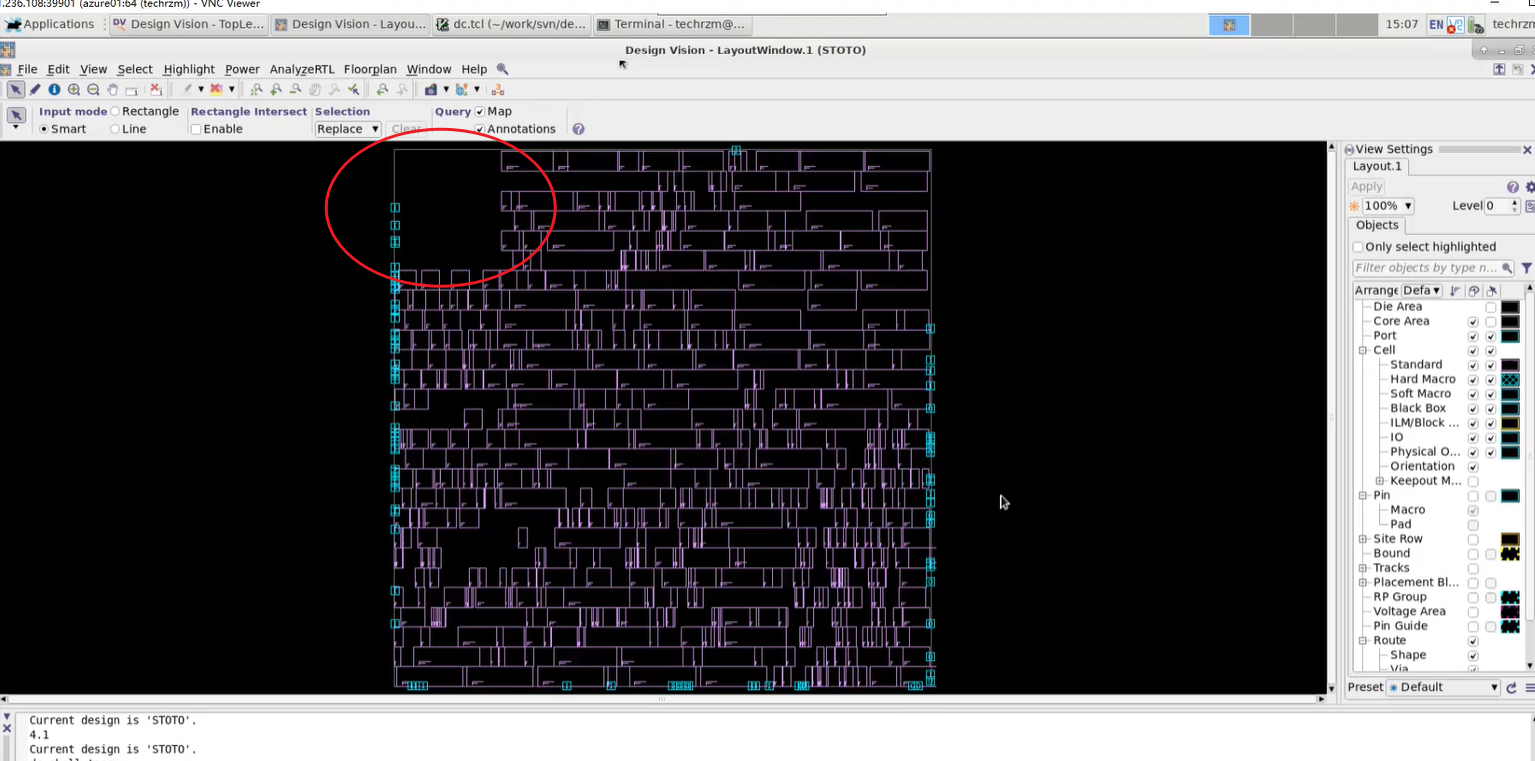

- out1和out2都是有三个扇出,使用WLM模式进行综合,得到的RC可能是一样的,但是实际上是不一样的,所以考虑使用拓扑模式进行综合

- WLM综合 --> ICC布局布线 --> 物理信息 --> 拓扑模式综合

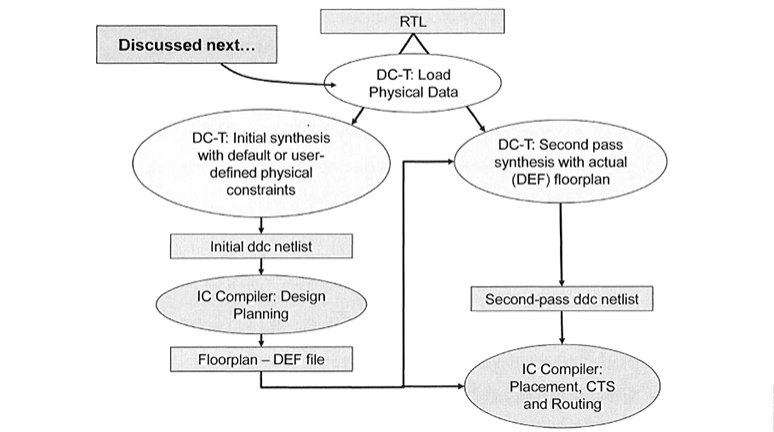

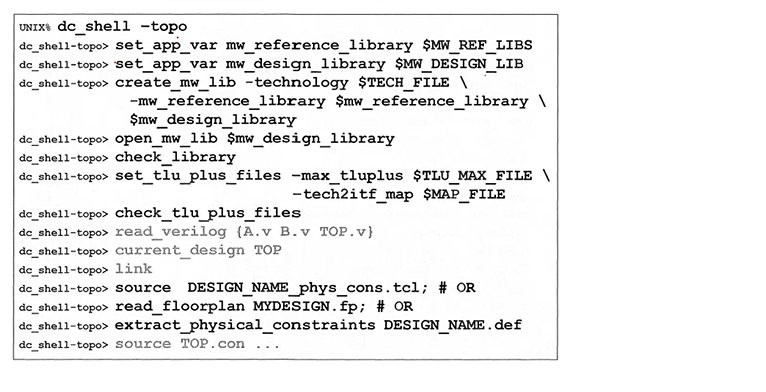

双通道topo模式综合流程

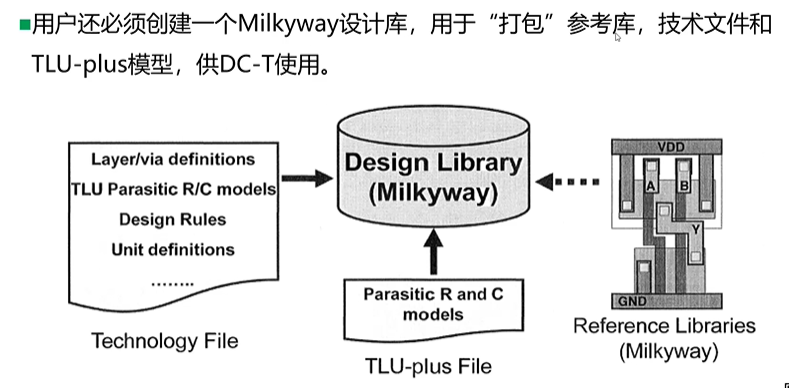

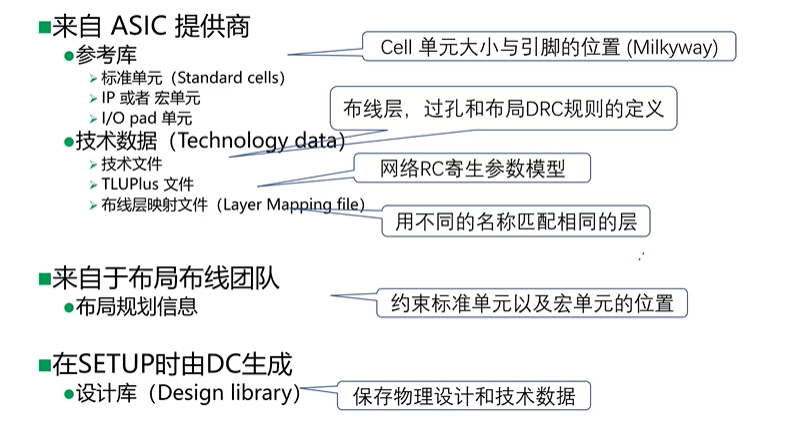

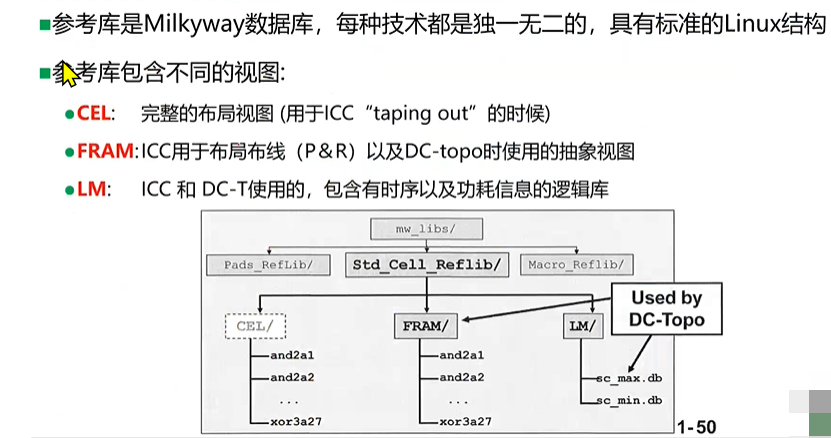

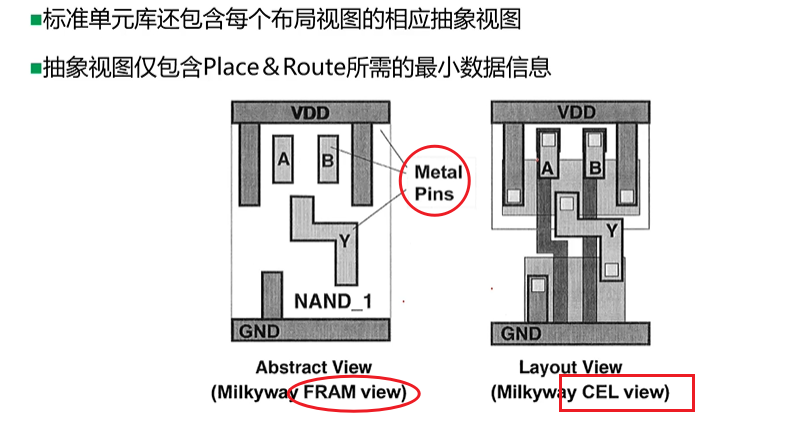

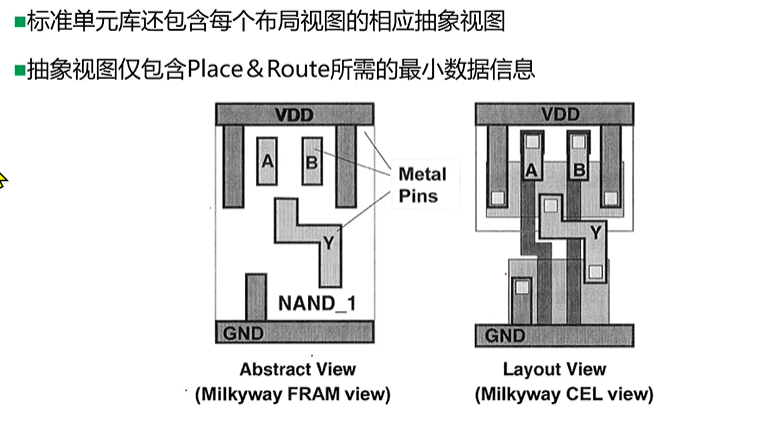

Milkyway参考库

- WLM模式下的模型 - LM

- CEl - cell库,包含所有standcell的形状及引脚的位置,包含全部信息及内部引脚的互联

- FRAM - CEL的简化,指包含引脚的位置

布局视图和抽象视图

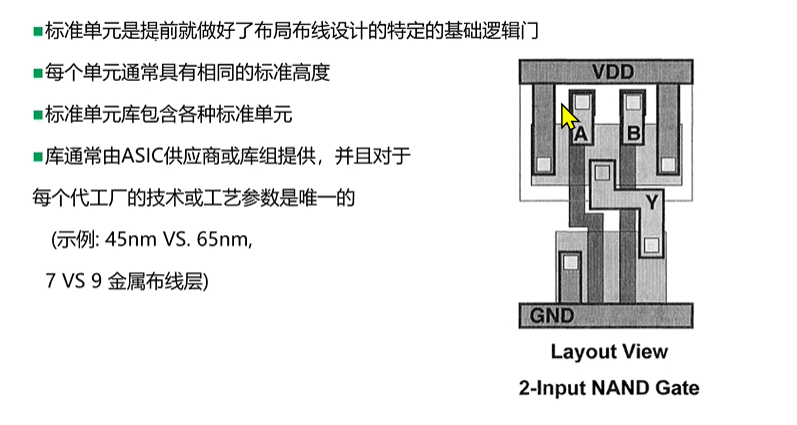

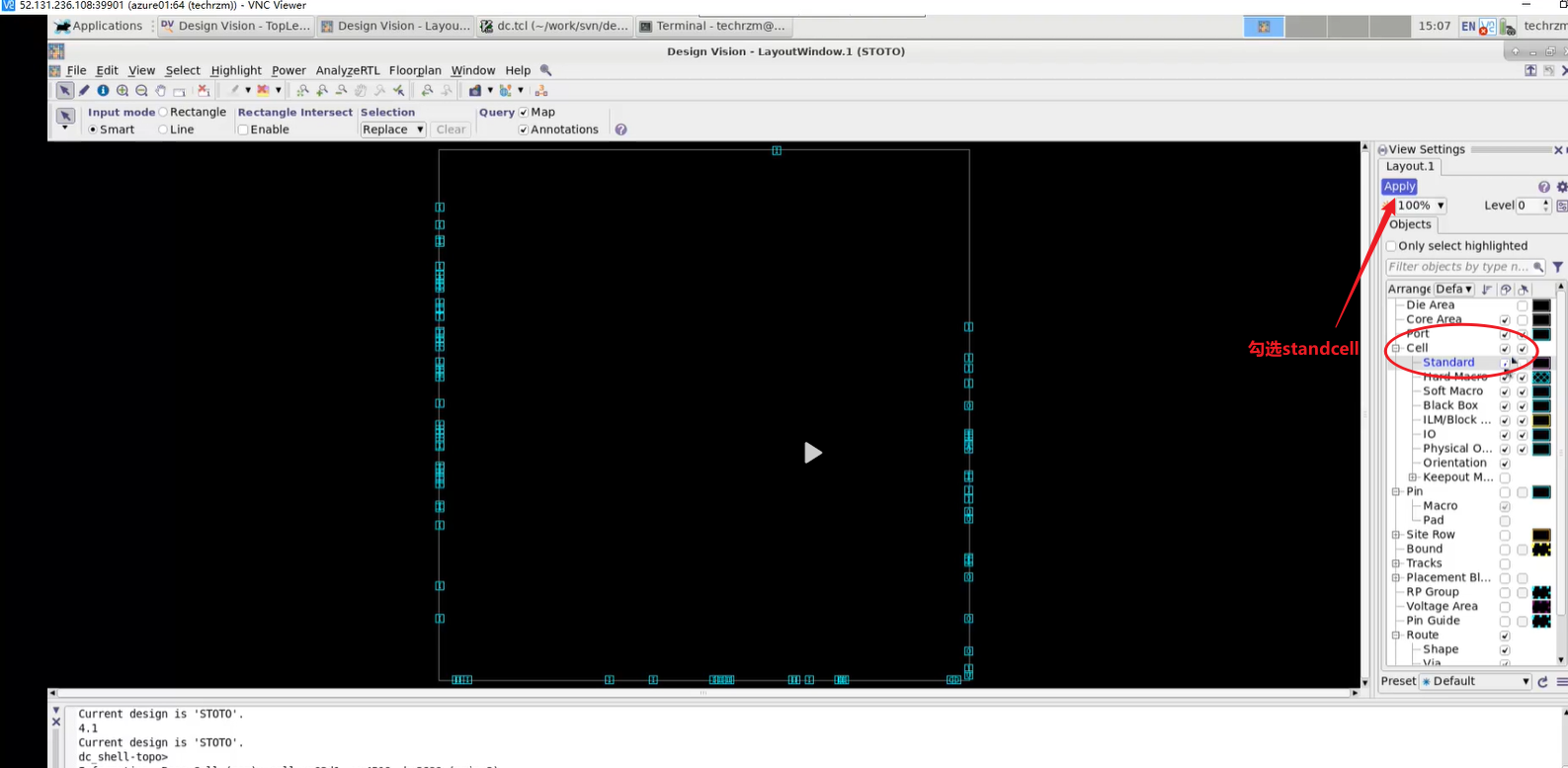

什么是标准单元库

- standcell - 是全定制的设计,其中N well和P Well都是设计好的

- standcell - 有固定的高度,方便布局布线;上层是VDD,下层是GND

- 工艺确定之后,标准单元库就确定了

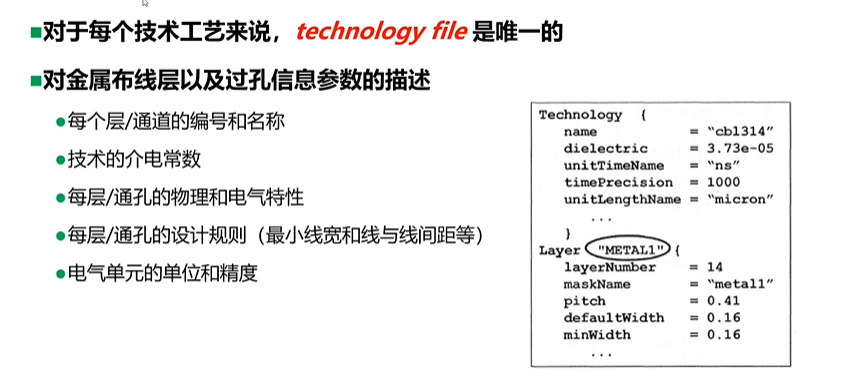

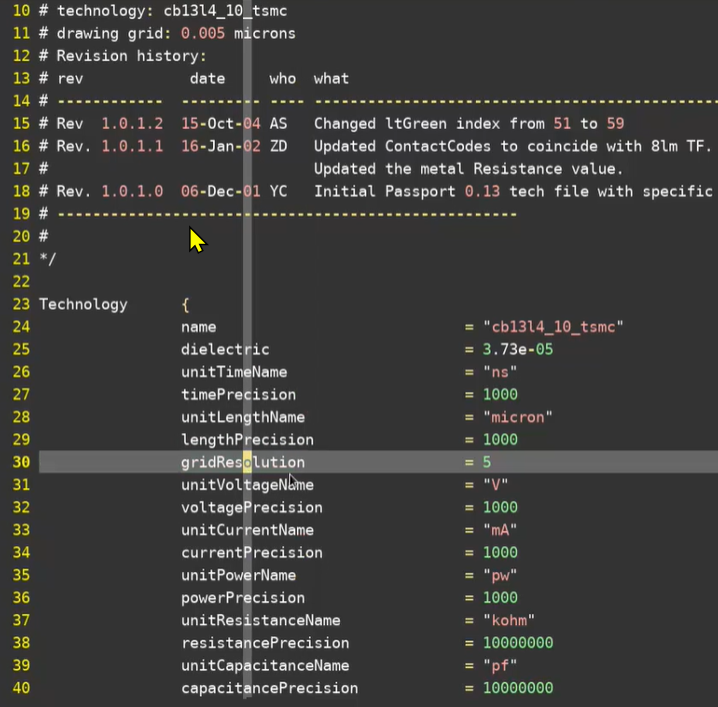

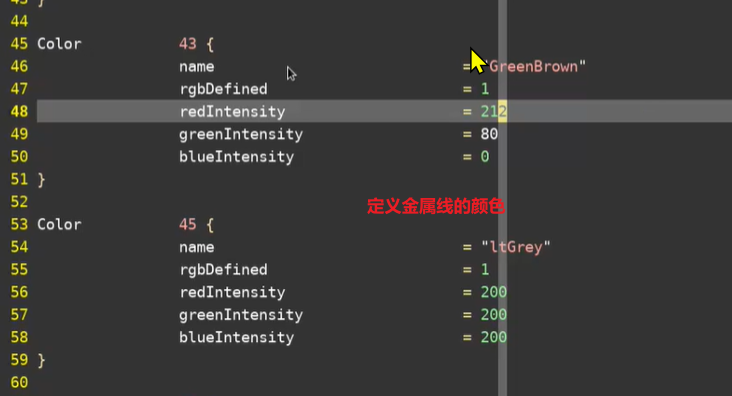

技术文件(Technology File)(.tf file)

- 走线越靠近上方,走线越宽

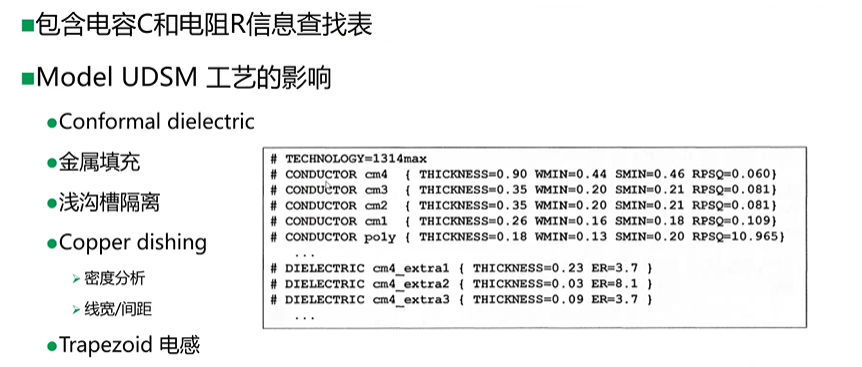

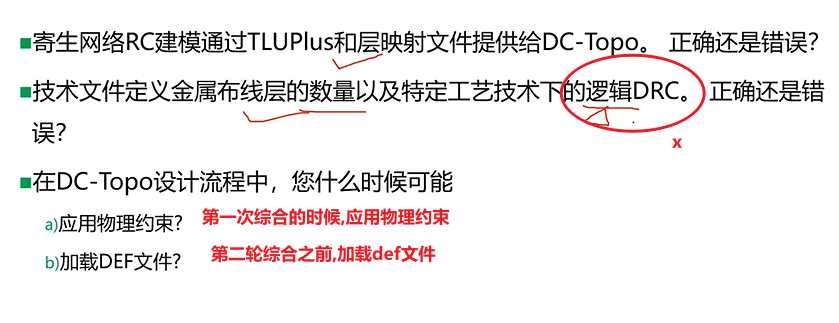

TLUPlus files

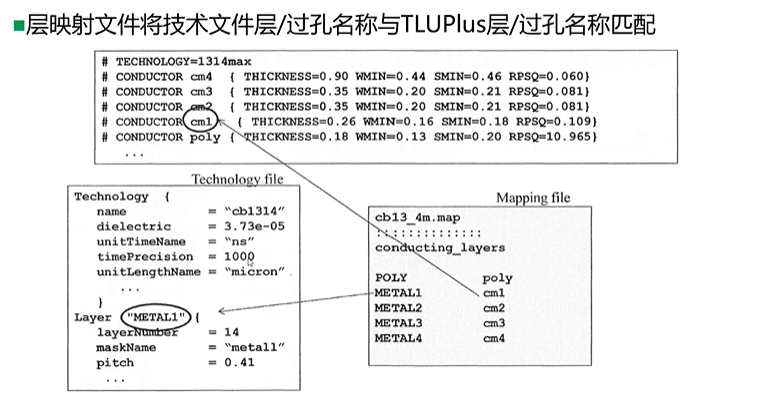

层映射文件(Layer mapping file)

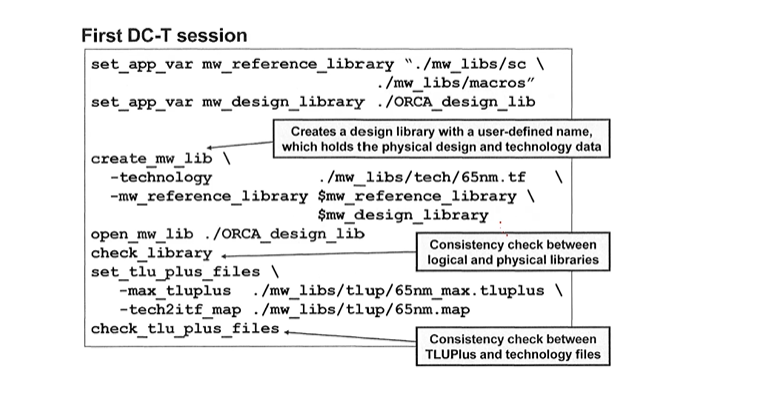

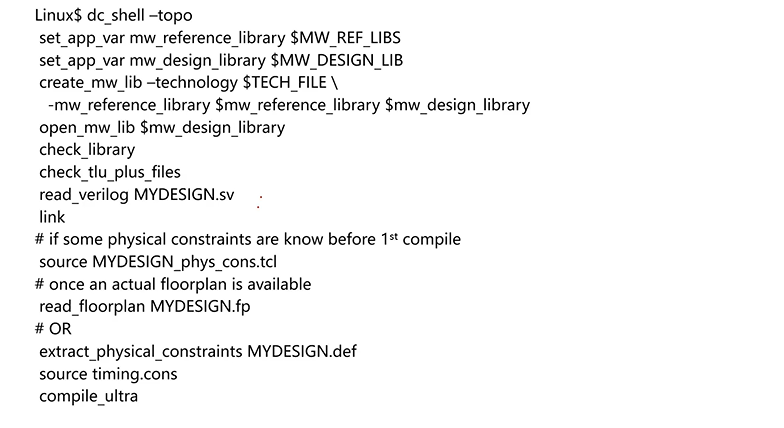

首次加载物理技术数据

- mw_reference_library - 设置milkyway library

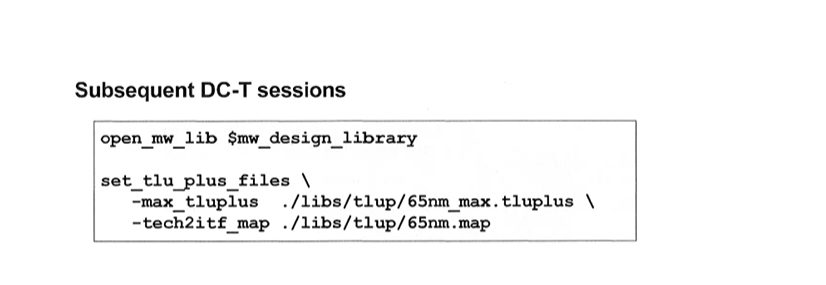

重新加载现有的设计

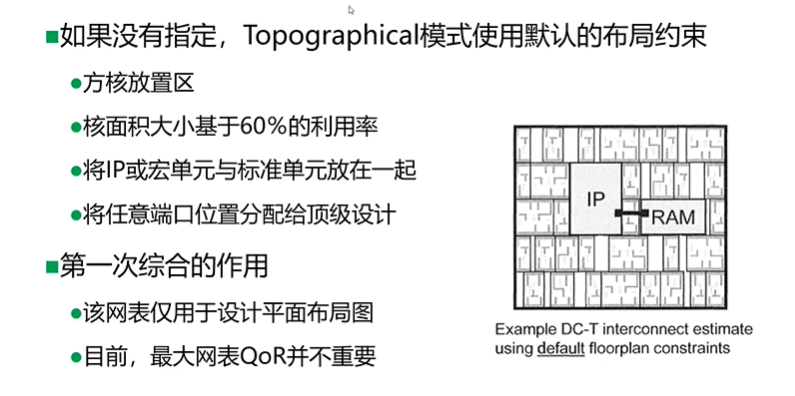

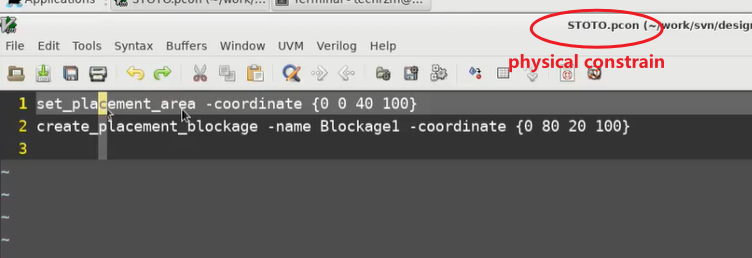

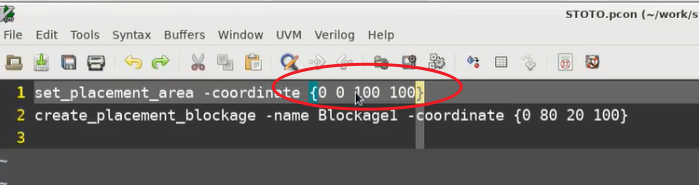

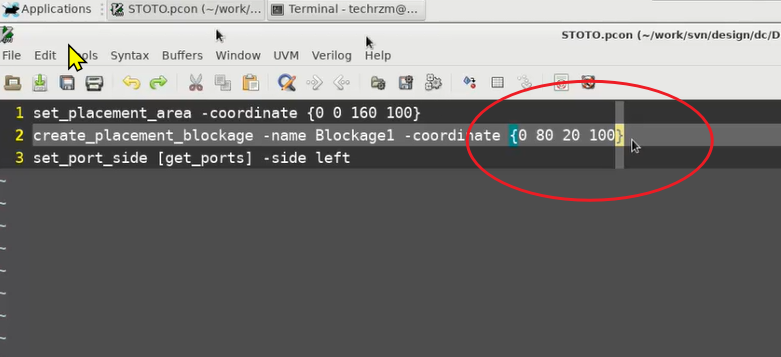

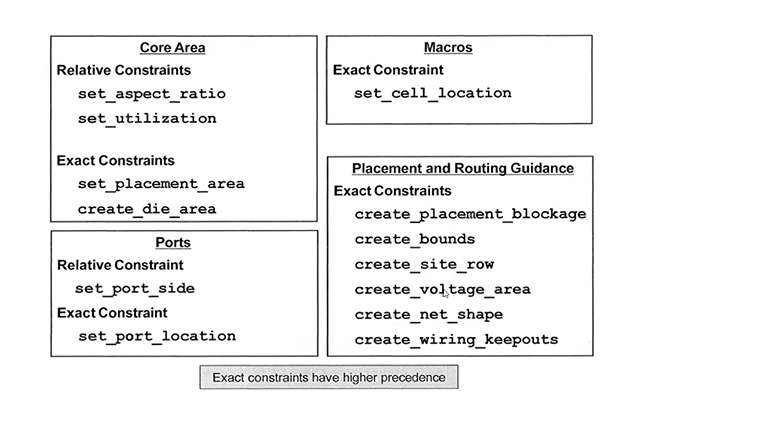

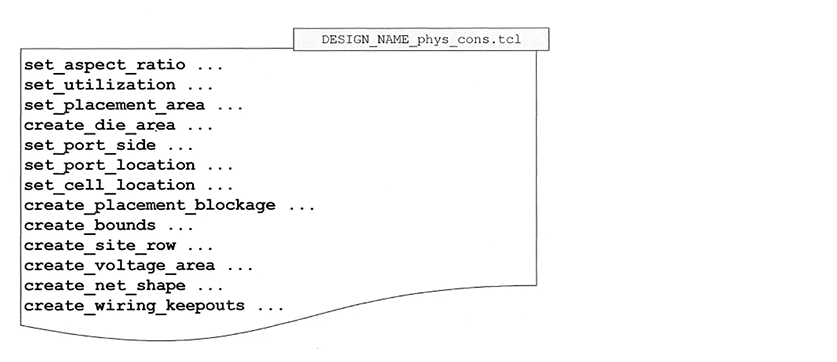

默认的布局约束 - 第一次综合

- 方核放置区 - 长宽一致

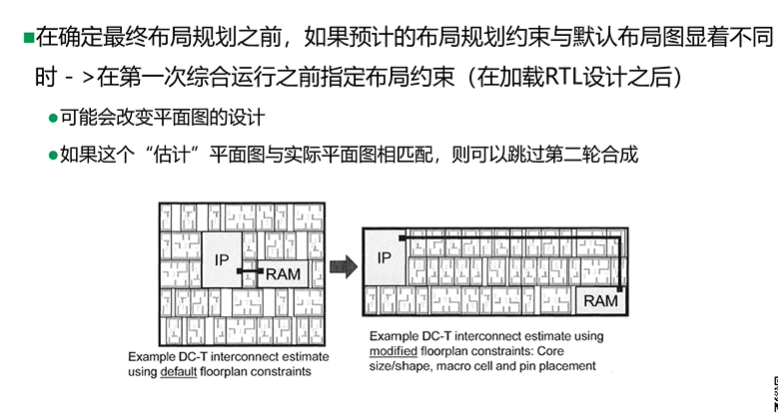

修改布局(FP)约束 - 第一次综合

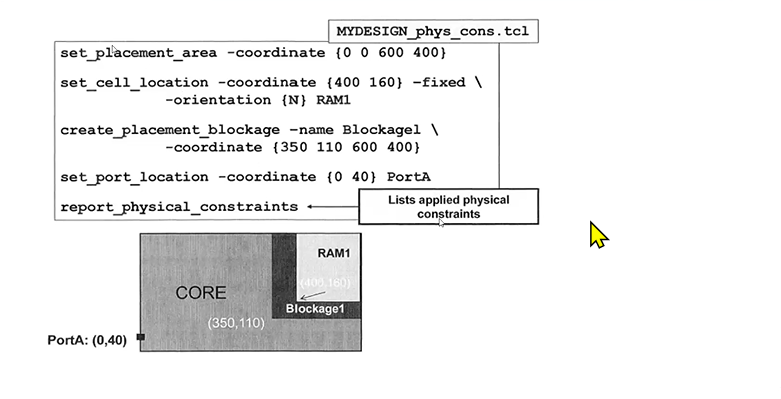

- 可以对于IP和RAM的位置进行指定

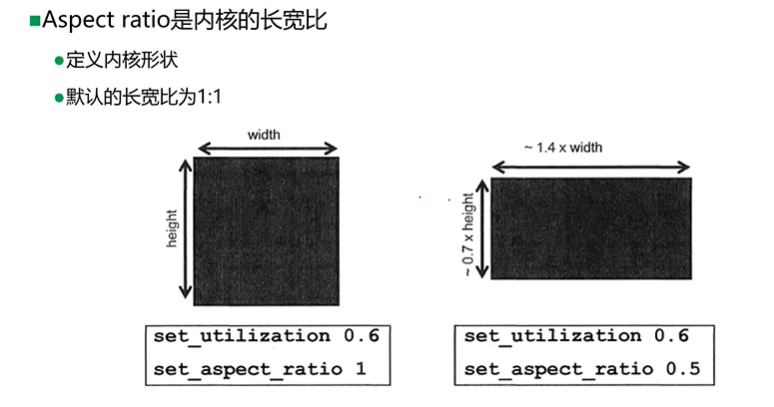

定义相对核心形状:Aspect ratio

- Aspect ratio - 长/宽

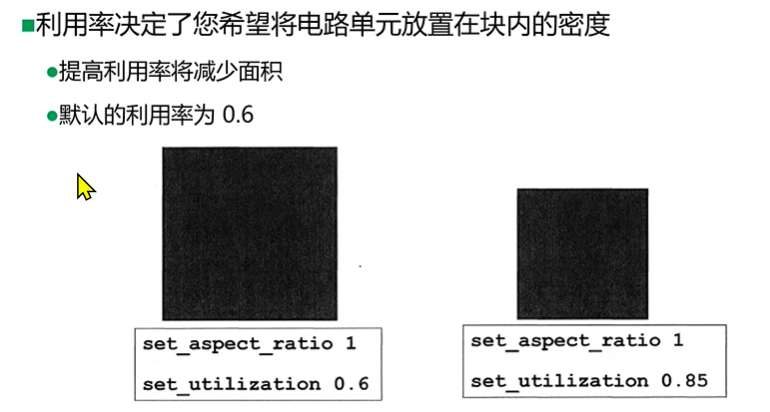

定义相对核(relative core)的大小:利用率

- 利用率越高,拥塞程度会增加

- total area = cell area/utilization(利用率),利用率越高,total area越小

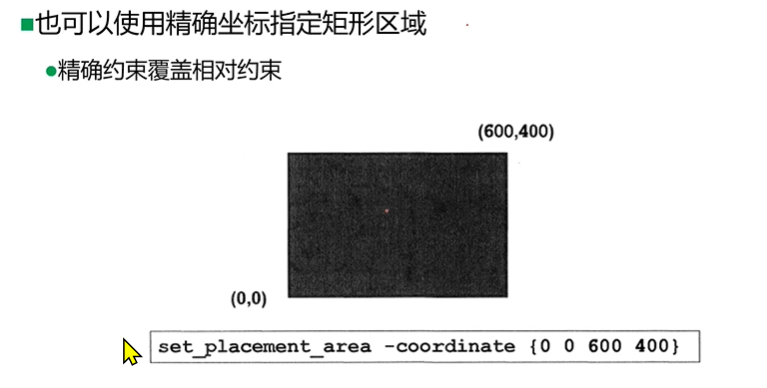

定义精确的矩形区域

- 指定左下角坐标和右上角坐标,比较适合于设计大的SoC

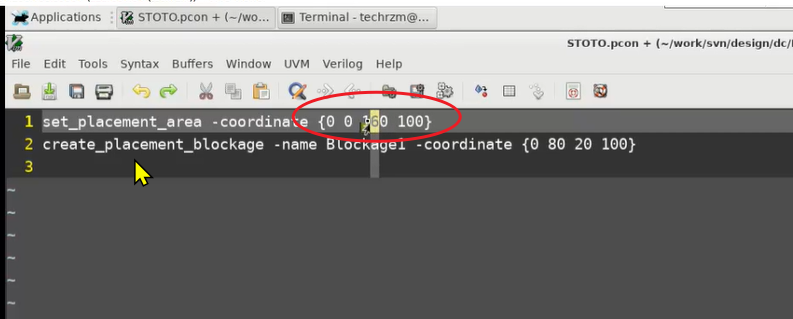

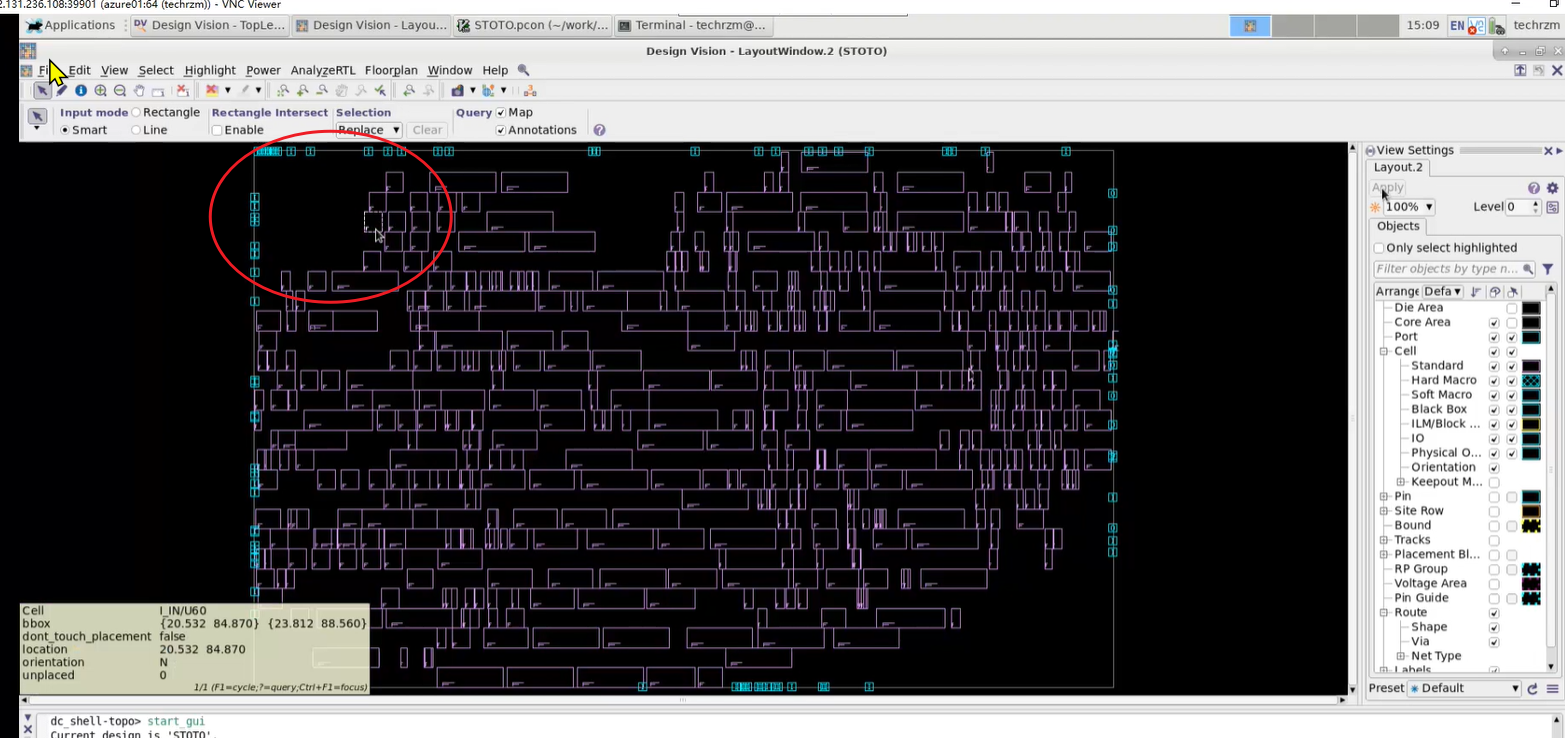

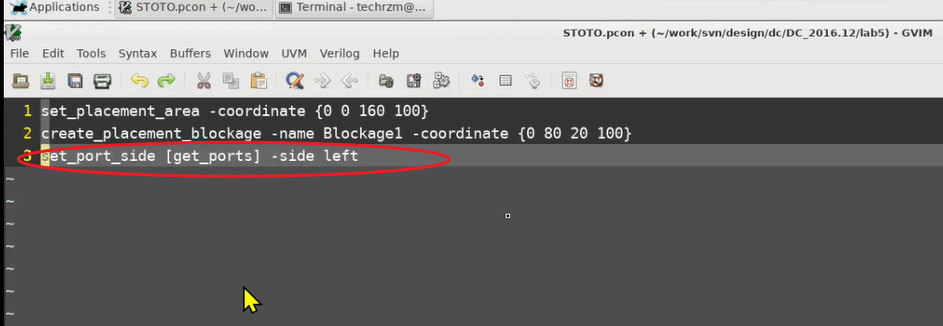

实例

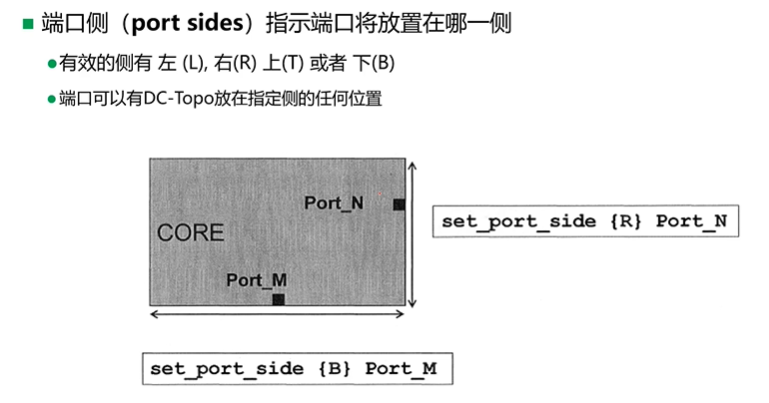

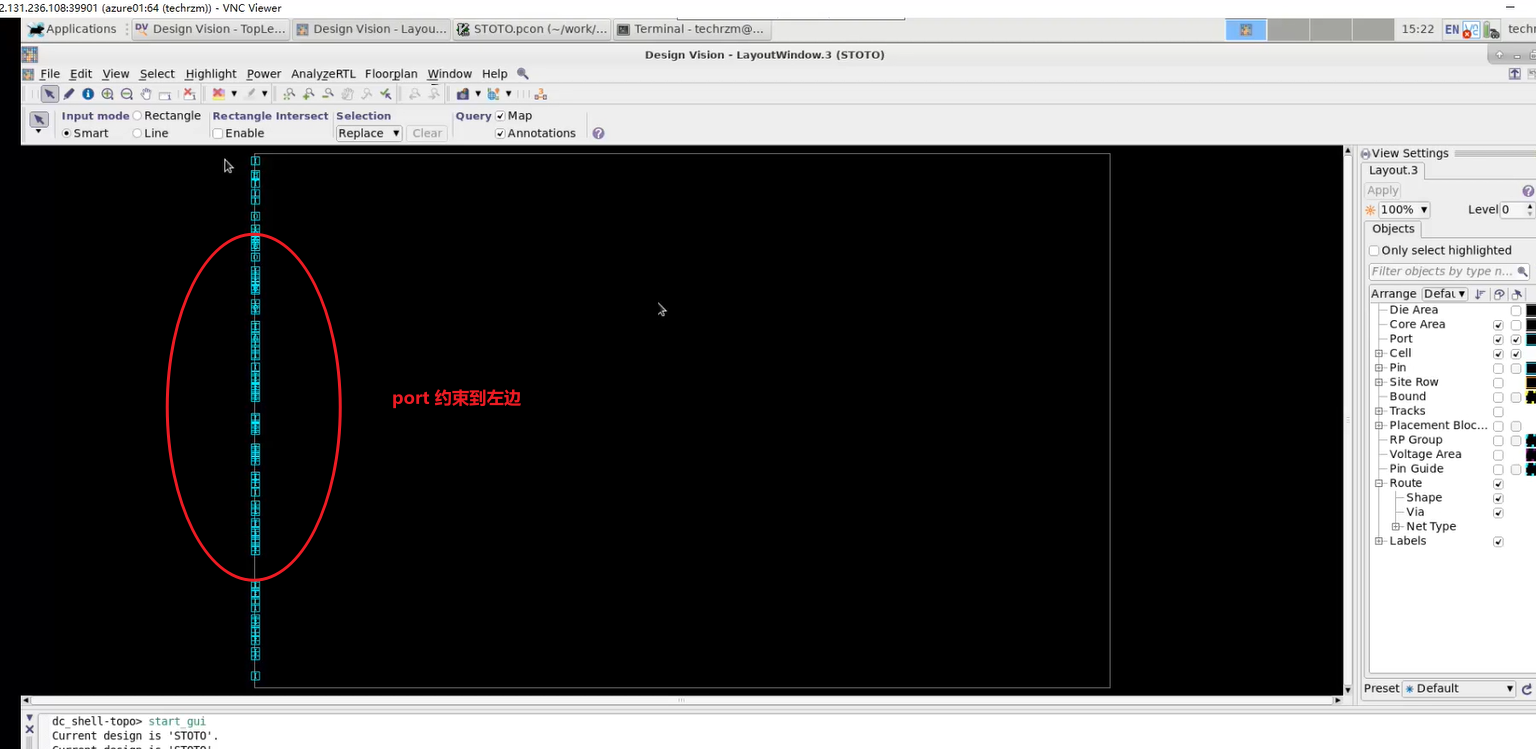

定义相对端口侧

定义确切的端口,宏和阻挡区

- 在RAM的四周设置Blockage,RAM周围会布很多的线,会导致拥塞或者short,在Blockage中不能摆放standcell

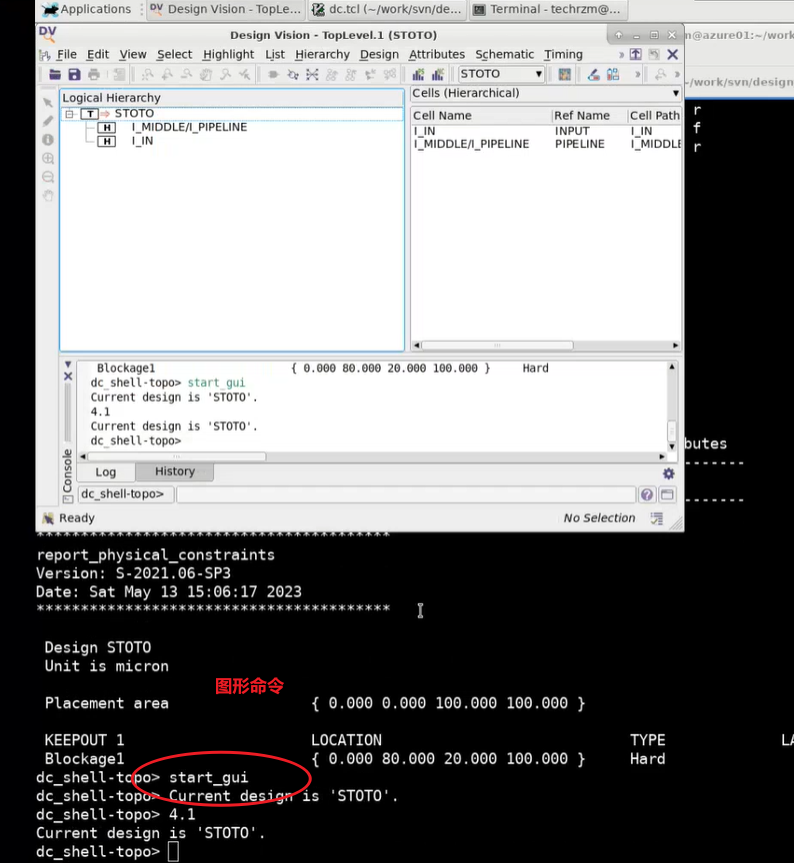

DC-T物理约束

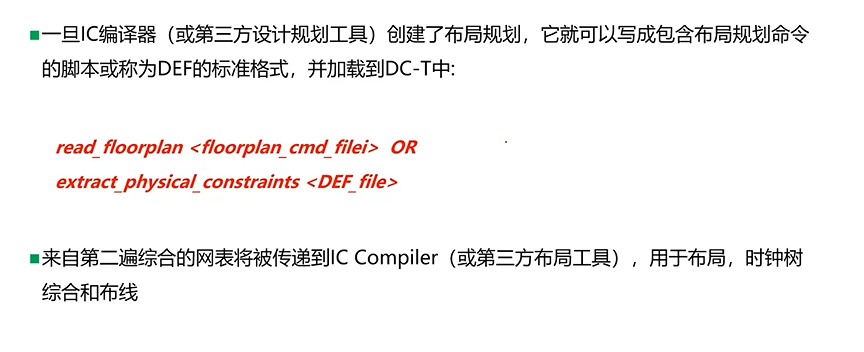

加载实际平面约束-第二次综合

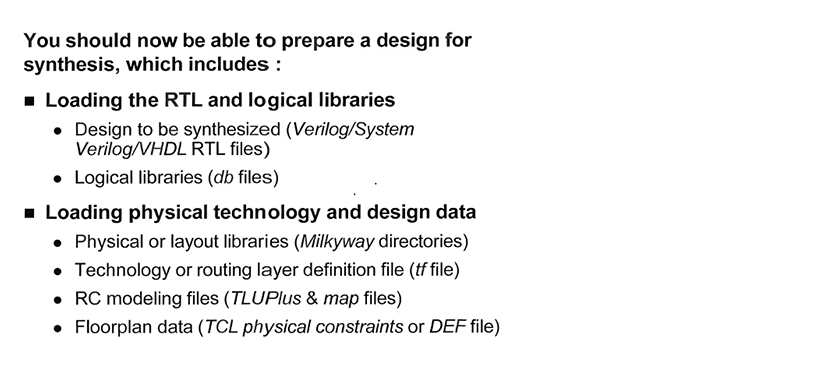

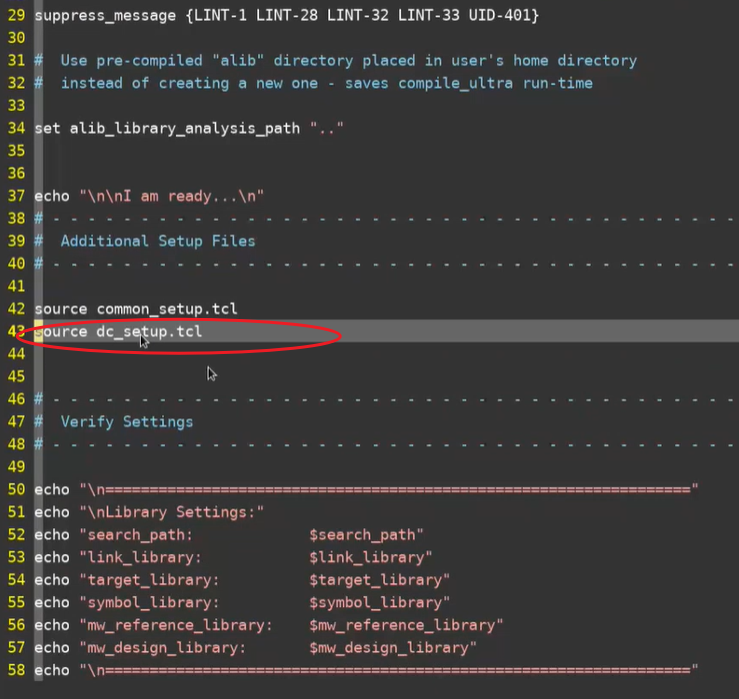

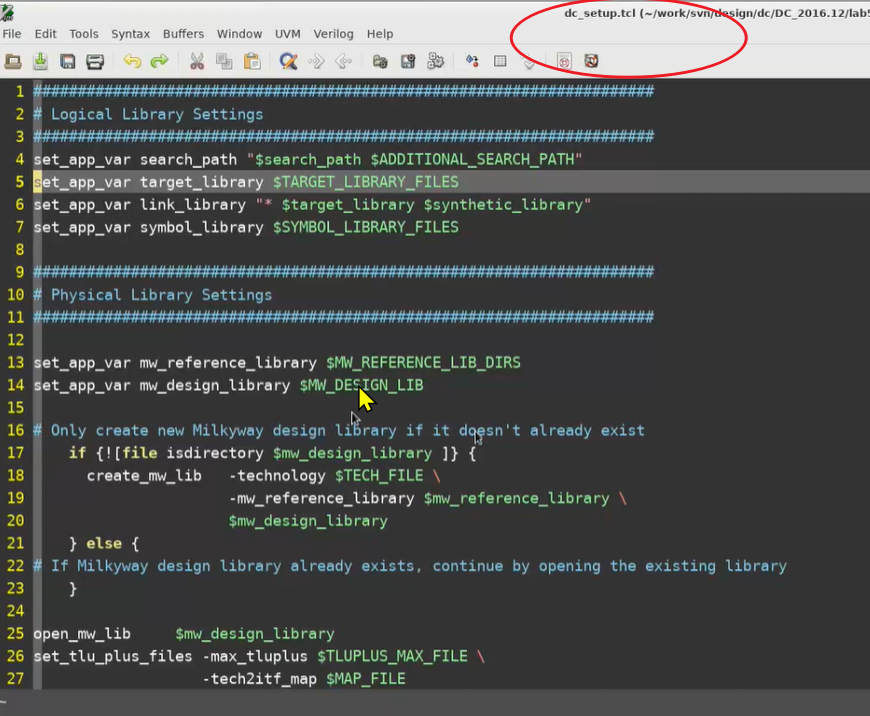

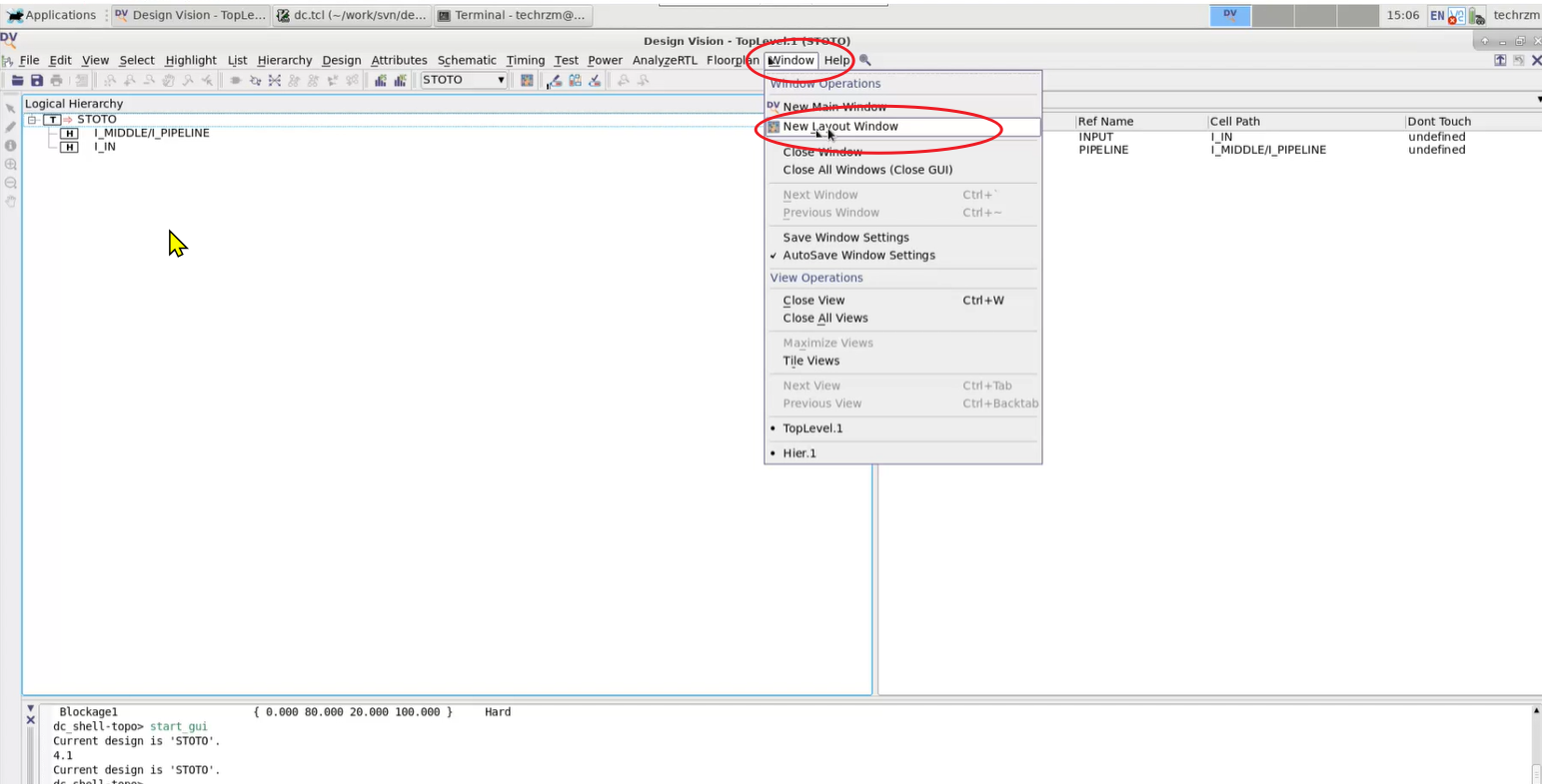

典型的DC-T流程:编译前的准备

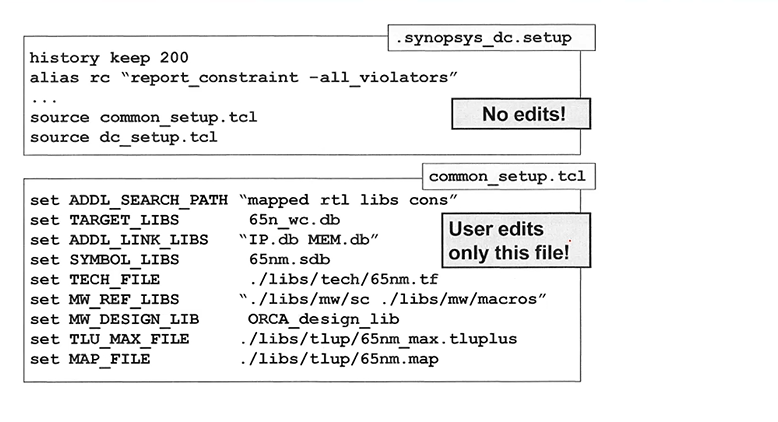

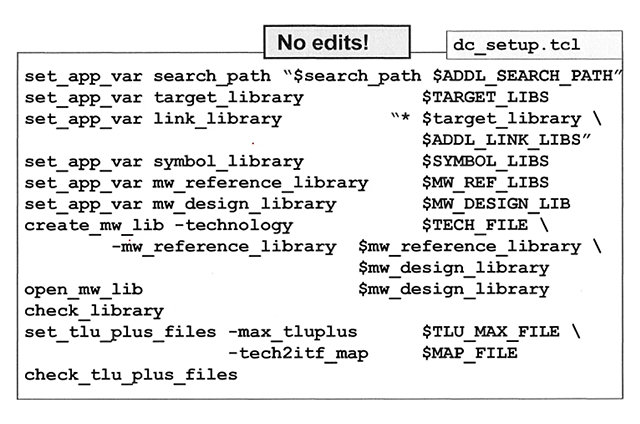

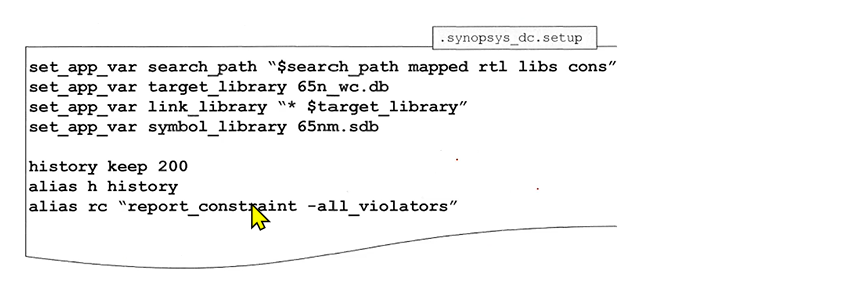

方便的替代设置文件

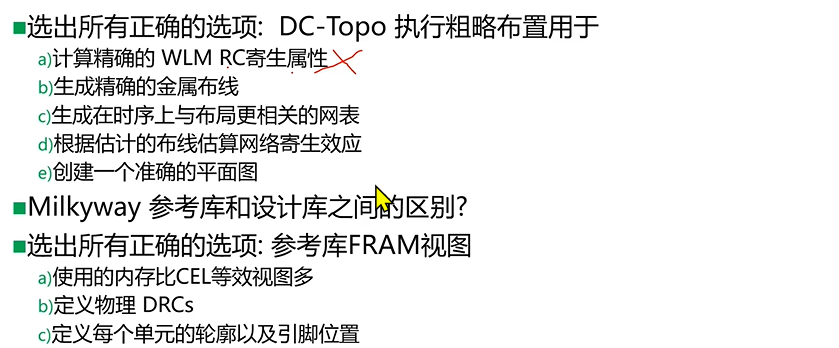

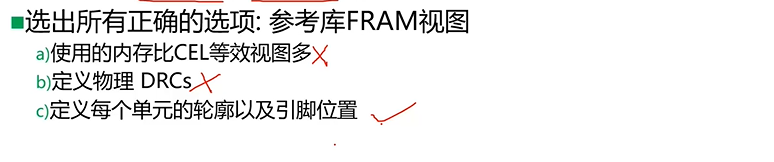

DC-T测试

- a x - DC-T是没有LM模型的

- b x - 不精准的布线

- c √

- d √

- e x - 不是创建精准的floorplan

- milkyway参考库 - standcell\IO\pin

- 设计库 - 设计的物理信息

变量总结:定义逻辑库

命令总结:加载逻辑数据

命令总结:加载物理数据

命令总结:物理约束

总结