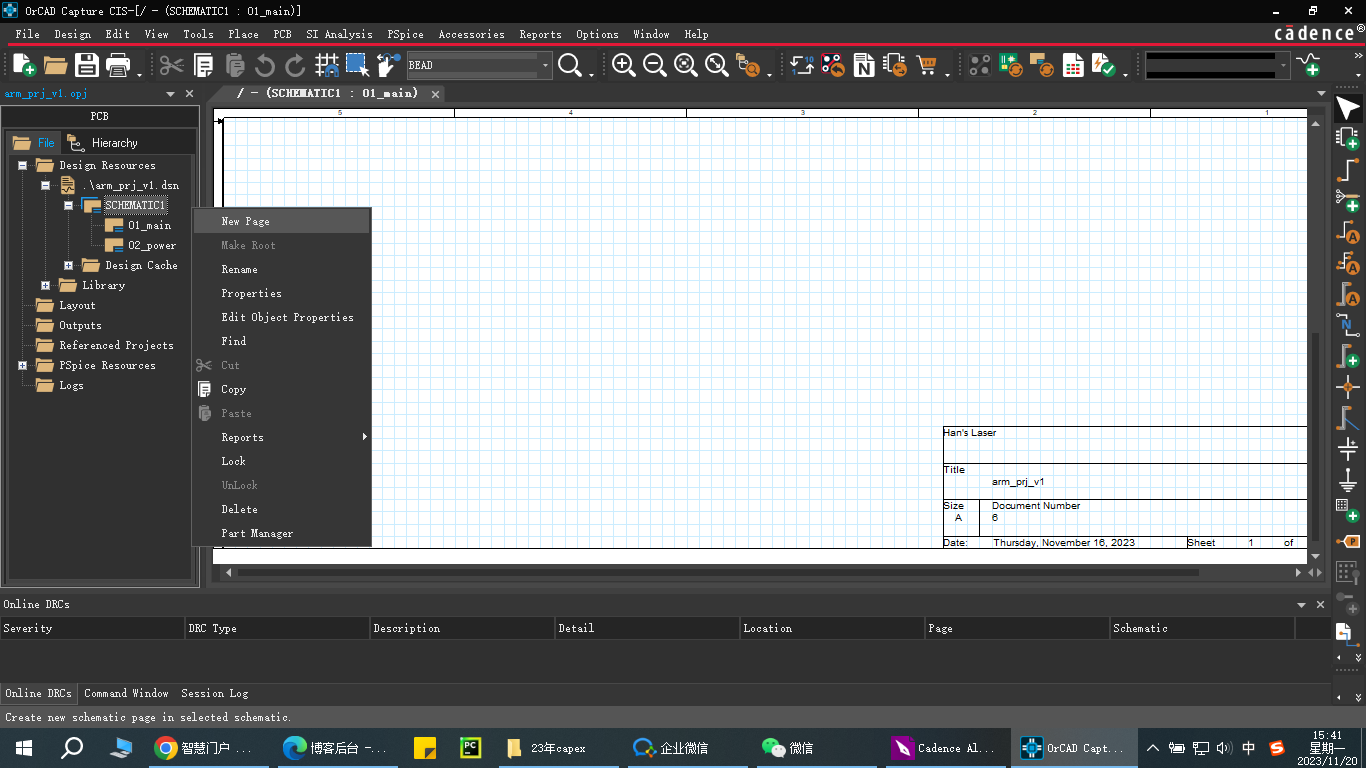

1、新增原理图:“SCHEMATIC”-->“New Page”

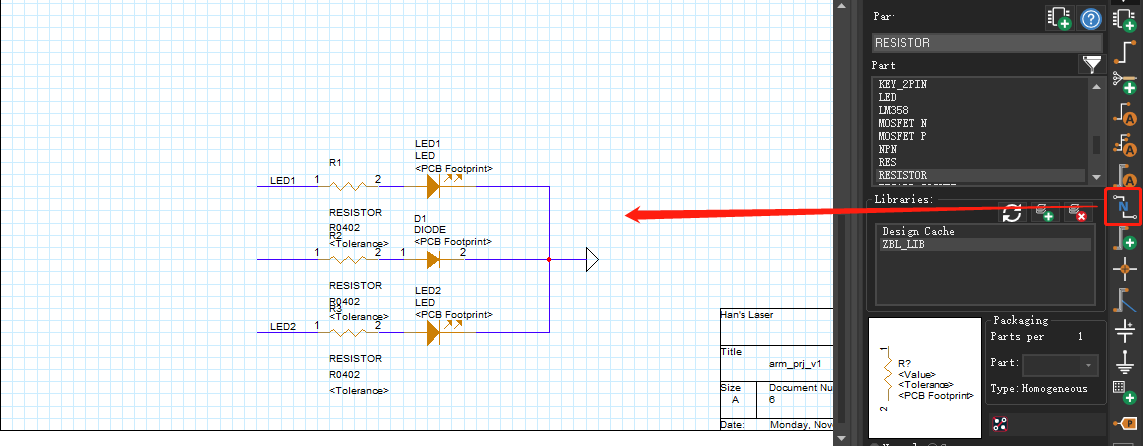

2、元器件放置

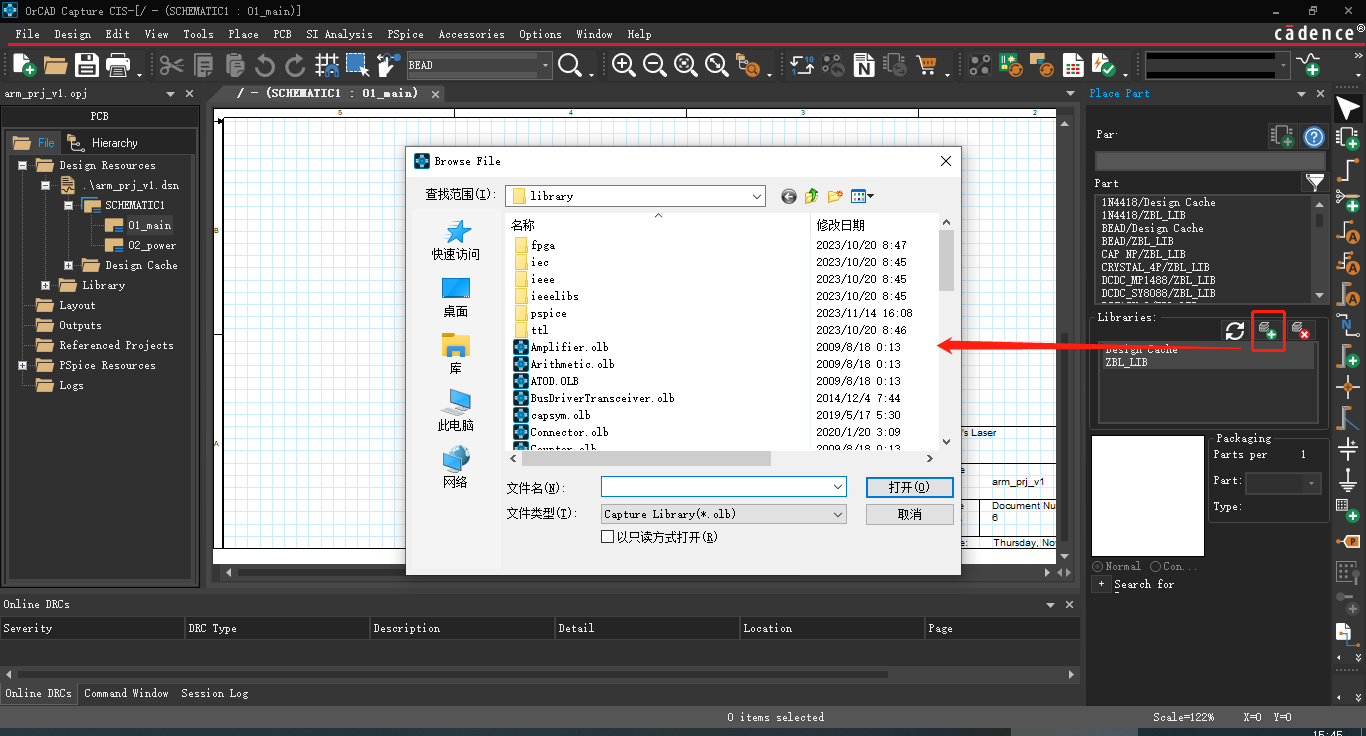

①、添加原理图库

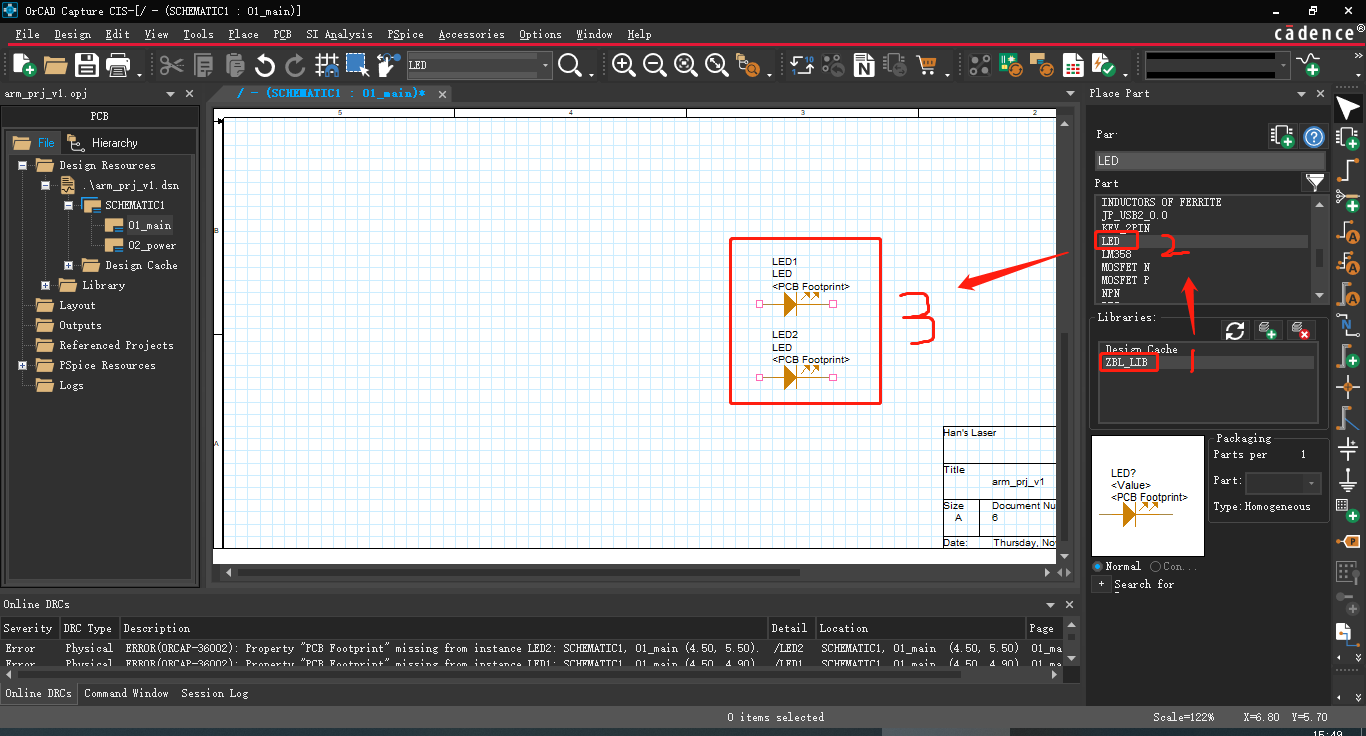

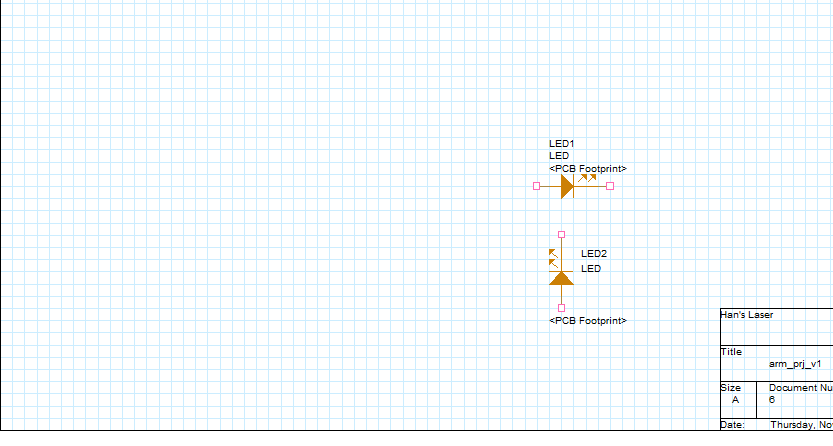

②、放置元器件

选择对应元件库,再选择需要放置的元件,双击该元件后,在到原理图界面放置即可,按ESC退出放置。

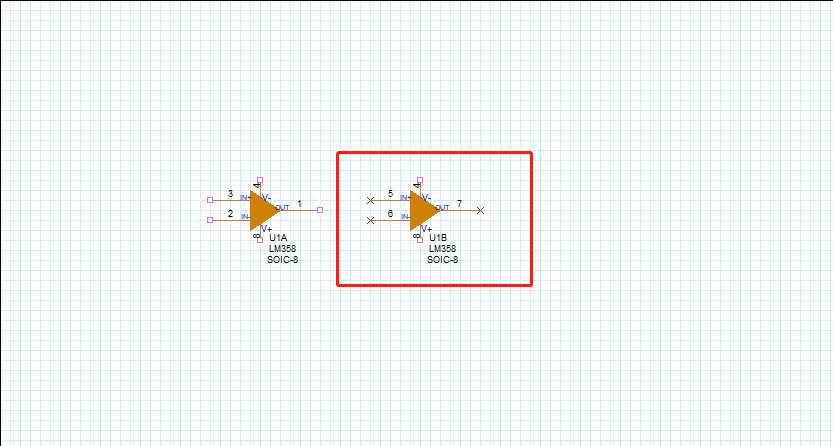

③、旋转放置的元件

选择该元件,单击键盘快捷键“R”即可完成元件旋转,或者点击鼠标右键,选择“Rotate”操作旋转,或者菜单栏“Edit”-->“Rotate”操作。

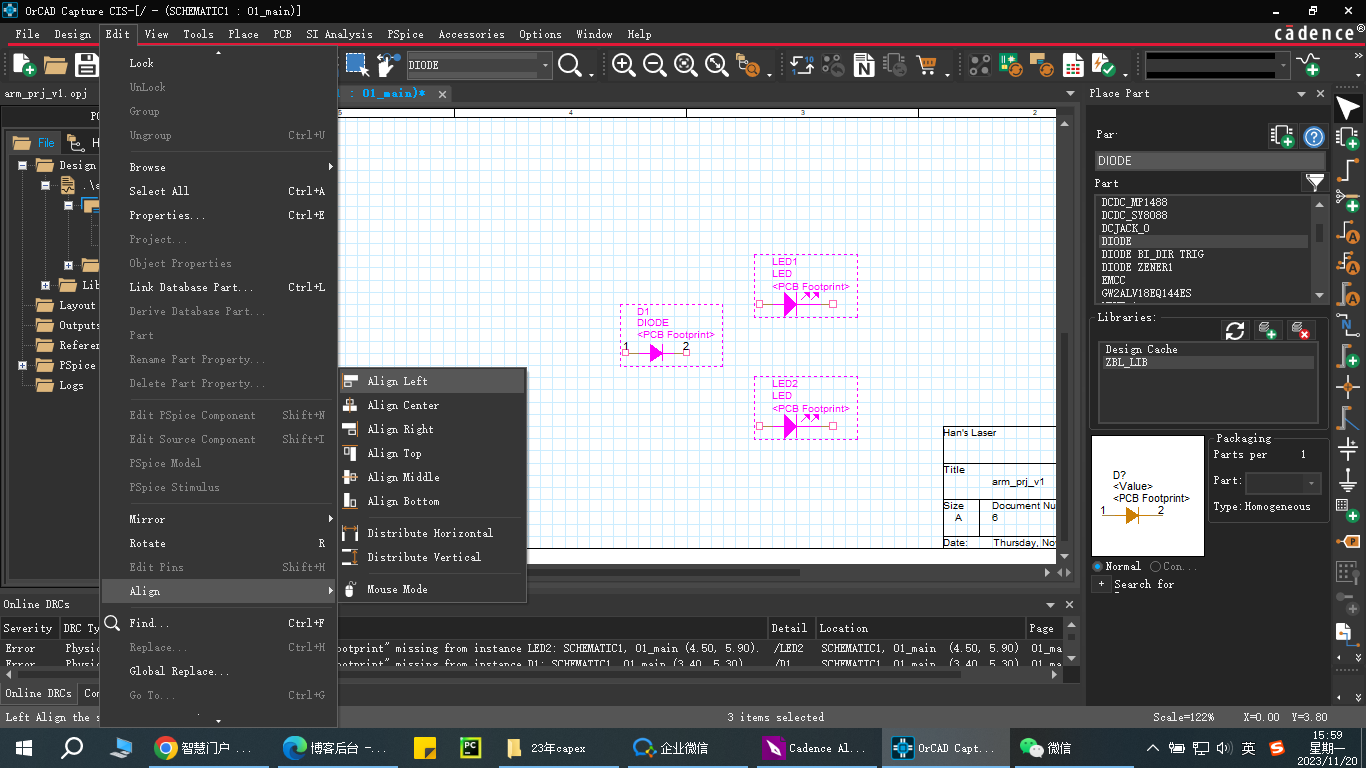

④、元器件对齐

菜单栏“Edit”-->“Align”-->“Align Left”进行元件左对齐。其他的上下左右、中心对齐都是这个选择路径。

⑤、元件的复制(‘Ctrl + C’)、粘贴(‘Ctrl + V’)、剪切(‘Ctrl + X’)、删除(‘Delete’)、撤销(‘Ctrl + Z’)

三、电气连接

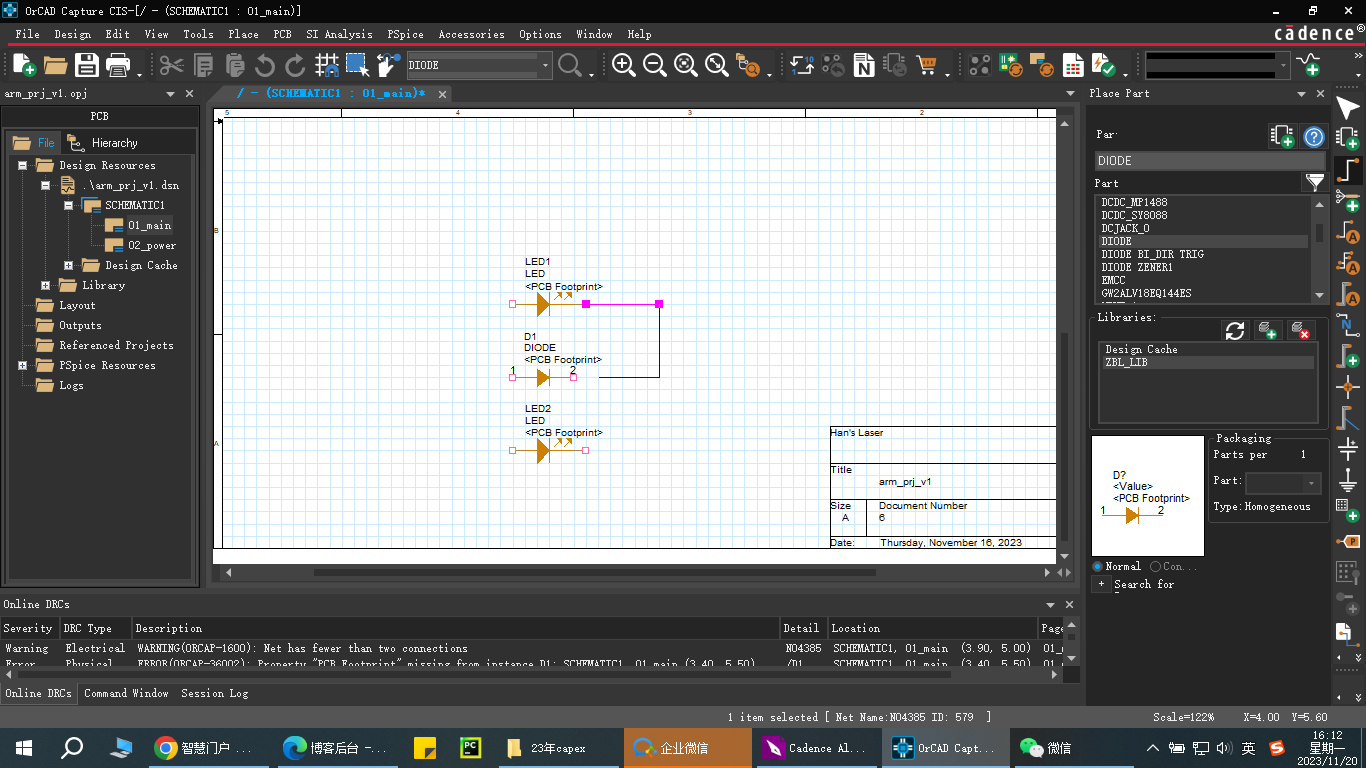

①、导线连接

执行菜单栏“Place”--> “Wire”,或者键盘快捷键‘W’,开始绘制。按“Esc”键或者单击鼠标右键选择“End Wire”选项,结束连线操作。

②、放置节点(导线与导线相通)

执行菜单命令“Place”→“Junction”即可,或者直接按“J”键亦可实现。

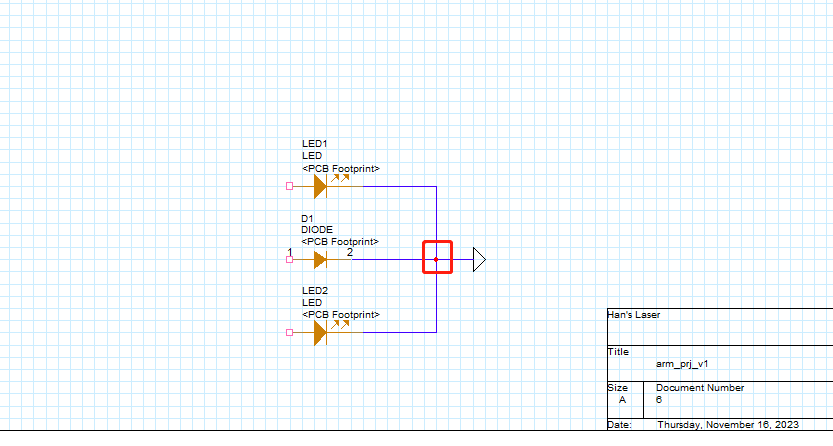

③、放置网络标号(Net Label)

使用网络标号进行电气连接,按“N”键来执行放置网络标号,或者执行菜单命令“Place”→“Net Alias”,放置网络标号。

④、放置 No ERC 检查点

No ERC 检查点即忽略 ERC 检查点,是指该点附加的元器件引脚在进行 ERC 时,如果出现错误或者警告,则错误或者警告将被忽略,不影响网络报表的生成,忽略 ERC检查点本身并不具有任何的电气特性,主要用于检查原理图。

按“X”键来执行放置 No ERC 检查点,或者执行菜单命令“Place”→“No Connect”,也可放置 No ERC 检查点。放置后显示‘X’

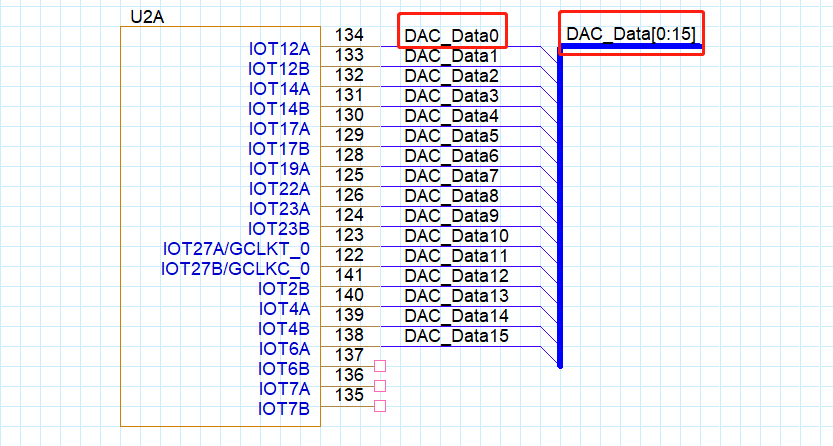

⑤、总线放置

总线代表的是具有相同电气特性的一组导线,在具有相同电气特性的导线数目较多的情况下,可采用总线的方式,以方便识图。

(1)按“B”键放置总线,或者执行菜单命令“Place”→“Bus”;

(2)按“N”键或者执行菜单命令“Place”→“Net Alias”,放置网络标号。

总线注意事项:

- 总线的名字不能以数字结尾

- 符号[ ]前后不能有空格

- 命名必须是名字加[ ],如 BUS[0:15]。

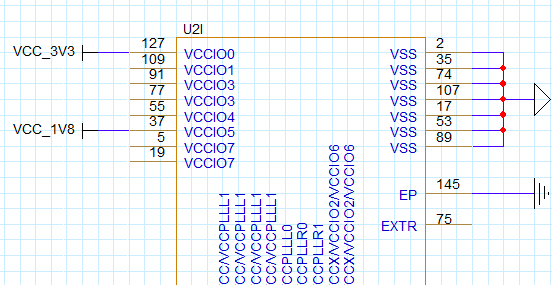

⑥、放置电源、地符号

(1)按“F”键或者执行菜单命令“Place”→“Power”;

(2)按“G”键或者执行菜单命令“Place”→“Ground”放置地网络标识。

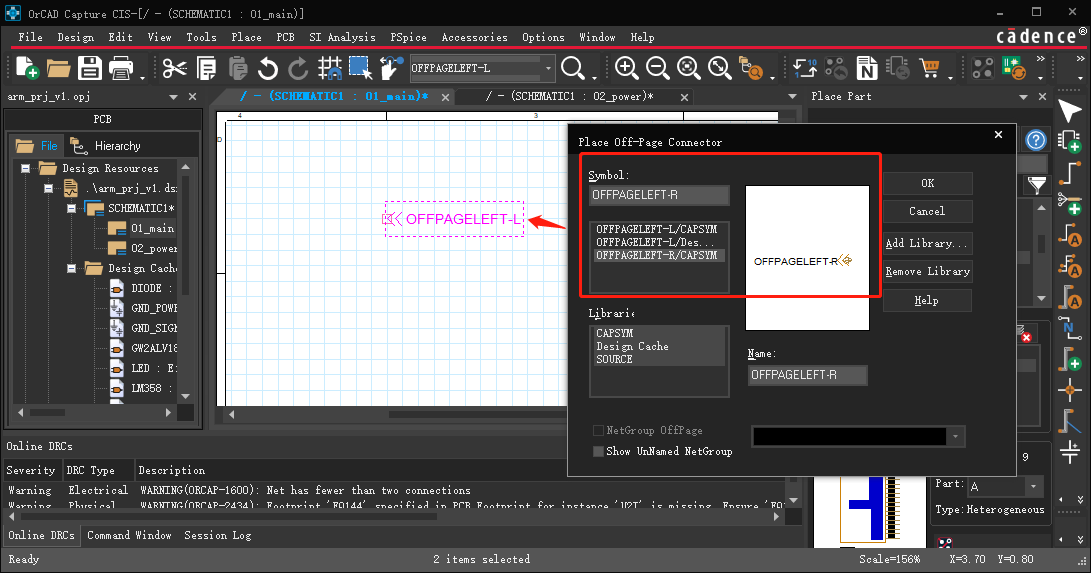

⑦、放置页连接符

图纸页和图纸页之间的线路连接,Off-Page Connector

执行菜单命令“Place”→“Off-Page Connector”,进行页面连接符合命名。

8、原理图添加差分属性

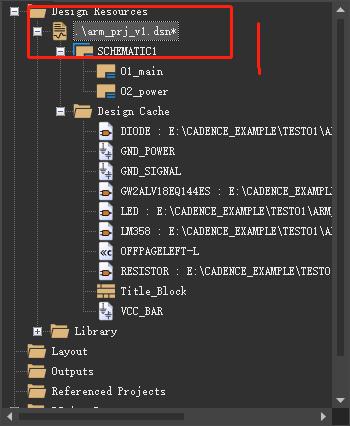

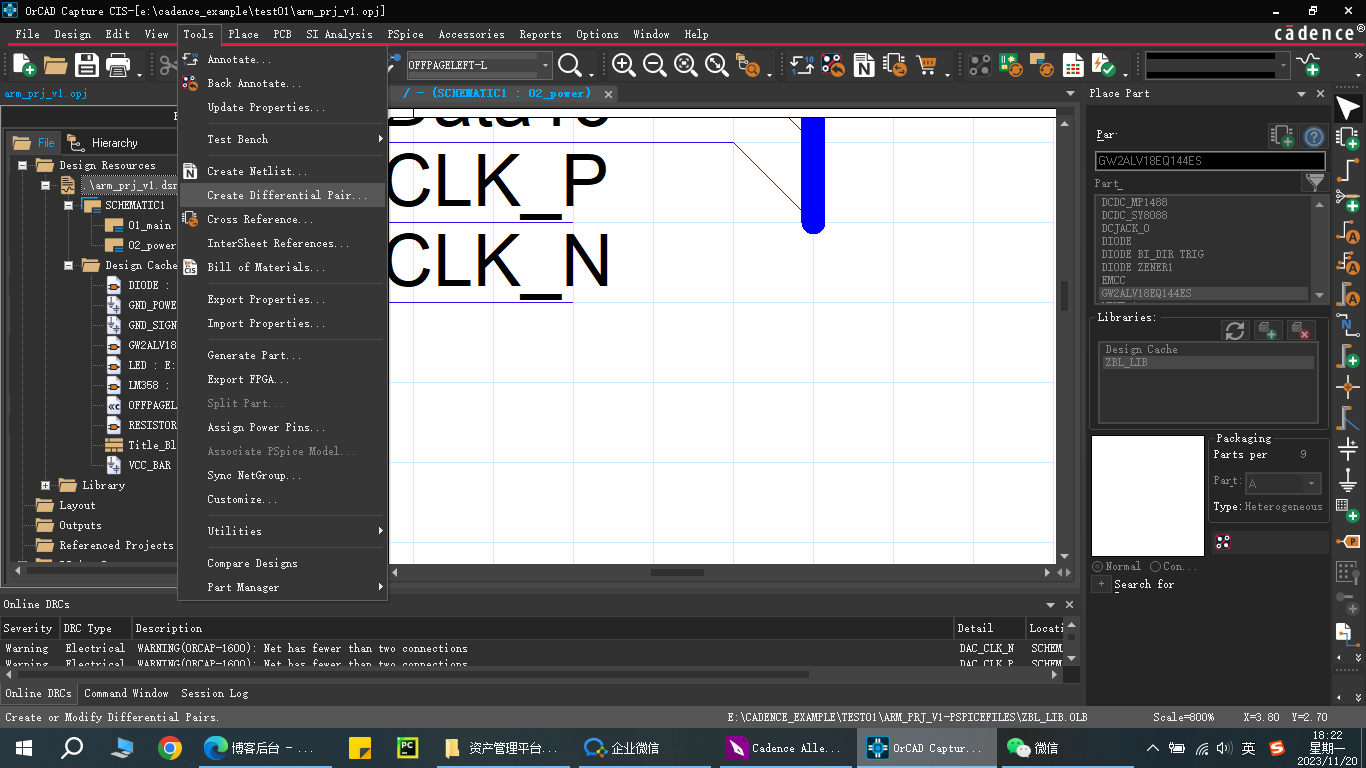

(1)首先鼠标左键单击选中原理图工程(.dsn),然后执行菜单命令“Tools”→“Create Differential Pair”。

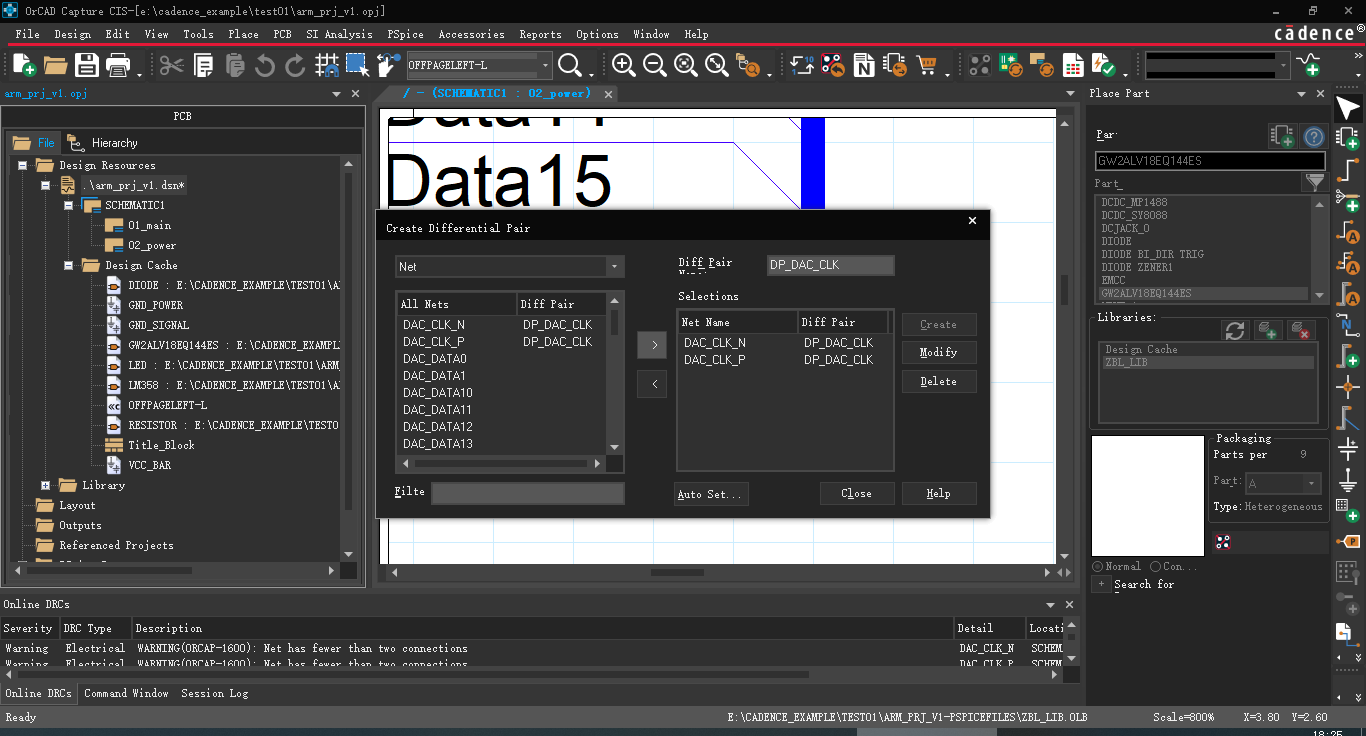

(2)在弹出的“Create Differential Pair”对话框中查找需要设置的网络名并添加到“Selections”中。 如图 5-95 所示在箭头①处输入需要查找的大概网络名, 在箭头②处选择具体对应的网络名,单击箭头③处的符号即可添加到“Selections”中,单击箭头④处的“Create”按钮即可自动创建差分类,最后单击箭头⑤处关闭。

(3)、差分对的属性,最好描述说明,PCB设计才不会出错。