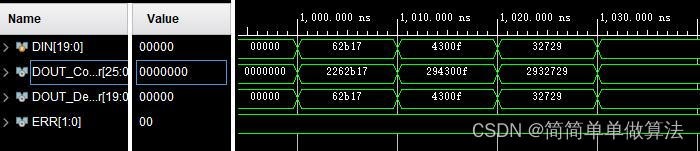

1.算法运行效果图预览

2.算法运行软件版本

matlab2022a和vivado2019.2

3.算法理论概述

Hamming 编码是一种用于纠错错误的线性分组码。它是由理查德·哈明(Richard Hamming)在20世纪中期提出的,用于在数字通信和存储系统中检测和纠正传输过程中产生的错误。本文将从原理、实现过程和应用领域三个方面详细介绍 Hamming 编码。

1. 原理

Hamming 编码是一种特殊的环形分组码,它通过在数据位中插入冗余位来实现错误检测和纠正。其原理是在编码时根据冗余位的位置和值来检测并纠正单比特错误,从而提高数据传输的可靠性。

1.1 编码规则

Hamming 编码的主要思想是根据数据位的位置,将冗余位插入到数据位中,形成编码。编码规则如下:

数据位编号:将数据位从1开始编号。

冗余位位置:冗余位的位置是2的幂次方位置(1、2、4、8...)。

编码方式:对于冗余位,其值是根据与其相关的数据位进行异或运算得到的。

1.2 错误检测和纠正

通过插入冗余位,Hamming 编码可以实现单比特错误的检测和纠正。当接收到编码后的数据时,可以根据冗余位的值来检测错误。如果检测到错误,可以通过异或运算来确定出错的位并进行纠正。

2. 实现过程

2.1 编码过程

Hamming 编码的编码过程包括以下步骤:

确定数据位和冗余位的位置:根据编码规则,确定数据位和冗余位的位置。

插入冗余位:根据冗余位的位置,将计算得到的冗余位插入到数据位中。

发送编码后的数据:将编码后的数据传输给接收端。

2.2 解码过程

Hamming 编码的解码过程包括以下步骤:

接收编码后的数据:接收从发送端传输过来的编码后的数据。

计算冗余位:根据冗余位的位置和接收到的数据计算冗余位的值。

检测错误:比较接收到的冗余位和计算得到的冗余位的值,检测是否存在错误。

纠正错误:如果检测到错误,通过异或运算确定错误位并进行纠正。

3. 应用领域

3.1 数字通信

Hamming 编码在数字通信领域广泛应用于数据传输过程中的错误检测和纠正。在高速数据传输中,由于噪声等因素,数据可能会发生位错误,使用 Hamming 编码可以提高数据传输的可靠性。

3.2 存储系统

在存储系统中,如磁盘驱动器、固态硬盘等,数据的正确性至关重要。通过使用 Hamming 编码,可以在存储过程中检测和纠正数据位错误,防止数据损坏。

3.3 ECC内存

ECC(Error-Correcting Code)内存是一种采用纠错码技术的内存模块,用于提高计算机内存的可靠性。Hamming 编码在 ECC 内存中被广泛应用,可以有效检测和纠正内存中的位错误,提高系统稳定性。

3.4 数据传输

在无线通信、有线通信等领域,数据传输过程中可能会受到各种干扰,从而引发数据位错误。Hamming 编码可以在数据传输中检测和纠正错误,确保数据的可靠传输。

综上所述,Hamming 编码是一种常用的纠错编码方法,通过在数据位中插入冗余位来实现错误检测和纠正。其原理简单而有效,被广泛应用于数字通信、存储系统、内存模块等领域,提高了数据传输和存储的可靠性。通过了解 Hamming 编码的原理和实现过程,可以更好地理解其在通信和存储中的应用。

4.部分核心程序

%编码

fprintf(fid,'module HammingCoder(\n input [%d:0] D,\n output [%d:0] DOUT);\n\n',K-1,K+m);

fprintf(fid,' wire [%d:0] data;\n\n',K+m-1);

fprintf(fid,' assign data[%d:0] = D[%d:0];\n',K-1,K-1);

...................................................

fprintf(fid,' assign DOUT = {^ data[%d:0], data[%d:0]};\n',K+m-1,K+m-1);

fprintf(fid,'\nendmodule\n\n\n');

fclose(fid);

%译码器

fid2 = fopen(FILE2,'wt');

fprintf(fid2,'module HammingDecoder(\n input [%d:0] D,\n output [%d:0] DOUT,\n output [1:0] ERR);\n\n',K+m,K-1);

fprintf(fid2,' wire [%d:0] S;\n',m-1);

fprintf(fid2,' wire PARITY;\n');

fprintf(fid2,' wire error_hamming;\n');

...........................................................

fprintf(fid2,' assign PARITY = ^ D[%d:0];\n',K+m);

fprintf(fid2,' assign error_hamming = | S[%d:0];\n',m-1);

fprintf(fid2,' assign ERR = {PARITY,error_hamming};\n');

fprintf(fid2,'\nendmodule\n');

fclose(fid2);

module HammingDecoder(

input [25:0] D,

output [19:0] DOUT,

output [1:0] ERR);

wire [4:0] S;

wire PARITY;

wire error_hamming;

assign S[0] = D[20] ^ D[0] ^ D[3] ^ D[5] ^ D[6] ^ D[9] ^ D[10] ^ D[11] ^ D[12] ^ D[13] ^ D[17] ^ D[18];

assign S[1] = D[21] ^ D[1] ^ D[4] ^ D[6] ^ D[7] ^ D[10] ^ D[11] ^ D[12] ^ D[13] ^ D[14] ^ D[18] ^ D[19];

assign S[2] = D[22] ^ D[0] ^ D[2] ^ D[3] ^ D[6] ^ D[7] ^ D[8] ^ D[9] ^ D[10] ^ D[14] ^ D[15] ^ D[17] ^ D[18] ^ D[19];

assign S[3] = D[23] ^ D[1] ^ D[3] ^ D[4] ^ D[7] ^ D[8] ^ D[9] ^ D[10] ^ D[11] ^ D[15] ^ D[16] ^ D[18] ^ D[19];

assign S[4] = D[24] ^ D[2] ^ D[4] ^ D[5] ^ D[8] ^ D[9] ^ D[10] ^ D[11] ^ D[12] ^ D[16] ^ D[17] ^ D[19];

assign DOUT[00] = D[00] ^ S[0] & S[2];

assign DOUT[01] = D[01] ^ S[1] & S[3];

assign DOUT[02] = D[02] ^ S[2] & S[4];

assign DOUT[03] = D[03] ^ S[0] & S[2] & S[3];

assign DOUT[04] = D[04] ^ S[1] & S[3] & S[4];

assign DOUT[05] = D[05] ^ S[0] & S[4];

assign DOUT[06] = D[06] ^ S[0] & S[1] & S[2];

assign DOUT[07] = D[07] ^ S[1] & S[2] & S[3];

assign DOUT[08] = D[08] ^ S[2] & S[3] & S[4];

assign DOUT[09] = D[09] ^ S[0] & S[2] & S[3] & S[4];

assign DOUT[10] = D[10] ^S[0] & S[1] & S[2] & S[3] & S[4];

assign DOUT[11] = D[11] ^S[0] & S[1] & S[3] & S[4];

assign DOUT[12] = D[12] ^S[0] & S[1] & S[4];

assign DOUT[13] = D[13] ^S[0] & S[1];

assign DOUT[14] = D[14] ^S[1] & S[2];

assign DOUT[15] = D[15] ^S[2] & S[3];

assign DOUT[16] = D[16] ^S[3] & S[4];

assign DOUT[17] = D[17] ^S[0] & S[2] & S[4];

assign DOUT[18] = D[18] ^S[0] & S[1] & S[2] & S[3];

assign DOUT[19] = D[19] ^S[1] & S[2] & S[3] & S[4];

assign PARITY = ^ D[25:0];

assign error_hamming = | S[4:0];

assign ERR = {PARITY,error_hamming};

endmodule