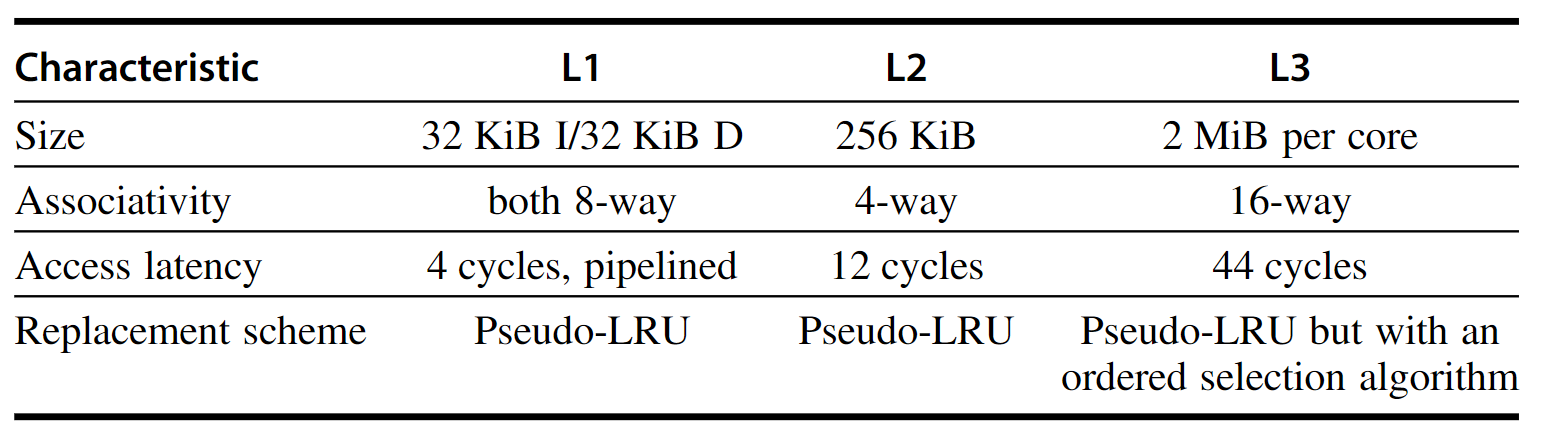

1、inter i7所用层次结构内容

修改处Data DLB(Data TLB).

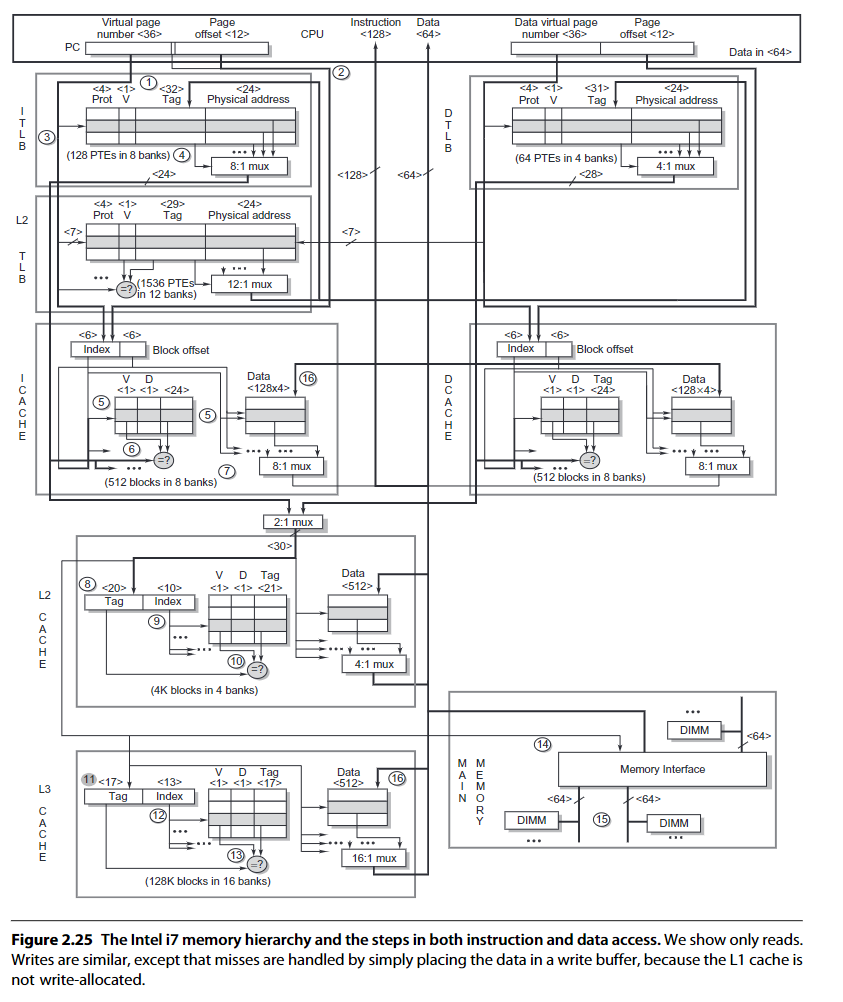

2、Inter i7存储器层次结构及指令与数据访问步骤图

3、指令与数据访问步骤:

- 指令地址的页帧(36bit)被发送给指令TLB(①)。

- 同时虚拟地址的12位页内偏移量被发送给指令缓存(ICACHE).对于8路组相连cache来说,缓存需要12位:6位用于索引缓存,再加上64个字节块的6位偏移量(②)。

- 指令TLB为了查找与地址匹配的有效页表项(③④)。

- 地址得索引字段被发送到指令缓存的8个存储体中(⑤)。

- 将四个标签及有效位与指令TLB中的物理页帧进行对比(⑥)。

- i7指令希望得到16个字节。L1缓存实现流水化,一次命中延迟为4个clock(⑦)。

- 30位的块地址被分为20位的标签和10位的索引(⑧)。

- 索引和标签再次被发送给不区分指令和数据的L2cache的4个存储体(⑨)。

- 如果有一个匹配且有效(⑩)。

- 若L2缺失,则访问L3,其索引大小为13位被发送给16个存储体(⑪⑫)。

- L3的标签长度为117位,将其送给来自TLB的物理地址进行对比(⑬)。

- 若L3缺失,请求主存储器,i7有三个64位通道,且通道地址发送的是同一个地址(⑭)。

- 当所有通道拥有相同的的DIMM时,就可以进行宽通道传输。每个通道最多支持4个DDR DIMM(⑮)。

- 在数据返回时,会将它们同时放在L3缓存与L1缓存中(⑯)。