SD Host功能列表

- 系统挂接在SoC中的

- 有控制寄存器和状态寄存器

- 内建DMA-数据需要从外部将数据读取到buffer中,然后再对于SD卡进行写操作;对于读操作,首先先将SD卡读取到控制器中buffer中,再从buffer中将数据存储到SoC中的存储单元中,数据搬移需要使用DMA

- DMA也是挂接在AHB总线上的

- 数据缓存的FiFo和内嵌DMA模块

- SD卡的时钟频率比较低,所以需要分频电路

- 读操作,硬件停时钟功能 - 数据-->SD Host中的buffer-->SRAM和eFlash,在数据从数据到buffer中的时候,此时不能再进行读,此时可以关闭时钟

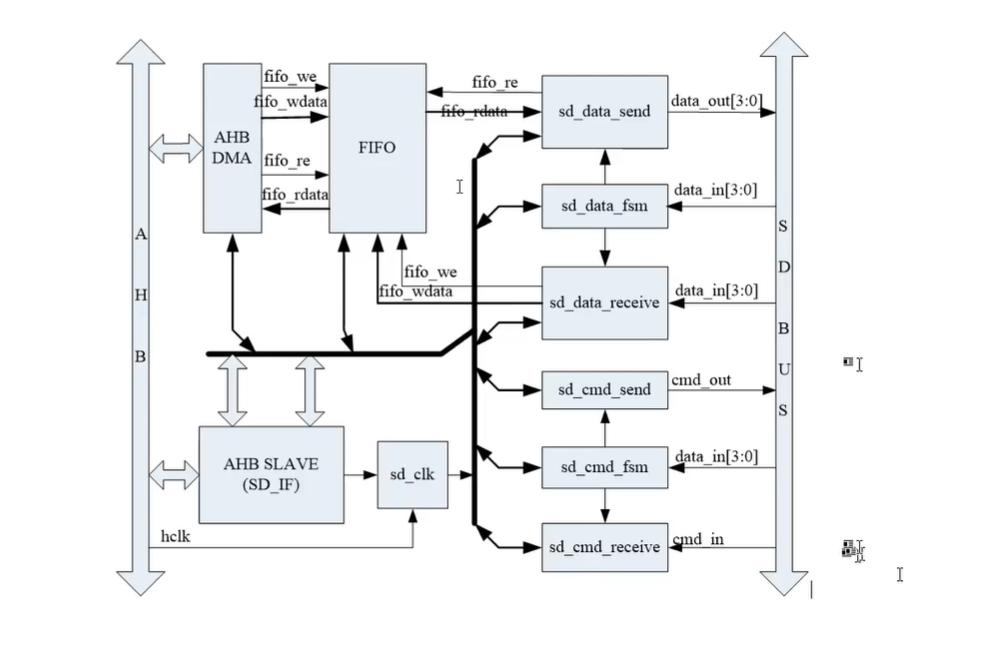

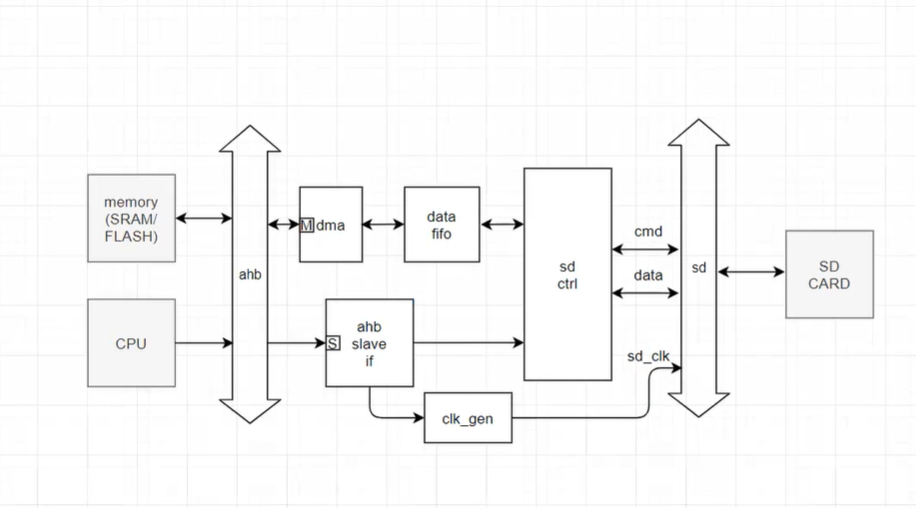

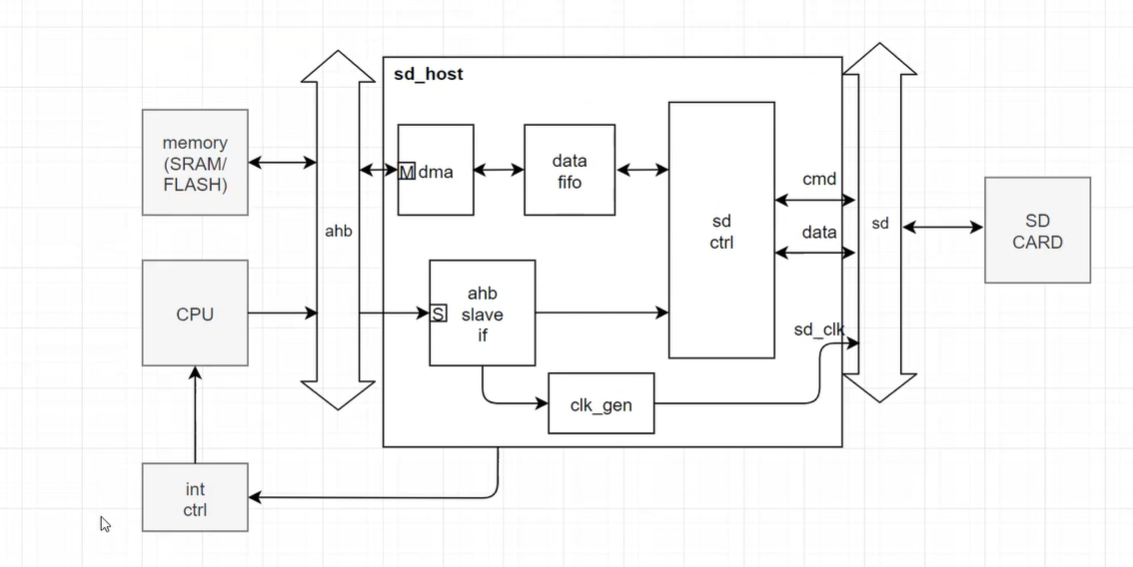

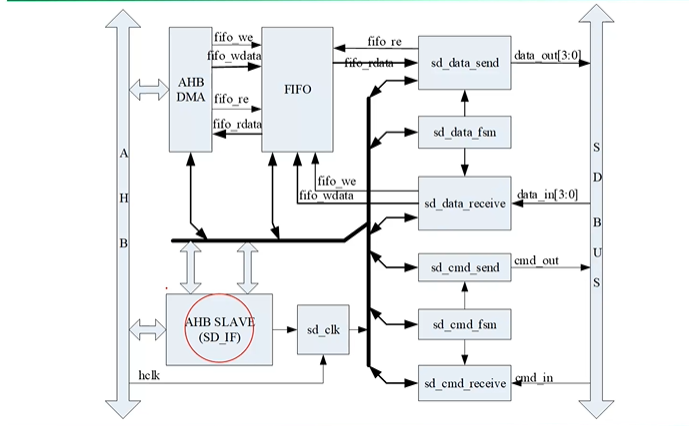

架构

- 先将外部需要的接口画出来:AHB总线和SD总线

- SD Host是基于AHB总线的,并且有一些控制和状态寄存器,所以需要设置ahb_slave_if模块,处理AHB信号

- ahb_slave_if中有控制寄存器,进行任务驱动,产生任务信息给到sd_ctrl模块

- 设置一个sd_ctrl模块发起对于sd总线的请求

- sd_ctrl与sd总线的交互除了有命令总线还有数据总线,都是双向的

- ahb时钟比较快,sd时钟比较慢,所以需要有 一个时钟分频模块

- 根据配置信息,产生命令,启动SD ctrl进行一些命令的发送

- 需要有一个缓存存储数据(FiFo),对于读数据,sd_ctrl控制数据总线,读取数据从sd总线上读取出来存储到fifo中,fifo中的数据满了之后,通过DMA将数据存储到SoC中的存储单元中

- DMA-搬运数据的时候是一个master,控制总线,发送数据

- ahb_slave_if模块是slave

sd_ctrl模块

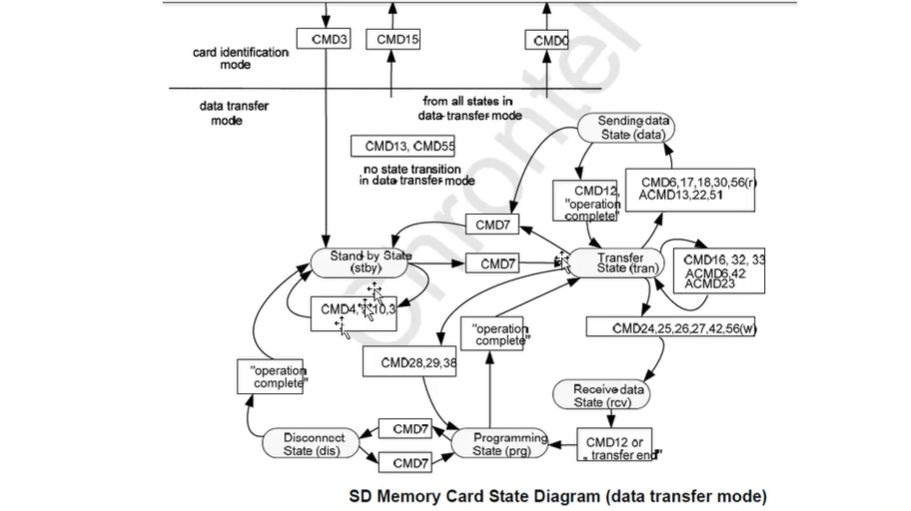

- 对于sd card进行读写,当上电之后,sd card处于idle状态,需要通过命令发送跳转到data transfer state,才可以进行数据的读写

- sd协议的状态机比较复杂,有两种设计思路

1.通过硬件实现所有的状态机,包括卡识别模式和数据传输模式

每一步操作都需要很多的指令,首先需要在ahb_slave_if模块中通过软件配置所有的操作

优点:集中式的配置,事先将所有的操作都配置好,发起启动信号之后,由硬件进行执行,和CPU交互频率较低,CPU负担较轻

缺点:硬件实现非常复杂,后期更改软件灵活性差

2.将硬件的执行力度降低,硬件操作的时候有两种:一种进行数据传输或者只进行命令传输,可以以一条指令的数据传输为力度进行设计状态机,硬件只实现一条CMD的发送和response的接收,只实现一条CMD对应的data的发送和接收

整个流程的控制权全部交给CPU,也就是软件,硬件只实现最小粒度的命令发送和接收,以及数据发送和接收

优点:硬件实现代价小,软件的灵活性非常大

缺点:CPU需要和SD Host进行大量的交互,CPU负担较重

- amd发送和response返回都是类似的

CPU与SD Host通过中断进行交互,SD Host也会发送中断给到中断控制器,CPU收到中断之后,需要进入中断处理程序处理中断

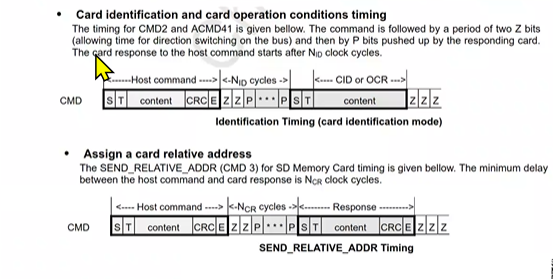

CMD发送

- CMD发送的时序是类似的,可以设置一个状态机,实现CMD的发送和response接收

- 接收来自ahb_salve_if的配置

- 再设置一个状态机,实现data的发送和接收

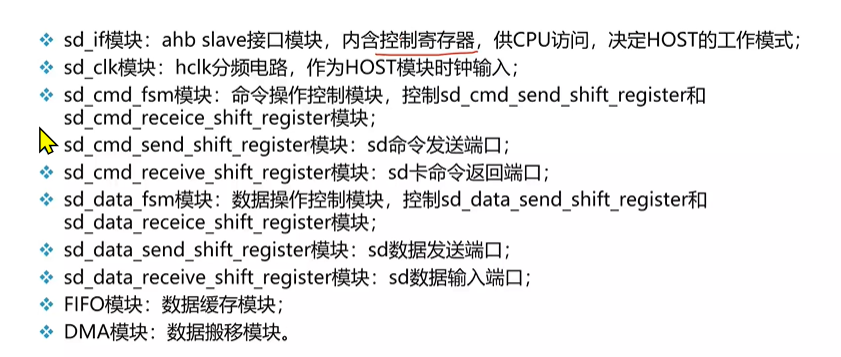

SD Host控制功能列表

SD Host控制器软硬件模块划分

SD Host控制器模块功能描述

- 通过异步fifo实现不同时钟域之间数据的传递

SD Host模块功能简述

SD Host架构设计文档