文章地址: Diplomatic Design Patterns: A TileLink Case Study (carrv.github.io)

一,简介

Diplomacy是一种基于Scala语言的编程框架。在Chisel硬件描述语言构建的CPU核心设计中,单纯使用Chisel无法完成复杂的连线和参数传递工作。因此开发了Diplomacy用于辅助SOC架构和集成。

相关代码在:rocket-chip/src/main/scala/diplomacy at master · chipsalliance/rocket-chip (github.com)

其主要在设计中承担以下内容:

- 在整个SOC范围内对每一个具有互联关系的模块之间的进行参数传递,协商或修改。这些参数包含但不限于:线宽,访问地址,访问权限,协议类型,方法。

- 对于模块间的互联逻辑进行例化。但是需要指出的是,用户必须通过对Diplomacy提供的抽象成员进行实例化的方式提供实际的连线类型和宽度来进行连线。实例化的类型可以是一种通用总线协议例如TileLink或者AXI4,或者是中断甚至是时钟和复位信号。

- 实例化位于每一个子模块内部的Chisel代码,产生模块内的逻辑电路。

- Diplomacy实际上延后了每一个Chisel模块的例化时刻,在这之前进行参数协商和传递工作。每个模块有自己需要认可的参数,例如总线位宽等。

Diplomacy is a parameter negotiation framework for generating parameterized protocol implementations.

TileLink is a highly- parameterized chip-scale shared-memory interconnect standard.

The implementation of TileLink in the Rocket chip generator exploits Diplomacy to specialize the interconnect to different levels of protocol conformance.

二,Diplomacy

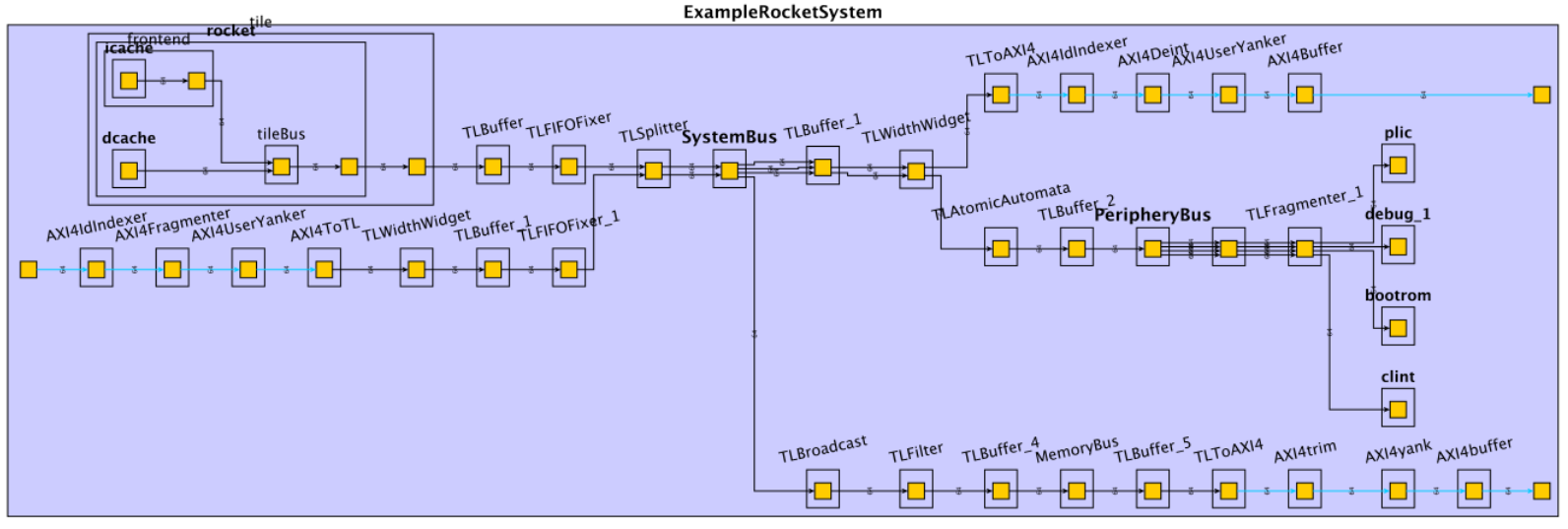

基于diplomacy的chisel设计在编译生成时分为两步:第一步进行参数协商,并生成拓扑图,每个节点自动协商每条边的值。第二步是进行具体的硬件生成。以此保证互联参数的正确性。

参数协商本身由两个独立的过程组成,1,从源节点开始,参数传递直到到达所有汇节点。2,从所有汇节点开始,另一些参数传递直到源节点,因此每条边接受到两组参数。

因此,该协议的基础是用来表示电路连接关系的拓扑图。节点(Nodes)是设计中需要用到互联参数来生成具体电路的模块。边(edge)表示主从节点的配对,因此其有源节点和汇节点,并承担参数协商的作用。一个模块可以具有多个节点,并且一个节点可以具有多条边。协商参数可以从节点指定或者从节点间的协商中得到。diplomacy希望用户描述一个由nodes组成的有向无环图。

以rocketchip的diplomatic为例,

注意到在一个典型的rocketsystem中tilelink和axi4协议均有所采用。axi4用于外部通信,而tilelink用于内核内部。故examplerocketsystem的接口是axi接口。

一个例子:(3条消息) rocket diplomacy学习-CSDN博客

三,Tilelink

未完

参考资料:

Diplomacy机制详解(二)框架 - 知乎 (zhihu.com)

(3条消息) rocket diplomacy学习-CSDN博客

rocket-chip/src/main/scala/diplomacy at master · chipsalliance/rocket-chip (github.com)

Seventh Workshop on Computer Architecture Research with RISC-V (CARRV 2023) | carrv.github.io