layout: post

title: AD总结时间

categories: 日志

tags:

- 开发

- 开发任务

BGImage: 'https://github.xutongxin.me/https://raw.githubusercontent.com/xutongxin1/PictureBed/master/img0/20201220234325.png'

jekyll-theme-WuK:

musicid: '744590'

环境:AD20

电路封装库:嘉鹏钉钉的库

新环境准备

本地化+库导入(设置,date类选项)

画PCB步骤

-

开个原理图

-

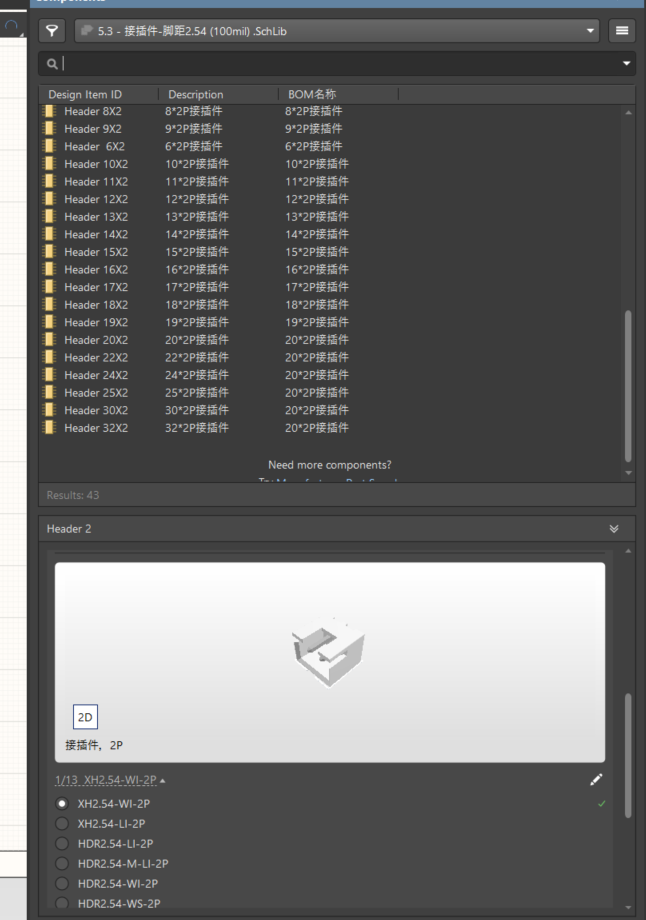

去封装库里找原件

- 注意选择原件时可以改封装类型再拖出来

- 一般排母排针间距都是100mil

- 注意选择原件时可以改封装类型再拖出来

-

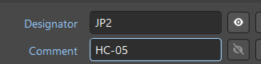

填写好网络标签,改comment并按需求选择是否显示

-

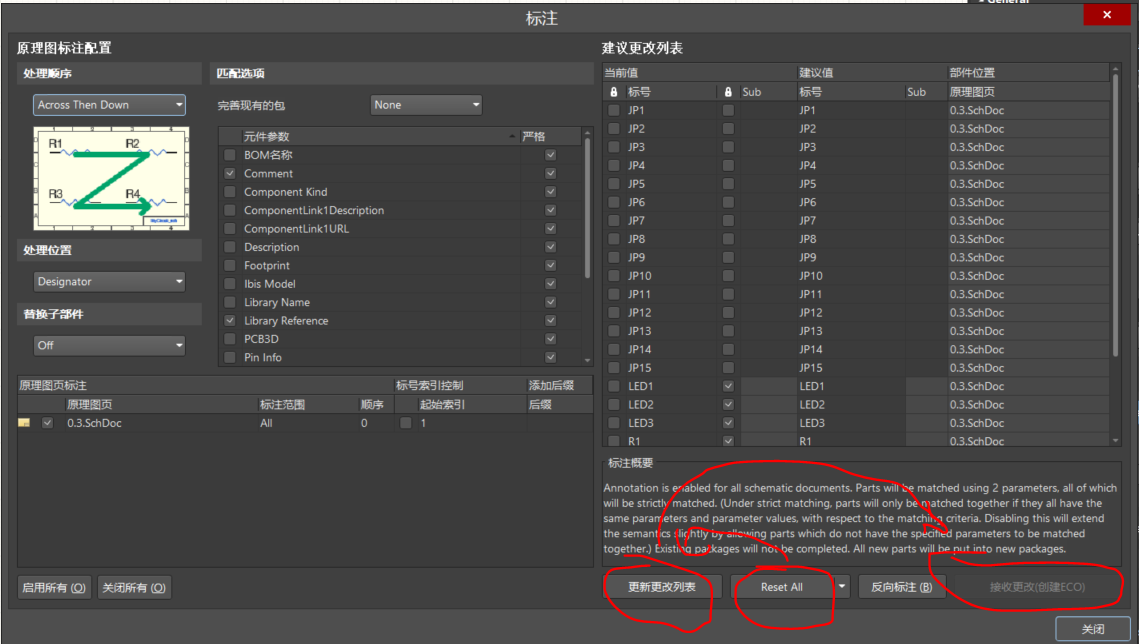

在工具-标注-原理图标注中,

-

打开message(右下角找),看看有什么错误,如那根网络是没接的

-

设计-UpdatePCB文件

-

排布零件,差不多后就画个框然后把多余的板子切了,红底的可以删了

-

开始自动布线-全部(删除自动布线的方案见后面)

-

对着任意线右键,查找相似对象

- GND删除

- VCC类线加粗,从10到20

-

手动看看有没有直角线,把它改曲:具体先放大,按一下那个转角位置,按到了再拖动把转角改大

-

工具-设计规则检查

-

如果短路了就改线,重复第11步,直到出现GND类问题

- 改线:交互式布线和过孔(记得确定是过孔不是焊盘)记得看看层再放线

-

滴泪

-

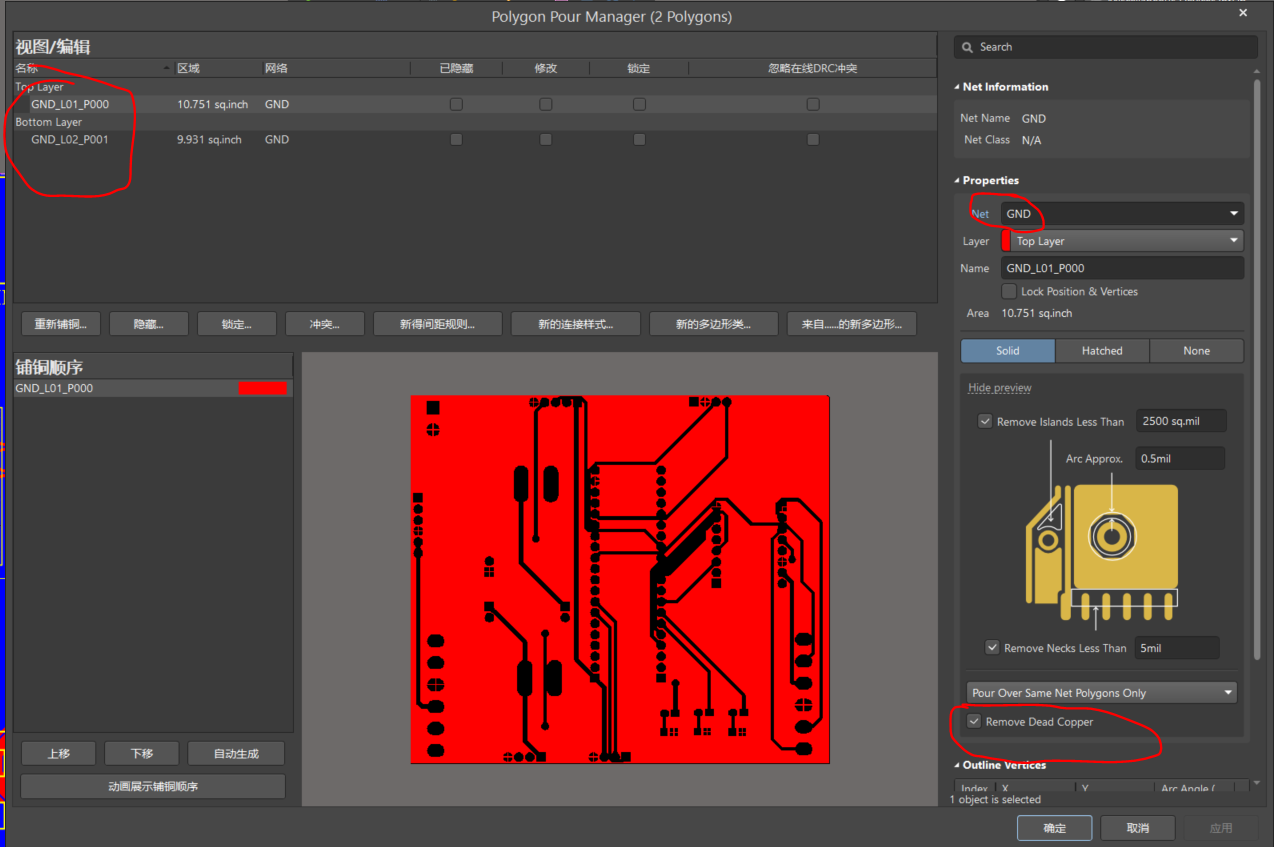

放置,铺铜,沿着边缘一圈,Top和Bottom层都要,改网络为GND,清除死铜(工具-铺铜-铺铜管理器)

如果铺铜后又出现修改的,工具-铺铜-所有铺铜重铺即可

如果铺铜后又出现修改的,工具-铺铜-所有铺铜重铺即可 -

继续重复11-14部直到某次发现设计检查通过(有一种点通不过的见后文)

-

在Top Overlay层进行最终版本号修改,发去打板

注意事项

- 你的PCB图中针座要考虑是否对称(对面的脚对不对)(一个模块两个针座),这个模块是否插得下,方向对不对(比如超声波),是否存在干扰

- 贴片元件只能在相同一面上接线

技巧

原理图:

- 记得你的原理图是用SchLib格式文件的库,并且记得SchLib和PCBLib要一起同时装

PCB:

-

按Q或者视图-切换单位可以从mil到mm

-

明确模块的两脚间距在PCB图上,可以画条线然后改长度然后把元件放线两端中央

-

自动布线的删除可以用

但并非在修改一个元件后必须要全部重新布线

但并非在修改一个元件后必须要全部重新布线 -

铺铜如果爆炸了,删掉铺铜再来一次(或者先选择左下角的重新铺铜,然后会看见很多短路,然后选择重新铺修改的铜)

-

快捷键UUA删自动布线,UAA自动布全部线,DR规则修改,改改规则自动布线很舒服

网络组NetClass

DC快捷键

全选一条线

Ctrl+H,点你要选的导线任意段(焊盘过孔都行)。