原语,即primitive,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,类似于C++中的cout关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT、D触发器、RAM等,相当于软件中的机器语言。在实现过程中的翻译步骤时,要将所有的设计单元都转译为目标器件中的基本元件,否则就是不可实现的。原语在设计中可以直接例化使用,是最直接的代码输入方式,其和DL语言的关系,类似于汇编语言和C语言的关系。

Xilinx公司提供的原语,涵盖了FPGA开发的常用领域,但只有相应配置的硬件才能执行相应的原语,并不是所有原语都可以在任何一款芯片上运行。在Verilog中使用原语非常简单,将其作为模块名直接例化即可。Xilinx的原语按照功能分为10类,包括:计算组件、I/O端组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G比特收发器组件。

FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM (Block Select RAM)的时延和抖动都为最小。

Vivado Utility Buffer中的公用缓冲器:

- IBUFDS (I/O端口组件):用于将差分输入信号转化为标准单端信号,输入为I、IB,一个为主,一个为从,二者相位相反

- OBUFDS (I/O端口组件):将标准单端信号转换成差分信号,输出端口需要直接对应到顶层模块的输出信息。和IBUFDS为一对互逆操作。

- IOBUFDS (I/O端口组件): 具有低电平有效输出的3态差分信号I/O缓冲器

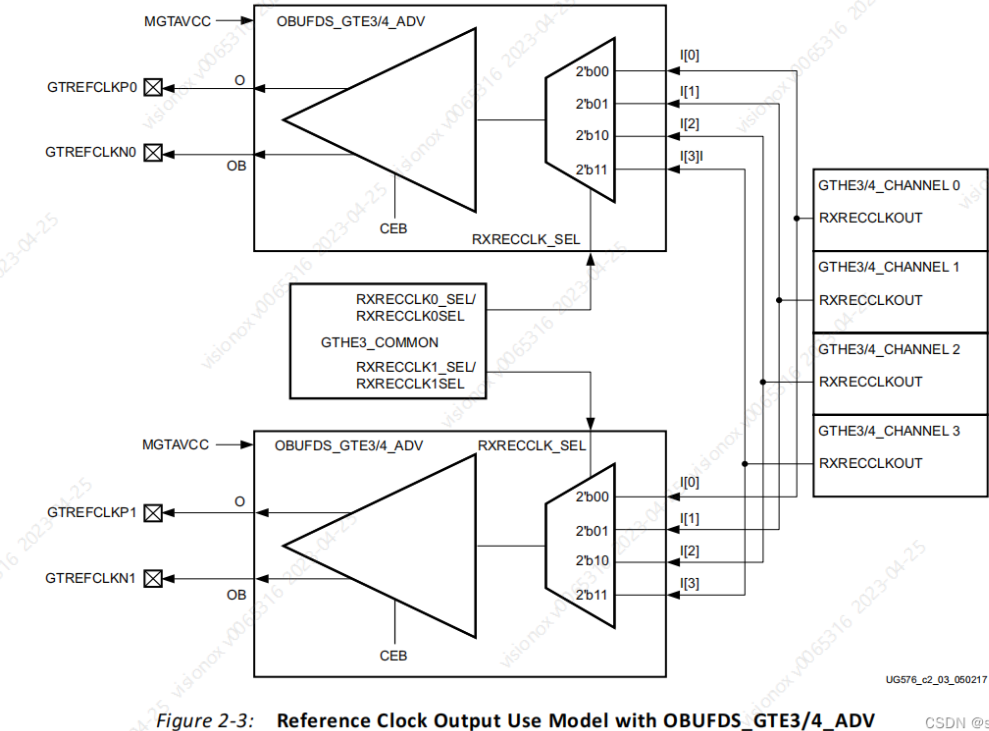

reference clock在GT高速通道中支持输入和输出两种模式。在参考时钟输入模式下,在专用参考时钟I/O引脚上提供一个时钟,用于驱动QPLL或者CPLL,使用IBUFDS_GTE4;参考时钟输出模式下,是从同一QUAD中的四个通道出来的恢复时钟RECLKOUT,可以传到专用的参考时钟I/O引脚,这个输出时钟可以用作不同位置的参考时钟输入,可以使用OBUFDS_GTE3/4和OBUFDS_GTE3/4_ADV。当RECLKout始终来自同一通道时,使用OBUFDS_GTE3/4;当在运行期间发生改变使用OBUFDS_GTE3/4_ADV

- IBUFDSGTE :精确为IBUFDS_GTEx,x=2/3/4,差分缓冲器,用于高速BANK(GTY BANK)的两路参考时钟输入,其中UltraSacle使用IBUFDS_GTE3作为GTY bank的差分缓冲器,UltraScale+采用IBUFDS_GTE4。对于高速BANK,需要使用IBUFDS_GTEx(不同系列的FPGA x的值不同),如果仍然使用IBUFDS,可能会在编译或者生成bit文件时报错,提示时钟约束有问题,约束后可以产生bit文件,但是转出的单端时钟不能使用(正常情况下差分时钟的电平是不需要约束的).使用该原语驱动GTY参考时钟GTREFCLK0和GTREFCLK1,实例化两个IBUFDS_GTE进行驱动。

- OBUFDS GTE:

- OBUFDS GTE ADV

- BUFG:全局缓冲,它的输入是IBUFG的输出,输出到达FPGA内部的IOB、CLB、Block Select RAM的时延和抖动最小

- BUFGCE:带有时钟使能端的全局缓冲

- BUFGCE DIV:有输入端口I、使能CE、清零CLR和输出端口O,可以直接驱动布线轨道和分布轨道,并且可以进行时钟的1-8分频

- BUFG GT: BUFG GT是UltraScale器件中的,需要将IBUFDS_GTE的IBUF_DS_ODIV2扇出连接到BUFG_GT_I的扇入,然后BUFG-GT的输出时钟就和普通BUFG扇出时钟一样,可以用于驱动用户逻辑,也可以用于MMCM/PLL等

- IOBUF:具有低电平有效输出的3态信号I/O缓冲器,一般不用单独添加IBUF和OBUF,因为EDA会自动插入这样的BUF,IBUF的作用就是对普通输入管脚(非时钟)驱动内部信号使用的,OBUF就是内部信号驱动普通输出的。 这里的普通是用于区别于时钟的

- BUFG PS:只有一个输入一个输出的简单时钟缓冲器,属于UltraScale+系列中PS的时钟缓冲器,可以让时钟从PS进入到PL中,布局位置位于PS的旁边。