检查封装

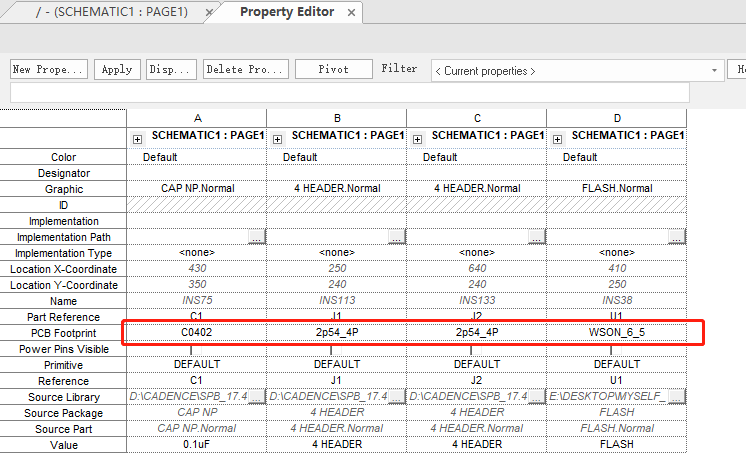

在生成网表前要先确认器件封装和实际封装文件是否对应存在

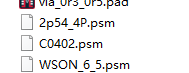

如下是之前设计好的封装文件.psm文件

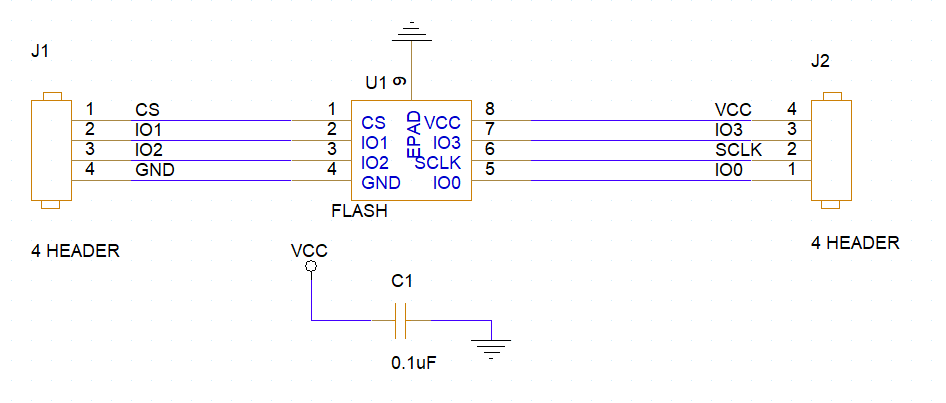

打开orcad,和元件属性中的封装内容对比确认一致

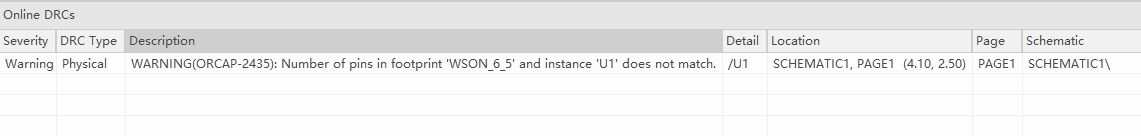

如果实际封装和元器件有不一致的地方,在线DRC会提示错误,例如如下显示封装引脚数和原理图元件引脚数不对应

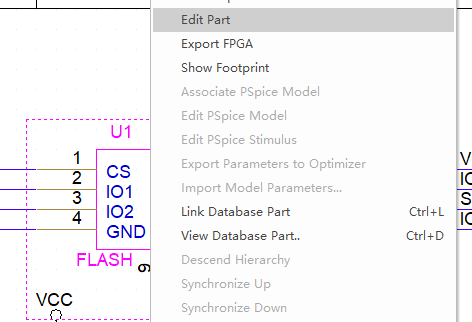

看了下情况,应该是原理图中的flash芯片只画了8个引脚,但实际的封装中EPAD也算一个引脚。所以修改下原理图的元件图案即可

修改好元器件后关掉页面即可,orcad会自动提示你要不要更新到原理图的,修改好后的原理图如下,已经是没有DRC错误了

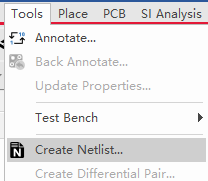

生成网表

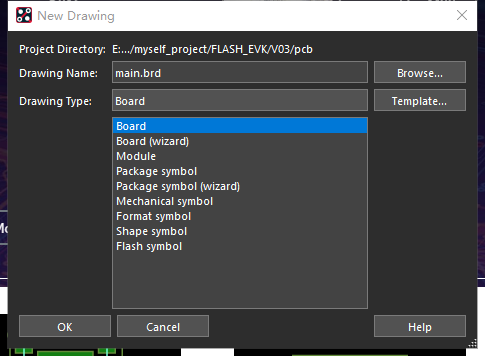

生成网表比较简单,在工具菜单栏直接选择生成网表即可,生成第一方网表无需什么配置

点击导出,默认路径为工程目录下的allegro目录下,一般只要DRC正常的,生成网表都不会有什么问题

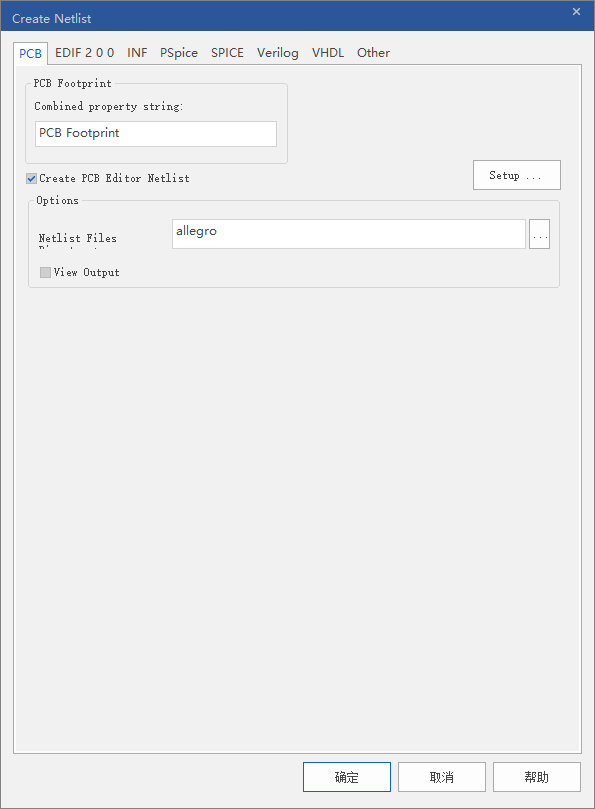

导入网表

导入网表前需要新建好PCB文件,在Allegro中PCB文件格式为.Brd

新建好PCB文件后一般要调整下原点、图纸大小、尺寸等参数,这些和之前设计封装时一样,不再说明。

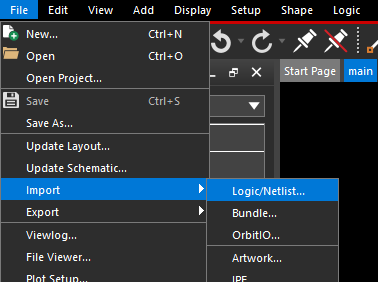

随后点导入网表

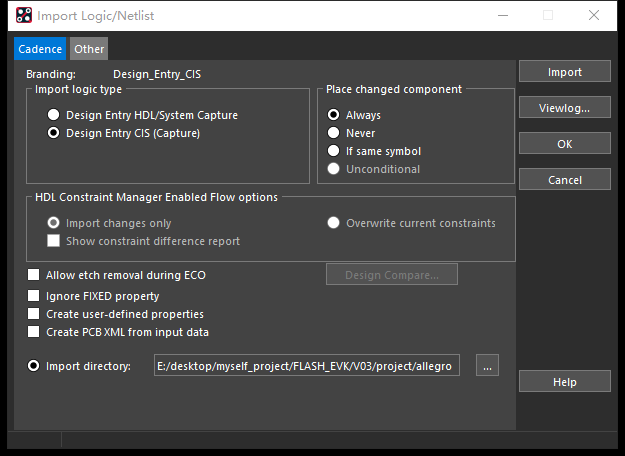

选择导入cis文件,下方选择好之前生成的网表文件的路径

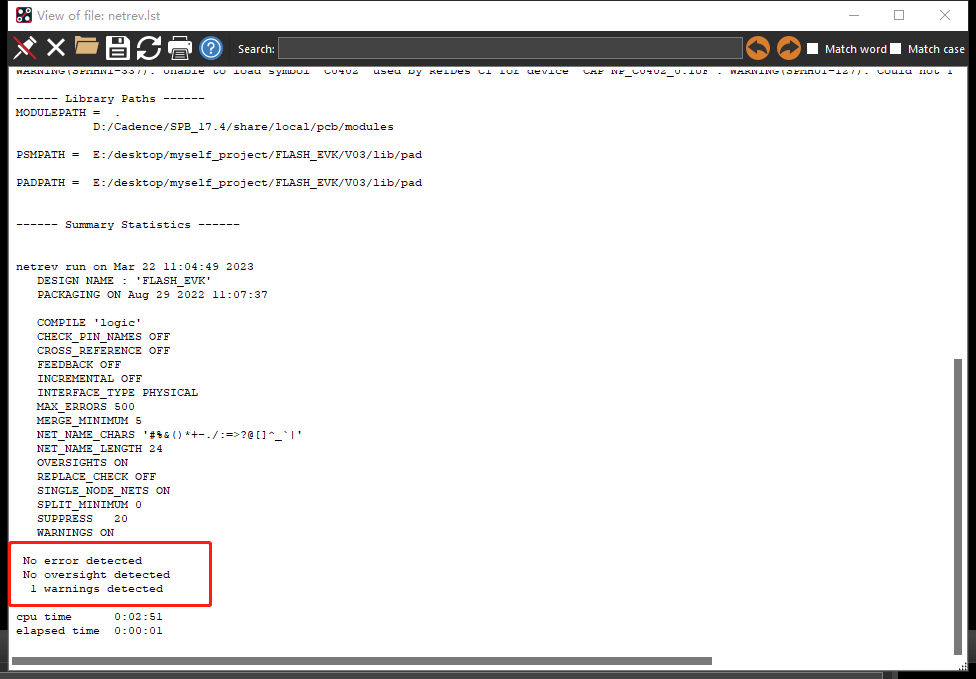

导入后会提示结果,一般只要不是error即可。这里提示有根线的符号名有点问题,可管可不管。

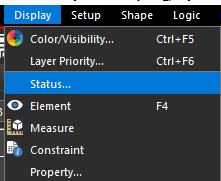

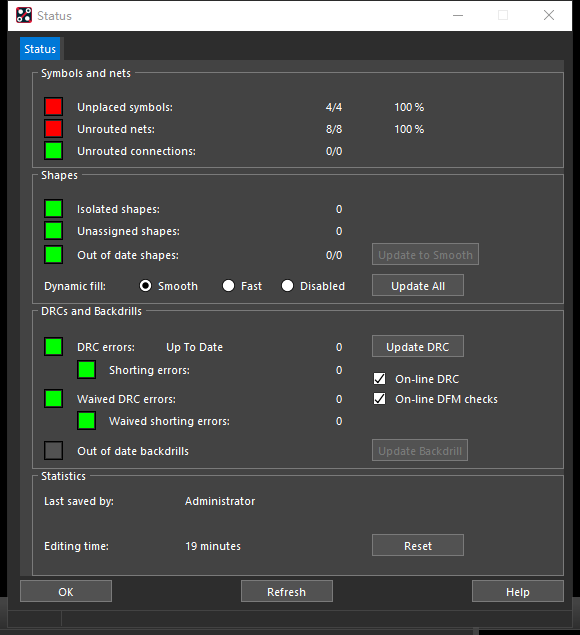

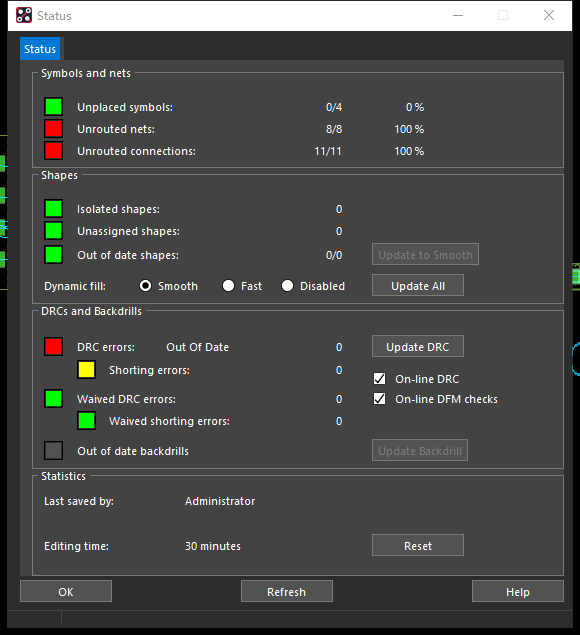

导入后可以查看导入的网络和封装的状态

可以看到,网表虽然导了进去,但是Cadence不会像其他软件那样会自动把器件和飞线也导进去,这个还需要我们自己手动再放置下

放置元件

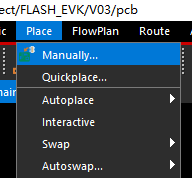

放置元件可以手动放也可以自动放,手动放方法如下:

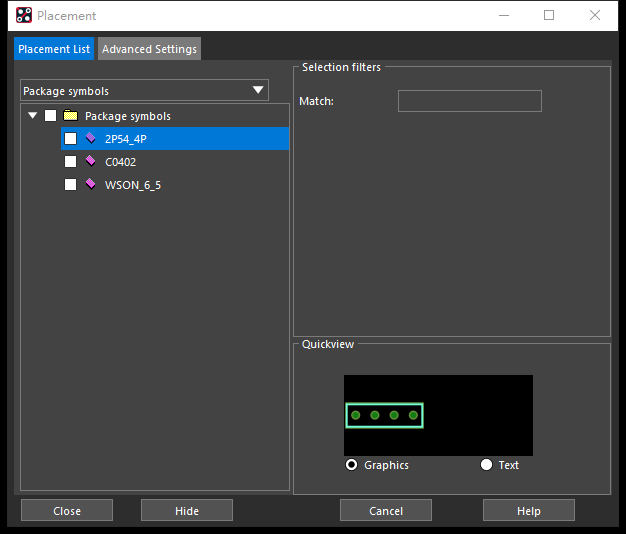

只要之前的path路径设置正确,并且路径下有对应的.psm封装文件和配套的.pad文件,可以在该页面看到之前画好的封装

建议画好封装好用这个方法看看封装生成的文件全不全

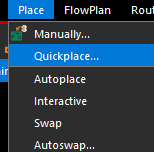

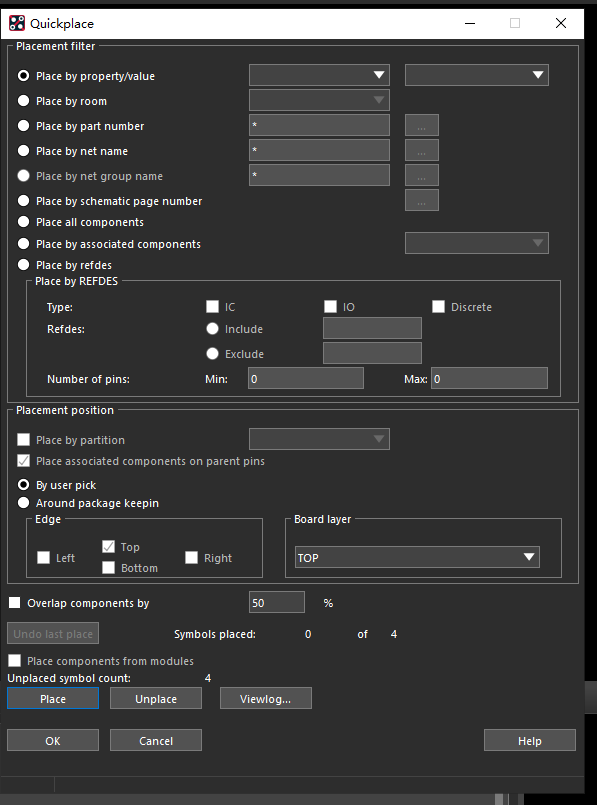

一般项目中实际使用自动放器件的方法(quickplace)

选择按属性放置

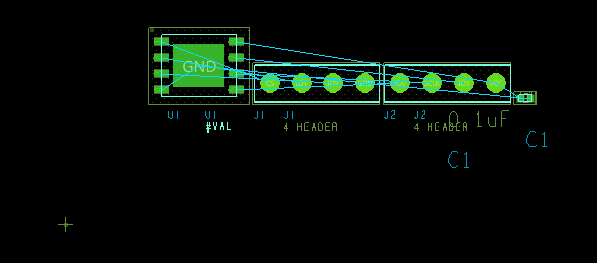

点击place再到图纸空白处点击下就能自动放置好所有器件

重新查看状态就能看到器件已经放好了

下一步就可以开始进行布局和走线了