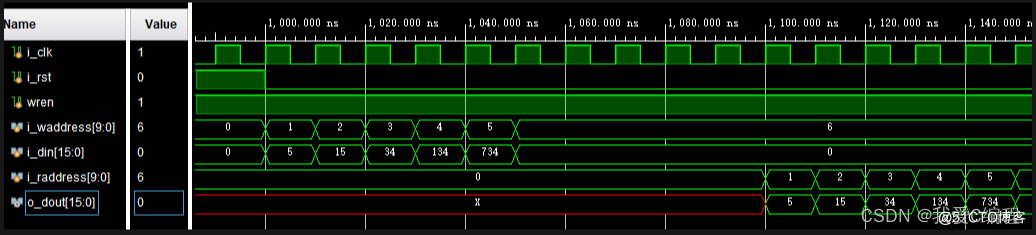

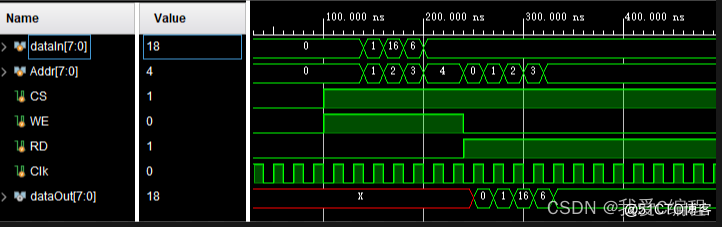

1.算法仿真效果

本系统进行了Vivado2019.2平台的开发,Vivado2019.2仿真结果如下:

ram

SRAM

2.算法涉及理论知识概要

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,具有可重构性、高速度、低功耗等特点,被广泛应用于数字电路设计、信号处理、图像处理等领域。在FPGA中,实现各类存储器是非常重要的任务之一。存储器是计算机系统中的重要组成部分,用于存储程序和数据。在FPGA中,存储器包括RAM(Random Access Memory)、SRAM(Static Random Access Memory)等。本文将从专业角度详细介绍基于FPGA的各类存储器的实现步骤和数学原理。

2.1、RAM的实现步骤

RAM是一种随机读写存储器,可以随机读取和写入存储单元中的数据。在FPGA中,RAM可以使用两种不同的实现方式:基于LUT的RAM和基于Block RAM的RAM。基于LUT的RAM使用LUT(Look-Up Table)实现存储器的单元。每个存储单元包含一个LUT和一个D触发器。LUT中存储了一个地址和对应的数据,D触发器用于保存LUT中的数据。实现基于LUT的RAM的步骤如下:

(1)定义RAM的大小和数据宽度。

(2)使用LUT作为存储器单元,每个单元包含一个LUT和一个D触发器。

(3)使用地址选择器选择需要访问的存储单元。

(4)使用数据选择器选择需要读取或写入的数据。

(5)使用时钟信号控制D触发器的读写操作。

基于Block RAM的RAM使用FPGA中的Block RAM实现存储器的单元。每个存储单元包含一个Block RAM和一个地址选择器。实现基于Block RAM的RAM的步骤如下:

(1)定义RAM的大小和数据宽度。

(2)使用FPGA中的Block RAM作为存储器单元。

(3)使用地址选择器选择需要访问的存储单元。

(4)使用数据选择器选择需要读取或写入的数据。

(5)使用时钟信号控制Block RAM的读写操作。

2.2、SRAM的实现步骤

SRAM是一种静态随机读写存储器,可以在不刷新的情况下保持存储单元中的数据。在FPGA中,SRAM可以使用两种不同的实现方式:基于LUT的SRAM和基于Block RAM的SRAM。

基于LUT的SRAM使用LUT实现存储器的单元。每个存储单元包含一个LUT和一个D触发器。LUT中存储了一个地址和对应的数据,D触发器用于保存LUT中的数据。实现基于LUT的SRAM的步骤如下:

(1)定义SRAM的大小和数据宽度。

(2)使用LUT作为存储器单元,每个单元包含一个LUT和一个D触发器。

(3)使用地址选择器选择需要访问的存储单元。

(4)使用数据选择器选择需要读取或写入的数据。

(5)使用时钟信号控制D触发器的读写操作。

基于Block RAM的SRAM使用FPGA中的Block RAM实现存储器的单元。每个存储单元包含一个Block RAM和一个地址选择器。实现基于Block RAM的SRAM的步骤如下:

(1)定义SRAM的大小和数据宽度。

(2)使用FPGA中的Block RAM作为存储器单元。

(3)使用地址选择器选择需要访问的存储单元。

(4)使用数据选择器选择需要读取或写入的数据。

(5)使用时钟信号控制Block RAM的读写操作。

RAM和SRAM的实现都涉及到存储器单元的读写操作和地址选择器的设计。

存储器单元的读写操作

存储器单元的读写操作是通过时钟信号控制的。在RAM和SRAM中,每个存储单元都包含一个D触发器,用于保存读取或写入的数据。D触发器的输出Q表示存储单元中保存的数据。D触发器的输入D表示需要写入的数据或需要读取的数据。时钟信号控制D触发器的读写操作。具体地,当时钟信号为上升沿时,D触发器将输入D的值保存在Q中,实现写操作;当时钟信号为下降沿时,D触发器输出Q的值,实现读操作。

地址选择器的设计

地址选择器用于选择需要访问的存储单元。在RAM和SRAM中,地址选择器通常使用多路选择器(Multiplexer)实现。多路选择器的输入包括需要访问的存储单元的地址和需要写入或读取的数据,输出为选择的数据。具体地,多路选择器的选择信号为需要访问的存储单元的地址,输入信号为需要写入或读取的数据,输出信号为选择的数据。

存储器的容量和速度

RAM和SRAM的容量和速度是设计存储器时需要考虑的重要因素。容量指存储器可以存储的数据量,速度指存储器的读写速度。在FPGA中,RAM和SRAM的容量和速度可以通过调整存储器单元的大小和时钟频率进行优化。具体地,增加存储单元的大小可以提高存储器的容量,增加时钟频率可以提高存储器的速度。但是,在增加存储单元的大小和时钟频率时需要考虑到FPGA的资源限制和功耗消耗等问题。

3.Verilog核心程序

module TEST_tops_sram();

reg [7:0] dataIn;

reg [7:0] Addr;

reg CS;

reg WE;

reg RD;

reg Clk;

// Outputs

wire [7:0] dataOut;

// Instantiate the Unit Under Test (UUT)

tops_sram uut (

.dataIn(dataIn),

.dataOut(dataOut),

.Addr(Addr),

.CS(CS),

.WE(WE),

.RD(RD),

.Clk(Clk)

);

initial begin

// Initialize Inputs

dataIn = 8'h0;

Addr = 8'h0;

CS = 1'b0;

WE = 1'b0;

RD = 1'b0;

Clk = 1'b0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

dataIn = 8'h0;

Addr = 8'h0;

CS = 1'b1;

WE = 1'b1;

RD = 1'b0;

#20;

dataIn = 8'h0;

Addr = 8'h0;

#20;

dataIn = 8'h1;

Addr = 8'h1;

#20;

dataIn = 8'h10;

Addr = 8'h2;

#20;

dataIn = 8'h6;

Addr = 8'h3;

#20;

dataIn = 8'h12;

Addr = 8'h4;

#40;

Addr = 8'h0;

WE = 1'b0;

RD = 1'b1;

#20;

Addr = 8'h1;

#20;

Addr = 8'h2;

#20;

Addr = 8'h3;

#20;

Addr = 8'h4;

end