目录

一.SRAM存储单元结构

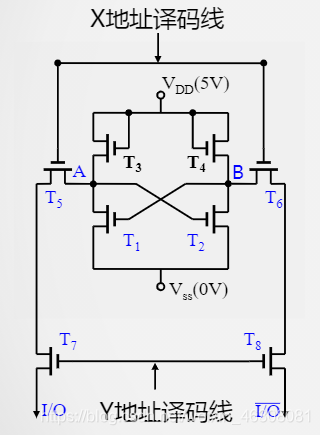

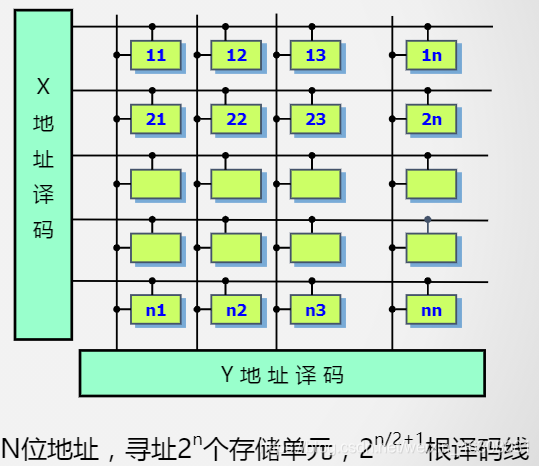

(1)结构图(双译码X+Y)

六管静态存储单元结构(每个管都处于饱和导通状态或者截止状态)

T1、T2为工作管,用来保存\存储数据

T3、T4为负载管,用于为T1、T2提供电荷

T5、T6、T7、T8为门控管,用于控制开关

(2)SRAM存储单元工作原理

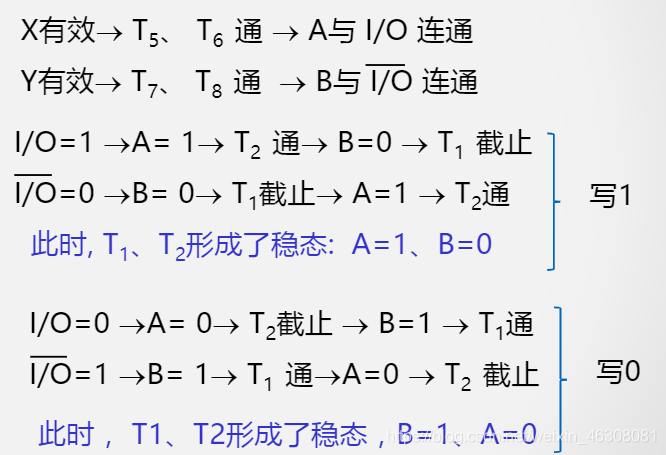

X地址选通(行选通)

T5、T6管被打开,A、B与位线连通

Y地址选通(列选通)

T7、T8管被打开,A、B分别于I/O 和 非I/O 相连通

【1】写过程

对于I/O=1时的结果分析:

当I/O=1时,A=1,此时T2处于饱和导通状态,因为T2接地而且B与T2相连,所以B=0

当B=0时,T1与B相连,所以此时T1也为0,T1为0可以使A保持高电平的状态,形成稳定的互锁状态

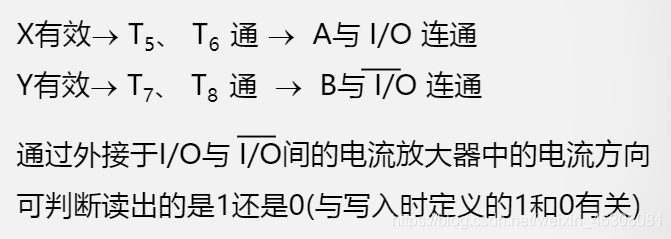

【2】读过程

当A点读入的值为1时,读出结果即I/O结果也为1

当A点读入的值为0时,读出结果即I/O结果也为0

B点同理

注意: 不论是读或写,都要求X和Y译码线同时有效!

【3】保持过程

当X和Y撤销后,由负载管T3、T4分别为T1、T2提供工作电流,保持此互锁状态。

二.静态存储器的结构

(1)单译码结构

若干个存储单元通过存储器的地址译码线来选通它的门控管

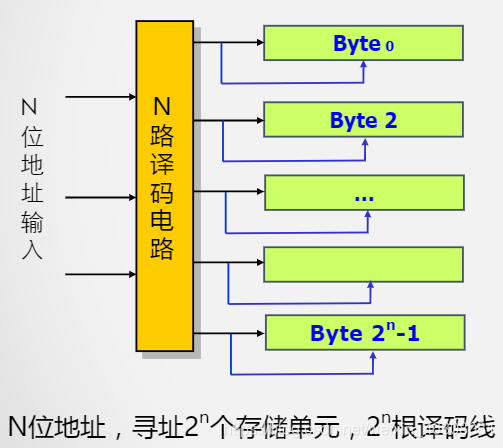

(2)双译码结构

X的译码输出作为这一行所有的行选通信号,Y的译码输出作为这一列所有的列选通信号

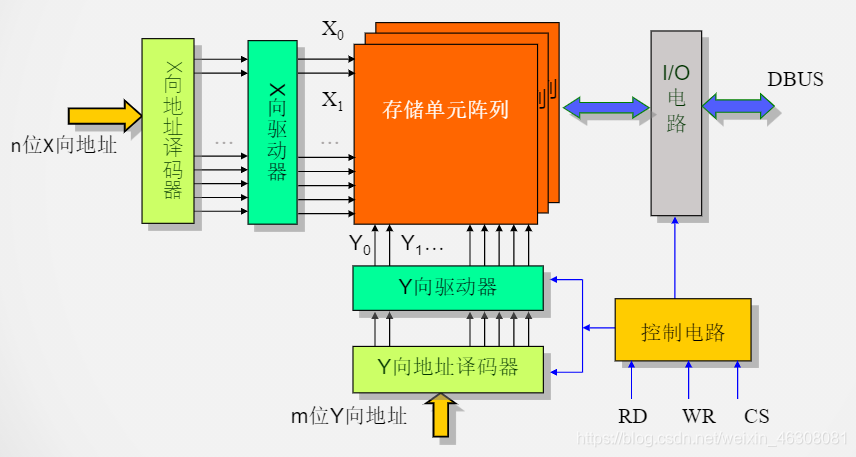

(3)采用双译码的静态存储器结构

上面提到的双译码结构就是图中的存储单元阵列

X和Y的位数可能不相同,均需要通过驱动器进行扩大

还有控制电路,分为读信号RD、写信号WR和片选信号CS,当片选信号有效时才可以进行其他操作。

三.例题

(1) 某计算机字长16位,其存储器容量为64KB,按字编址时,其寻址范围是多少?

【1】存储容量为64KB时,按字节编址的寻址范围就是64KB

【2】当按字编址时,因为一个字有8位,所以结果为 64K × 8 / 16 = 32K

(2) 一个16K*32位的SRAM存储芯片,其数据线和地址线之和为多少?

该存储芯片为16K*32位,那么16K为24×210,即它需要的数据线为4+10=14根。此外它还需要32根地址线,所以数据线和地址线的总和为46。

(3) 一个16K*32位的SRAM存储芯片,其内部采用位数相同的行列地址译码器,则其内部译码输出线的总量为多少?

【1】16K的存储单元需要的译码输入线为:24×210即14位。

【2】因为它采取位数相同的行列地址译码器,所以行列各7位,那么需要的译码输出线为 27 + 27 = 28 。即结果为28。

【3】拓展:当采用单译码方式时,译码输出线为 24×210 = 214

一、自适应逻辑块(ALM)

最近在看Cyclone V 代 FPGA 芯片手册,网上的资料就是把中文手册抄一遍或者是把英文手册翻译一下,不讲解细节以及应用,所以想发一篇从手册中电路出发到实际应用对应的电路到底会消耗什么资源。不管是 altera 、 xilimx 还是国产的芯片,这些原理都是一致的。

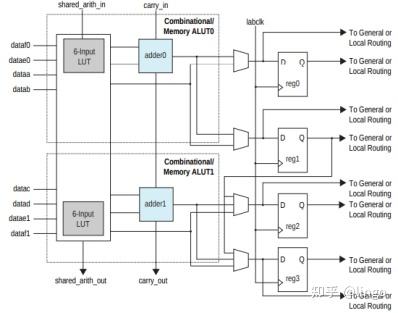

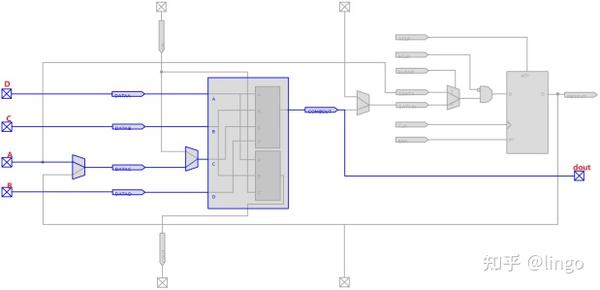

图1 Cyclone V 器件的 ALM 高级结构图

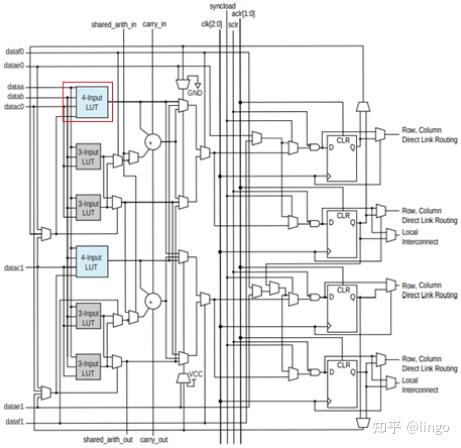

本来查找表原理是比较简单的,当然要将内部结构一次搞清楚。打开图 1内部详细电路如图 2 所示,想要一次说清楚好像有亿点复杂。6 输入查找表是由 2 个 4 输入查找表和 4 个 3 输入查找表加一些数据选择器构成的,本节就先了解一下图 2 中红色部分 4 输入查找表(LUT),由于Cyclone IV、Cyclone 10 LP这些芯片的查找表均为 4 输入,其实几输入的原理都一样,只是 SRAM 地址端个数不同而已。

图2 Cyclone V 器件的 ALM 内部详细结构

二、查找表实现任意逻辑的原理

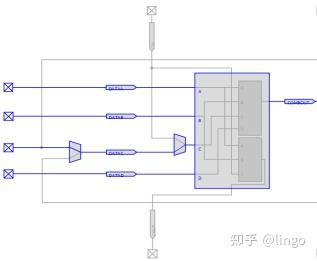

FPGA 可以实现所有门电路,然而 FPGA 却没有门电路这种硬件结构,都是通过一个叫查找表的结构等效实现的。本节内容解决一个查找表凭什么可以综合成任何门电路。下图蓝色边缘的方框就是一个四输入的查找表,四个输入端 a、b、c、d,一个输出端。

图3 查找表外部结构图

⼀个查找表(LUT)可以实现与门、或门、⾮门、加减法等各种组合逻辑。试想一下,n个输入,最多可以组合成 2n 个不同的状态,输出也就要与 2n 个输入状态对应。当查找表在实现固定功能时,输入信号确定时,输出信号也是确定的,只需要先把输入对应的输出结果计算并存储起来,把输入信号作为存储区的地址信号,读出的数据就是对应的输出数据了。

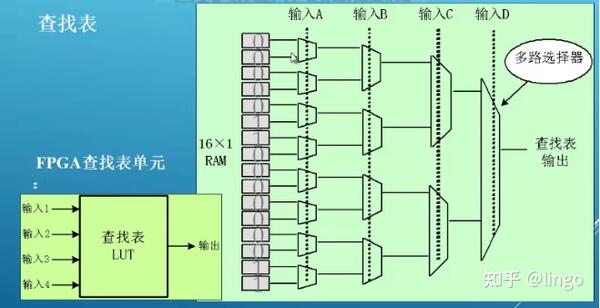

如图 4 所示,4 输入 LUT 实际有 16 个 1bit 基于 SRAM 结构的存储器,将A、B、C、D 四个输⼊作为 SRAM 存储器的地址信号,输出该地址存储的数据。SRAM 存储的数据不同,相同的输入可以得到不同的输出,从而等效成不同门电路,实现使⽤⼀个 LUT 实现各种组合逻辑的功能。

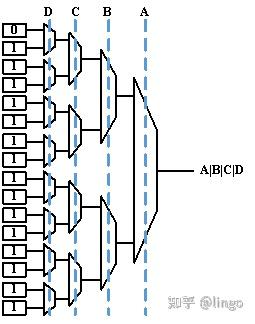

图4 4输入查找表内部组成

例如要实现 A|B|C|D 运算,则该运算只有当 A、B、C、D 同时为 0 时,输出为 0,其余时间输出均为 1。加⼊规定当数据选择端输⼊低电平时,数据选择器的上⾯输⼊端与输出端导通,当数据选择端输⼊⾼电平时,数据选择器的下⾯输⼊端与输出端导通,则查找表应如图 5 所⽰:

图5 4 输入查找表实现四输入或门

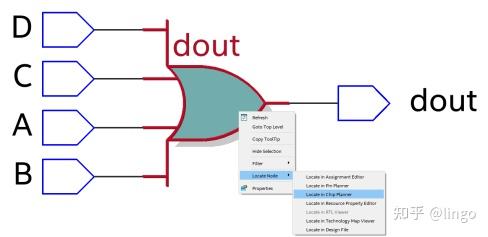

Quartus 在对模块进行综合时,就会生成每个查找表每bit SRAM需要存储的数据,在下载程序或者上电配置时,FPGA查找表对应的SRAM就会被初始化,之后这些查找表就可以等效成对应的门电路了,通过下面代码实现上述电路。

module top ( input A, input B, input C, input D, output dout ); assign dout = A | B | C | D; endmodule综合的RTL视图如下所示,右击打开chip planner查看该或门在芯片内的位置,以及实现方式。

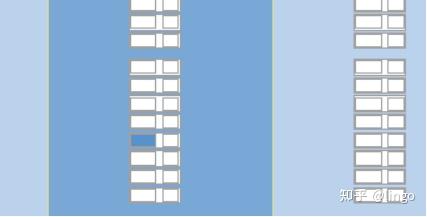

图6 4 四输入或门的RTL视图

图7 Chip planner中对应的查找表所在的LE

图8 查找表实现4输入或门

由于查找表是最基本结构,quartus无法在对其进行展开,无法查看更加细节的电路,而vivado是可以导出lut的网表,可以看到lut的ram里面存储的数据,会更加直观。

三、总结及扩展

对 xilimx、altera 等厂家的 FPGA 进⾏编程,实际上就是把需要进⾏运算的结果计算出来并存储在 SRAM 之中,输⼊发⽣相应变化时,将 RAM 中对应值输出即可。⼀个 N 输⼊查找表(LUT)可以实现 N 个输⼊变量的任何逻辑功能,如 N 输⼊“与”、N 输⼊“异或”等。输⼊多于 N 个的函数、⽅程必须分开⽤⼏个查找表(LUT)实现,这个过程由 quartus 、vivado 等综合软件⾃动完成。

从前面查找表原理有人也会想到,查找表最基本的结构是 SRAM,除了能够用来实现门电路,加减法等组合逻辑之外,还可以作为存储体使用。FPGA 的 RAM 分为两部分,一部分是块 RAM,在 Cyclone IV 里面叫 M9K,在 Cyclone V 系列里面升级为 M10K 存储体。另一部分叫分布式 RAM,查找表就属于分布式 RAM,一般情况下,块 RAM 读写速度会比分布式 RAM 高,所以在实现 FIFO、ROM、双口 RAM 这些存储体 IP 时,一般会选择使用块 RAM 资源,后面到存储体时在详细说。

英伟达的高端GPU都已经不能卖给我们了,还不知道哪天 xilimx、altera 的高端 FPGA 是否也会禁止出售给我们,不管是国内 FPGA 芯片还是 EDA 软件,与其差距实在太大,无法奢求他们能在短期时间内赶上国外厂家。所以除了会写程序之外,还是要了解底层原理,这样才能更好的优(ya)化(zha) FPGA 资源。

需要 Cyclone IV、Cyclone V 代 FPGA中英文手册的在gongzhonghao回复 Cyclone即可。