什么是跨时钟域的概念呢?

在一个电路中launch的时钟和capture时钟,如果不是同一个时钟呢?就是跨时钟域的电路

若两个时钟是同步时钟呢,那这个就叫同步时钟域

若两个时钟是异步呢时钟呢,那就是异步时钟域,也就是异步跨时钟域电路。

看这张图。这是clock a的domain,这是clock b的doamin。它们之间有个逻辑的连接关系。launch时钟是clock a,capiture时钟是clock b,那么这就是一个跨时钟域的电路。

如果clock a clock b是异步关系呢?那就是异步时钟域电路。

跨时钟域的例子在现实设计中有非常多,比如UART的接收器\USB\整个soc里面有多个不同的时钟。那么,这几个时钟可能有逻辑的关系,这时候就存在跨时钟域电路的关系。

跨时钟域有什么问题呢?

跨时钟率的设计极大的影响你芯片的功能,甚至影响芯片的可靠性和稳定性。

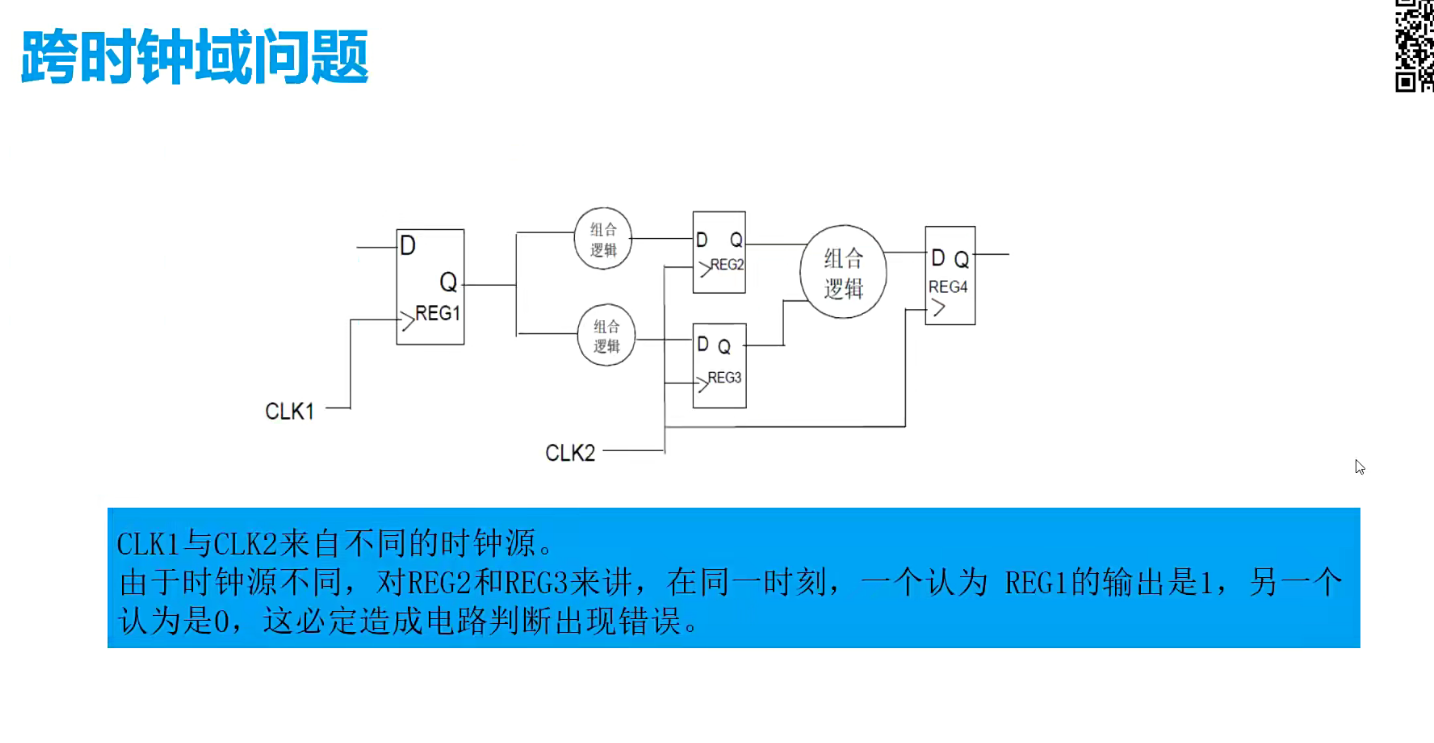

上图中,有clock 1,寄存器reg 1,有clock 2,锁存reg 2 reg 3。然后呢,再经过组合逻辑送到reg 4。reg 1的输出经过两个分支。组合逻辑分别送给reg 2和reg 3。那这里面有个问题,如果clock 1 clock 2,它来自于不同的时钟源。由于时钟源不同,对reg 2和rag 3来讲,在同一时刻,一个认为一输出的是1,另一个认为是0。也就是说,因为它们是不同源的,所以这个信号什么时候送到这个地方是不确切的,没有相位的关系。那这个delay的大小也是不一定的,这样必定会导致电路的判断出现错误。

这就是一个非常典型的跨时钟域的出现错误的例子。那么,粗略的看,如果没有任何延迟信息,又或者是说它们的相位关系认为问题不是很大的话,那么极有可能这个电路没有什么问题.就这个功能来执行,但是在实际工作中,恰恰在某些时候会出现功能的错误。