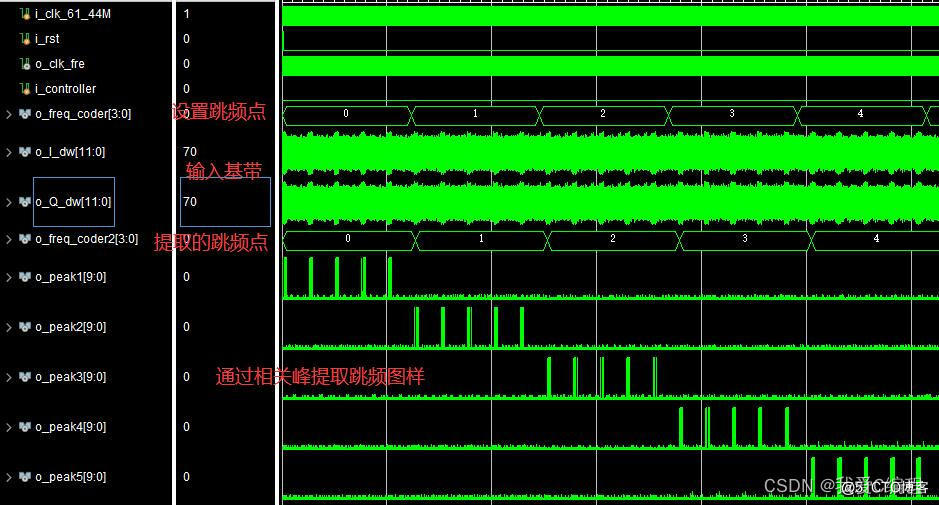

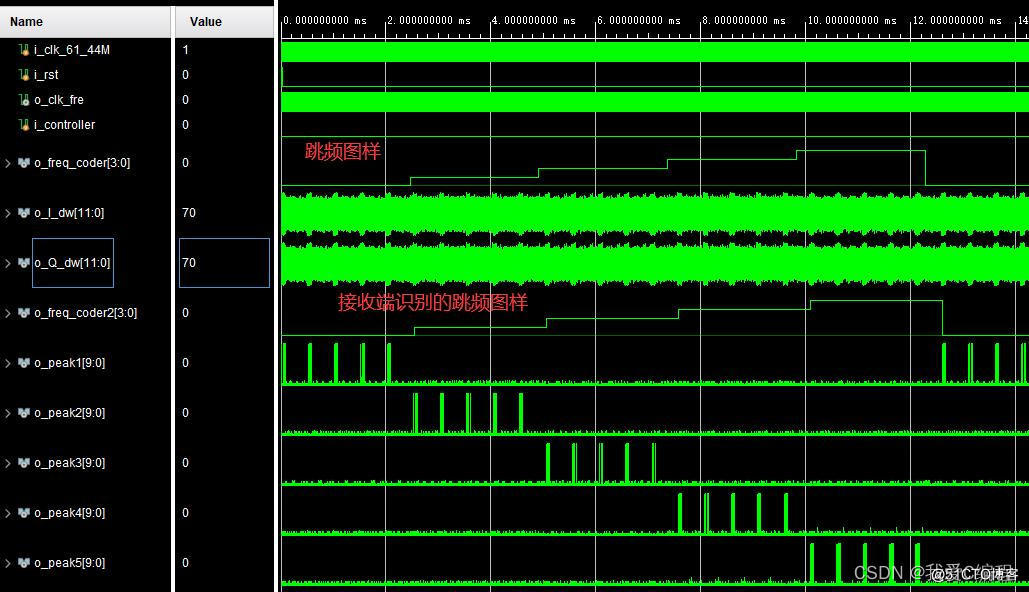

1.算法仿真效果

Vivado2019.2仿真结果如下:

本案例通过不同的跳频同样,在基带数据中插入不同的PN序列,然后在接收到,基于PN序列相关峰的检测识别,来判决当前基带数据对应的跳频图样实现跳频通信。这里数据是基于基带数据来进行测试的。

2.算法涉及理论知识概要

插入导频: 跳频信号在传输过程中可能会经历频率变化,这使得信号的频谱随时间变化。为了帮助识别信号的频率,我们在跳频信号中插入导频序列。导频序列是预先知道的、不随时间变化的信号,它可以用来估计信号的频率偏移。

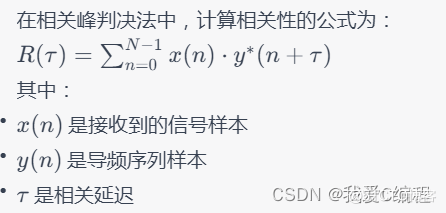

相关峰判决法: 跳频图样识别基于导频序列的相关峰。在收到信号后,首先通过相关操作计算信号与导频序列之间的相关性。当信号的频率与导频序列的频率相匹配时,相关性峰值最高。通过检测相关性峰值,我们可以判断信号是否匹配特定的跳频图样。

具体实现步骤如下:

导频序列插入: 在发送端,将预先知道的导频序列插入跳频信号的特定位置。这些位置通常是在跳频图样的变化点。

信号接收: 接收端收到信号。

相关计算: 对接收到的信号与导频序列进行相关计算。通过对不同相关延迟进行计算,得到相关峰。

相关峰检测: 在相关峰函数中,检测最高的相关性峰值。该峰值对应于信号的频率与导频序列频率相匹配的情况。

判决: 根据相关峰值的存在与否,以及峰值的位置,来判断接收到的信号是否与特定的跳频图样匹配。

通过这个过程,基于插入导频相关峰判决法的基带信号跳频图样识别可以实现对跳频信号的快速、准确的识别。这种方法在跳频通信系统中具有重要的应用,能够有效地解决跳频信号的频率偏移问题,提高信号识别的可靠性。

3.Verilog核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/04/22 15:13:09

// Design Name:

// Module Name: tops

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tops(

i_clk_61_44M,//输入时钟

i_rst, //复位

o_clk_fre,

i_controller,

o_freq_coder,

o_I_dw,

o_Q_dw,

o_freq_coder2,

o_peak1,

o_peak2,

o_peak3,

o_peak4,

o_peak5

);

input i_clk_61_44M;

input i_rst;

output o_clk_fre;

input i_controller;

output[3:0]o_freq_coder;

output signed[11:0]o_I_dw;

output signed[11:0]o_Q_dw;

output[3:0] o_freq_coder2;

output signed[9:0]o_peak1;

output signed[9:0]o_peak2;

output signed[9:0]o_peak3;

output signed[9:0]o_peak4;

output signed[9:0]o_peak5;

wire clk_61_44M;

wire clk_15_36M;

wire clk_7_68M;

clk_wiz_0 clk_wiz_0_u

(

// Clock out ports

.clk_out1(clk_61_44M), // output clk_out1

.clk_out2(clk_15_36M), // output clk_out2

.clk_out3(clk_7_68M), // output clk_out3

// Status and control signals

.reset (1'b0), // input reset

.locked (), // output locked

// Clock in ports

.clk_in1 (i_clk_61_44M)

);

assign o_clk_fre=clk_15_36M;

wire signed[11:0]w_I_dw1;

wire signed[11:0]w_Q_dw1;

wire signed[11:0]w_I_dw2;

wire signed[11:0]w_Q_dw2;

wire signed[11:0]w_I_dw3;

wire signed[11:0]w_Q_dw3;

wire signed[11:0]w_I_dw4;

wire signed[11:0]w_Q_dw4;

wire signed[11:0]w_I_dw5;

wire signed[11:0]w_Q_dw5;

signal_f1 signal_f1_u(

.i_clk (o_clk_fre),

.i_rst (i_rst),

.o_I_dw(w_I_dw1),

.o_Q_dw(w_Q_dw1)

);

signal_f2 signal_f2_u(

.i_clk (o_clk_fre),

.i_rst (i_rst),

.o_I_dw(w_I_dw2),

.o_Q_dw(w_Q_dw2)

);

signal_f3 signal_f3_u(

.i_clk (o_clk_fre),

.i_rst (i_rst),

.o_I_dw(w_I_dw3),

.o_Q_dw(w_Q_dw3)

);

signal_f4 signal_f4_u(

.i_clk (o_clk_fre),

.i_rst (i_rst),

.o_I_dw(w_I_dw4),

.o_Q_dw(w_Q_dw4)

);

signal_f5 signal_f5_u(

.i_clk (o_clk_fre),

.i_rst (i_rst),

.o_I_dw(w_I_dw5),

.o_Q_dw(w_Q_dw5)

);

jump_frequency jump_frequency_u(

.i_clk (o_clk_fre),

.i_rst (i_rst),

.i_controller (i_controller),

.i_freqset (4'b0010),

.o_freq_coder (o_freq_coder)//输出跳频带你

);

reg signed[11:0]o_I_dw;

reg signed[11:0]o_Q_dw;

always @(posedge o_clk_fre or posedge i_rst)

begin

if(i_rst)

begin

o_I_dw <= 12'd0;

o_Q_dw <= 12'd0;

end

else begin

if(o_freq_coder == 4'b0000)//根据不同的频点,插入不同的序列,接收端根据序列类型判决频点

begin

o_I_dw <= w_I_dw1;

o_Q_dw <= w_I_dw1;

end

if(o_freq_coder == 4'b0001)

begin

o_I_dw <= w_I_dw2;

o_Q_dw <= w_I_dw2;

end

if(o_freq_coder == 4'b0010)

begin

o_I_dw <= w_I_dw3;

o_Q_dw <= w_I_dw3;

end

if(o_freq_coder == 4'b0011)

begin

o_I_dw <= w_I_dw4;

o_Q_dw <= w_I_dw4;

end

if(o_freq_coder == 4'b0100)

begin

o_I_dw <= w_I_dw5;

o_Q_dw <= w_I_dw5;

end

end

end

jump_check jump_check_u(

.i_clk (o_clk_fre),

.i_rst (i_rst),

.i_I_dw (o_I_dw),

.i_Q_dw (o_Q_dw),

.o_freq_coder(o_freq_coder2),

.o_peak1 (o_peak1),

.o_peak2 (o_peak2),

.o_peak3 (o_peak3),

.o_peak4 (o_peak4),

.o_peak5 (o_peak5)

);

endmodule