最后修改日期:2023/10/13

简介

在CMOS模拟版图中,常常用Guard Ring将若干个MOS管(一般来说,一个Gurad Ring内部的MOS管都是同型的,即都是PMOS/NMOS)包围起来,起到保护作用。在芯片layout设计时,在面积允许的情况下要多放置一些Guard Ring,以提高芯片的性能。

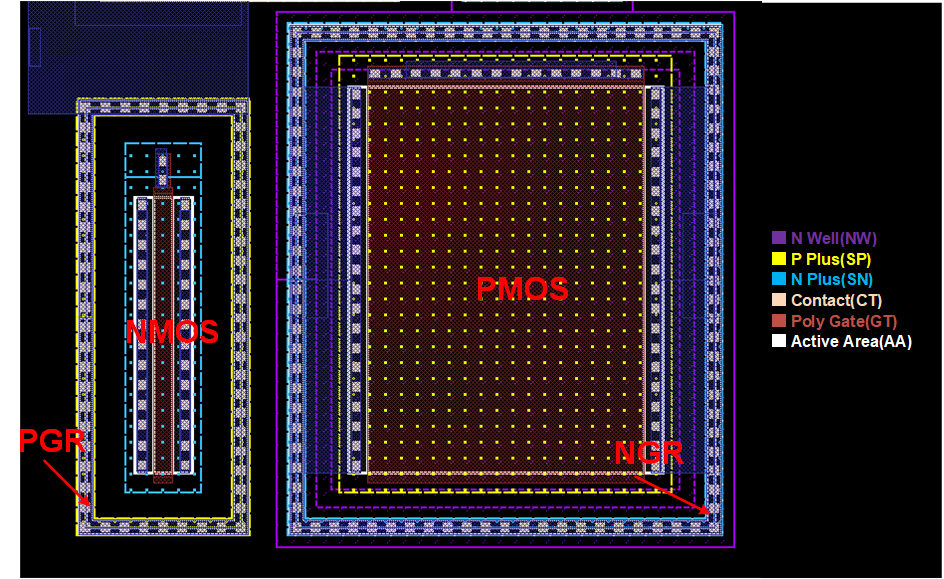

Guard Ring在layout中的形式

一般CMOS工艺的特点

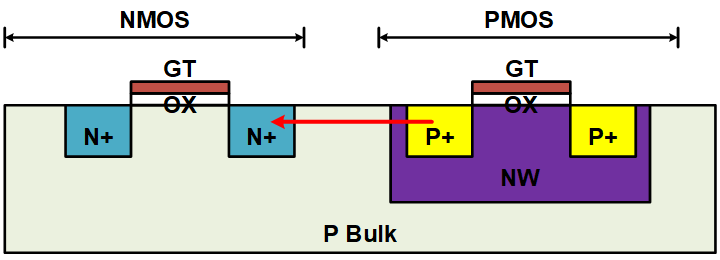

在一般的CMOS工艺中,整个基底都是P型半导体,所以制作NMOS直接在基底上制作。而PMOS的基底是N型的,因此需要先在巨大的P型基底上先制作N阱(N Well),再在N阱中制作PMOS。

-

Active Area就是会生成MOS的区域。AA与GT相交就构成一个MOS。但是实际上在工艺中AA代指什么还不确定,因为不确定工艺的隔离工艺是什么。我的推测是:MOS的硅区与上方的Metal之间总是有氧化层的,而AA位置对应的氧化层较薄,因此GT能对AA区的硅形成控制。这个做法类似于STI或者LOCOS工艺。

-

Contact是接触孔,可以理解为连接Active Area和Metal 1,也即通过Contact可以控制一块Active Area的电平。

P Gurad Ring(PGR)

P Guard Ring用来保护NMOS器件。PGR本身由SP中的AA组成,CT是用来控制PGR的电平的(一般为VSS)。

N Gurad Ring(NGR)

又称Well Guard Ring,因为其由SN中的AA组成,而SN必须存在于NW中。CT作用同理,电平一般为VDD。

闩锁效应/可控硅效应/晶闸效应(Latch-up)

Guard Ring的一个重要作用就是抑制闩锁效应。

Layout中的闩锁模型

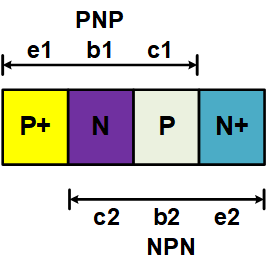

如上图展示了直接制作一对靠近的PMOS和NMOS的工艺截面。注意红色箭头,其依次经过了P+、N、P、N+区域,即可以简化为如下的模型:

而有另一类器件叫做BJT,其有三个端子,分别是:基极(b)、集电极(c)、发射极(e)。PNP管的ebc分别由P++、N、P+制作,而NPN管的ebc分别由N++、P、N+制作。类比BJT的结构