参考书籍《Static Timing Analysis for Nanometer Design》

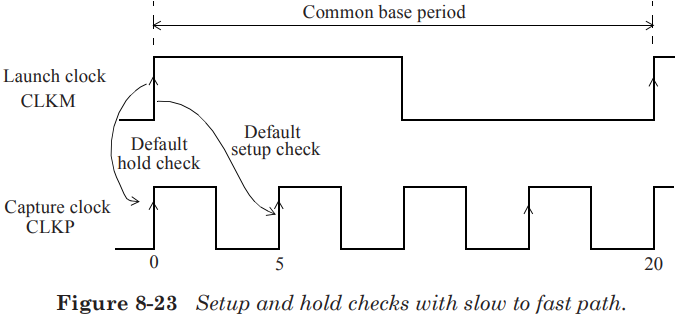

慢时钟 ——> 快时钟

首先进行时钟约束

create_clock -name CLKM -period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]

由于电路是从慢时钟到快时钟的,因此最严格的建立时间检查路径就是从慢时钟的0时刻 发送,在快时钟的第一个上升沿检测建立时间。

特别的:实际电路中,慢时钟域的延时会非常大,可能会超过一个或多个快时钟域周期,因此这个时钟可以根据实际的延时值,规定在第几个时钟周期进行时序分析,而不是从默认的第0个时钟周期开始时序分析。

set_multicycle_path 4 -setup -from [get_clocks CLKM] -to [get_clocks CLKP] -end

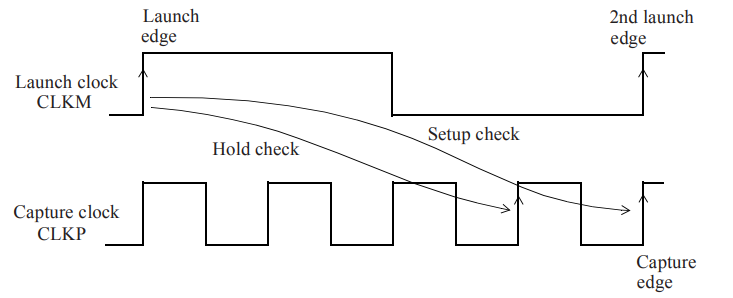

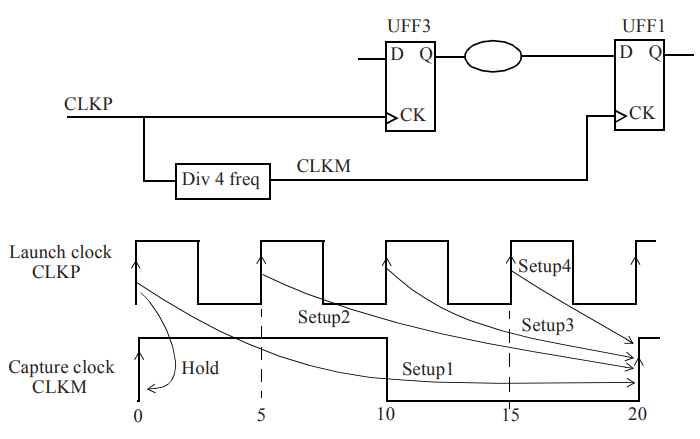

快时钟 ——> 慢时钟

create_clock -name CLKM -period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]

此时,一个捕获时钟周期可以收到多个发射时钟的数据。

快时钟的第一个时钟周期来检查保持时间是最严格的,快时钟的第四个时钟周期检测建立时间最为严格。

此外也可以通过下述代码来,调整建立时间和保持时间的检查点。

set_multicycle_path 2 -setup -from [get_clocks CLKP] -to [get_clocks CLKM] -start

set_multicycle_path 1 -hold -from [get_clocks CLKP] -to [get_clocks CLKM] -start