合并型数组(packed):

合并型数组可以实现连续的存储,赋值时不需要用 ’{ }。

数组中,数据排列为{ b_pack[2], b_pack[1], b_pack[0] },其中每个b_pack为8个bit;

bit是二值逻辑,每位bit只占据1位。故24位(8 bit * 3)只占据一个word(一般一个word为32 bit)的存储空间。

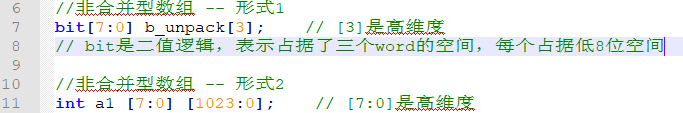

非合并型数组(unpacked)

存储的数据都是相互独立(不连续)的,赋值时需要用 ’{ };

那么如果:

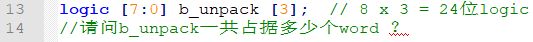

如果logic [3][7:0] b_pack的话,因为logic是四值逻辑,每一位logic需要两位来表示,所以24位logic就需要48位来表示,即需要2个word来存储。

注明:上述内容摘录于https://blog.csdn.net/SummerXRT/article/details/116588881