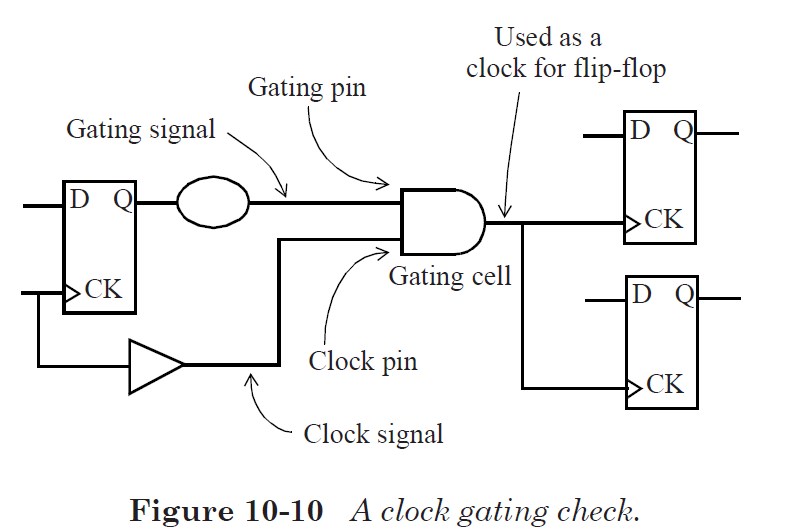

1、clock gating Checks典型的结构如下图所示

2、clock gating有两种类型,具体如下所示,这里的active high是指在gate pin为高时,clock可以通过

There are two types of clock gating checks inferred:

• Active-high clock gating check: Occurs when the gating cell has an and or a nand function.

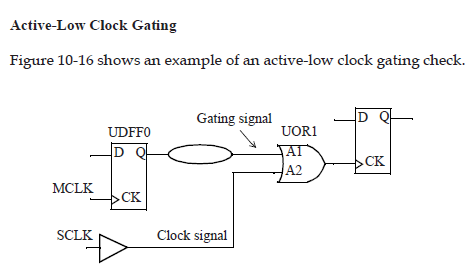

• Active-low clock gating check: Occurs when the gating cell has an or or a nor function.

gate结构的功能必须明确,如果是选择器或者异或逻辑等,STA就会输出一个警告: no clock gating check is being inferred. 这个警告可以通过

command set_clock_gating_check.来消除,但同时还要注意如果命令指定的功能与工具推出的不同,也会报出警告

3、clock gate 的timing如何检查?

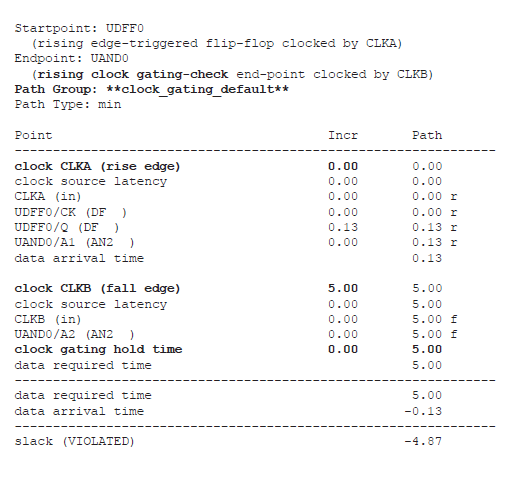

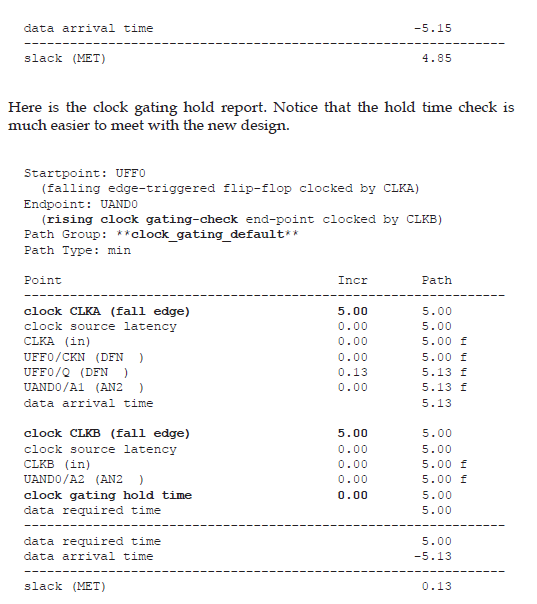

clock check timing的检查就是保证时钟不会出现毛刺,它的检查也是检查建立时间和保持时间,只是这里建立时间和保持时间的endpoint与常规的不同,针对figure10-10的图进行检查,

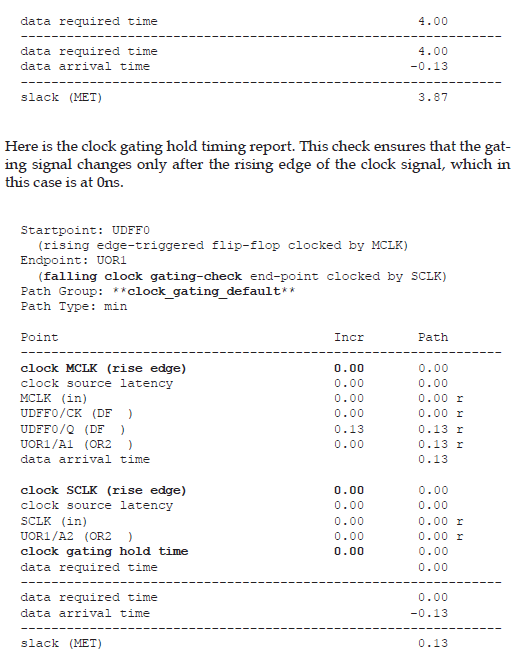

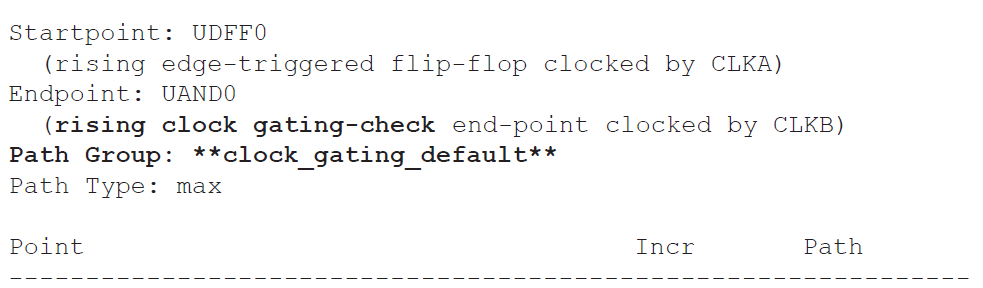

如下图所示:首先检查建立时间,由于是active-high结构,建立时间的检查点为CLKB的时钟上升沿,建立时间满足要求

然后检查保持时间,由于是active-high结构,gate 信号肯定不能在CLKB为高时,发生变化,要不然会出现毛刺,所以hold time的检查点的endpoint为

CLKB的下降沿,检查结果如下图所示,保持时间不满足要求。

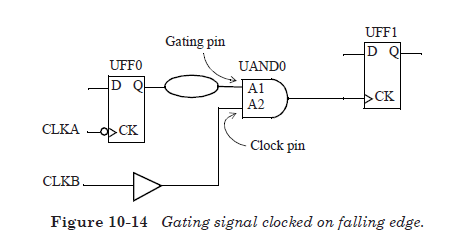

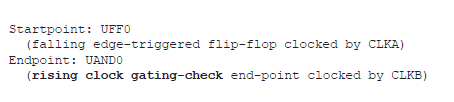

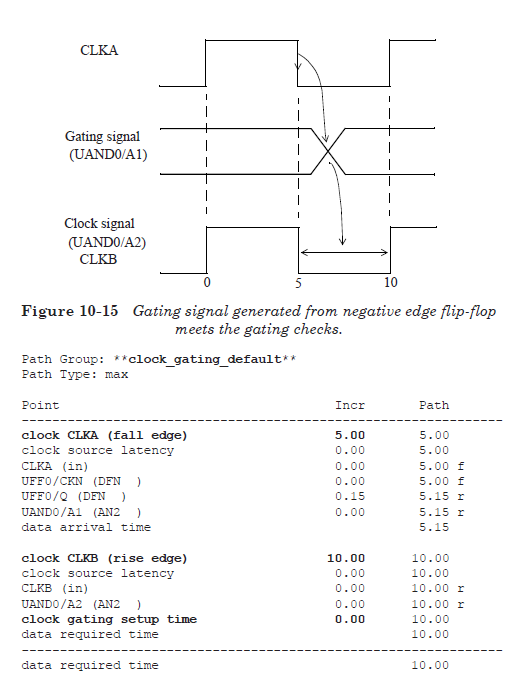

因此可以做如下改变,将CLKA进行反相

这样建立时间和保持时间都满足要求,

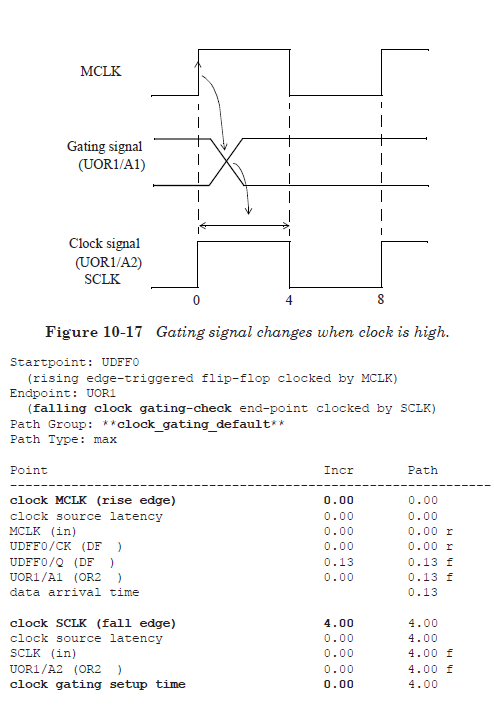

4。还有另外一种结构,active-low

这个结构有助于我们更好的理解建立时间的真是含义,它应该指的是时钟采样之前数据应该保持的时间,所以active-low的结构,clock为低时,gate才会起作用,因此建立时间的检查endpoint为SCLK下降沿,保持时间的检查点的endpoint是SCLK