GPU max power distribution

- internal power and switch power - 动态功耗(时钟翻转)

- Leakage power - 漏电功耗(静态功耗,mos管导通的特性)

- clock_network - 时钟树的功耗,系统中有很多寄存器,但是时钟到达寄存器的时间是不同的,需要插入一些buffer,形成时钟网络,会有功耗

- combination - 组合逻辑功耗

- sequential - 时许逻辑

- memory - 存储功耗,系统中的memory比较多,功耗比较高

时钟树上的功耗是不能被忽略的,需要优化时钟树上的功耗

Clock Gating for Conventional RTL

- 在写寄存器的时候,需要设置使能信号,在使能信号的作用下,才能将D段的数据同步到Q端

- 添加CG就是一个与的逻辑,将clock与enable信号进行与操作,enable = 0,时钟不反转;enable = 1,输入就是时钟,时钟翻转

- ICG - 综合工具会自动进行插入,不需要手动进行例化,但是代码风格需要注意,给寄存器添加使能型信号

Clock Gating across - Module Boundartes

Clock Gating for Implicit Enable

- 工具会尽可能添加ICG,最好写代码的时候添加enable信号

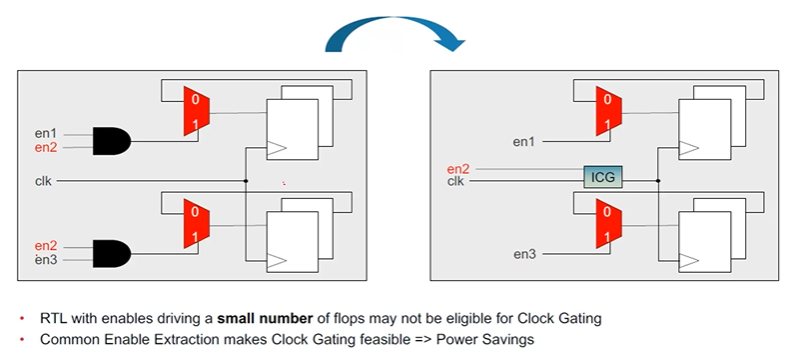

Automated Common Enable Extraction

always @ (posedge clk)begin

if(en0 && en1)

a_r <= a_nxt;

end

reg [1:0] b_r;

always @ (posedge clk)begin

if(en1 && en2)

b_r <= b_nxt;

end

- 寄存器数据位宽小于4bit,工具是不会插入ICG的,因为插入ICG会有一些面积的产生

- a_r和b_r有共同的使能en1,工具会提取公共的使能端,生成ICG

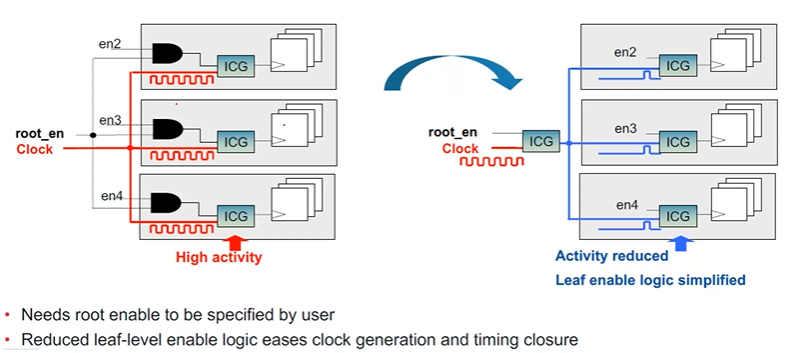

Multi-Stage Clock-Gating When CE is Specified

- ICG生成的时钟可以驱动其他的寄存器

- 时钟路径比较长,导线和buffer上时钟翻转也会产生功耗,几个寄存器前一级有公共的使能端,可以在前一级设置一个ICG,能供降低导线和buffer上的时钟翻转,降低功耗

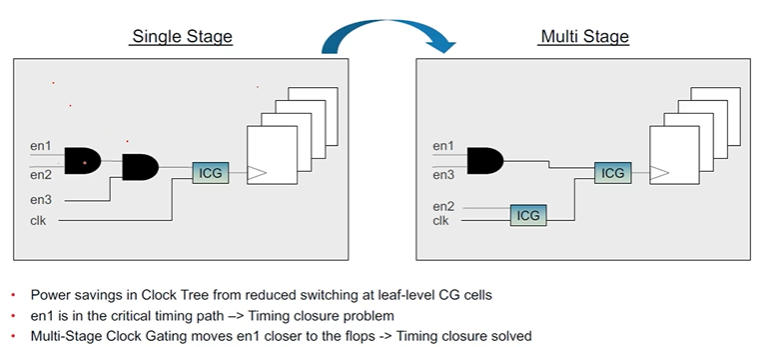

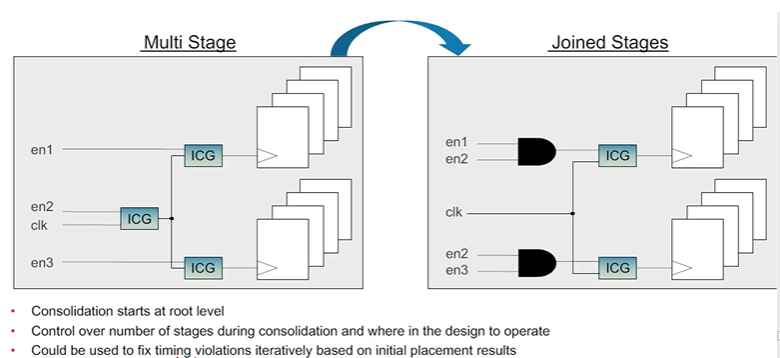

Multi-Stage Clock—Gating

Consolidating Multi-Stage Clock Gating

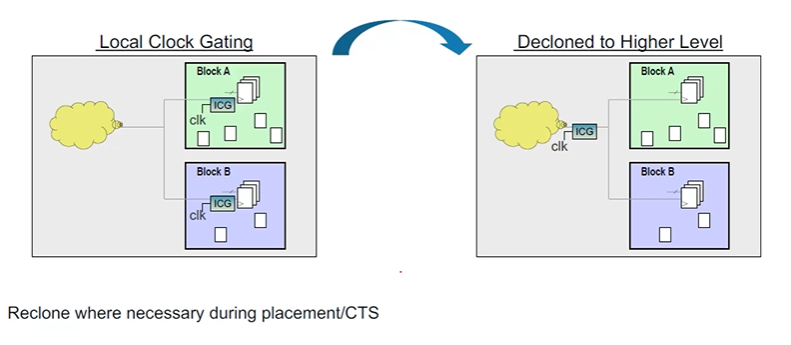

"Decloning" Local Clock Gating