特点:发送—并转串;接收—串转并;全双工传输

1、发送:

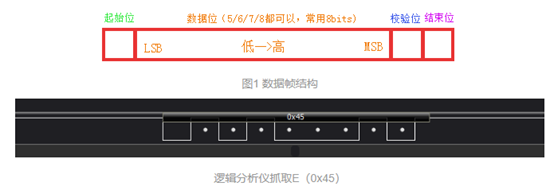

常见设置包含:起始位、数据位、波特率、奇偶校验类型、停止位、空闲位

(1)起始位

先发一个逻辑0,表示传输字符开始,依靠检测起始位来实现发送与接收方的时间同步。

(2)数据位

单个UART数据传输的数据位数,可以是5、6、7或8(默认)

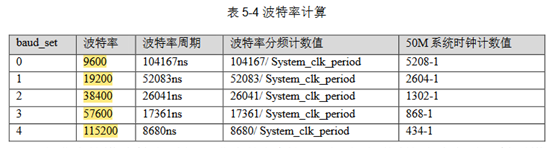

(3)波特率

用途:确定每秒钟通信的数据比特个数

举例:“使用波特率为115200bps ,则我们需要产生一个频率为115200Hz的时钟信号”

步骤:①计算波特率周期Tb;

1秒钟为1000_000_000ns,则周期Tb = 1000_000_000/115200 = 8680.6ns,即115200信号的一个周期为8680.6ns。

设定定时器定时时间为8680.6ns,每当定时时间到,产生一个系统时钟周期长度的高脉冲信号即可

②计算波特率分频计数值;

系统时钟频率fclk为50MHz,即系统时钟周期Tclk为20ns

波特率分频计数值 = Tb/Tclk = 8680/20

即,只需要计数8680/20个系统时钟,就可获得8680ns 的定时

③计算系统时钟计数值;

= 波特率分频计数值 – 1 = Tb/Tclk – 1 = 8680/20 – 1 = 434 -1

(4)校验位

用途:验证数据的正确性;

原理:①奇校验(Odd)——所有传送数位(数据位+校验位)中“1”的个数为奇数;

②偶校验(Even)——所有传送数位(数据位+校验位)中“1”的个数为偶数;

(5)停止位

用途:标志一次数据传输完成;可选择1(默认)、1.5或2位。

(6)空闲位

处于逻辑“1”状态,表示没有数据传输

2.接收

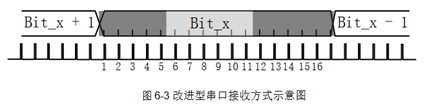

使用改进型串口接收方式

原理:将每一个bit平均分成16小段,对中间浅灰色段,进行多次采样(过采样),并求高低电平发生的概率,取出现次数最多的电平为采样结果。

包含:异步信号同步设计、边沿检测设计、采样时钟生成模块设计、采样数据接受模块设计、数据状态判断模块设计

(1)异步信号同步设计——使用两级触发器(打两拍)

理由:接收的信号如不进行处理,直接将其输入使用,容易出现时许为例导致亚稳态——单bit信号跨时钟域的处理;

(2)边沿检测设计

理由:起始位由空闲的高变低

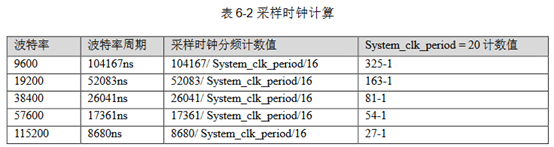

(3)采样时钟生成模块设计

基于过采样方式——实际采样频率为波特率的16倍

(4)采样数据接受模块设计

步骤:以图6-3为例,位于中间的采样时间段对应的bps_cnt值分别为6、7、8、9、10、11。

以16作为循环,后一位数据采样时间段的bps_cns值为22、23、24、25、26、27。以此类推,得到其他位的采样时间段对应bps_cnt值。

(5)数据状态判断模块设计

步骤:基于原理,使用数值比较器进行判断,或直接令其等于当前位的最高位数据。