关于DMA (一)

发布时间 2023-06-19 14:42:04作者: 可达达鸭

1. CPU与外设数据传送方式

- 主要有程序传送方式和中断传送方式。

- 程序传送方式

- 在程序控制下进行数据输入/输出操作,分为无条件(无需考虑外设状态,直接IN/OUT指令输出)和查询(在IN/OUT指令前,需要查询设备状态)两种。

- 中断传送方式

- 外设向CPU发起请求,CPU暂停正在执行的程序,去传输数据给外设,传输结束后。CPU再继续被暂停的程序。

- 程序传送方式和中断传送方式的区别

- 前者为CPU主动发起,轮询外设,效率低。

- 后者为外设主动发起,等待CPU处理,但是需要进行断点和现场的保护和恢复,浪费CPU时间,适合少量数据的传输。

- 下图列出了CPU程序传送方式、中断传送方式以及DMA传送方式的CPU使用情况。(图源不知道是哪里,有点糊。)

2. DMA 批量数据传输

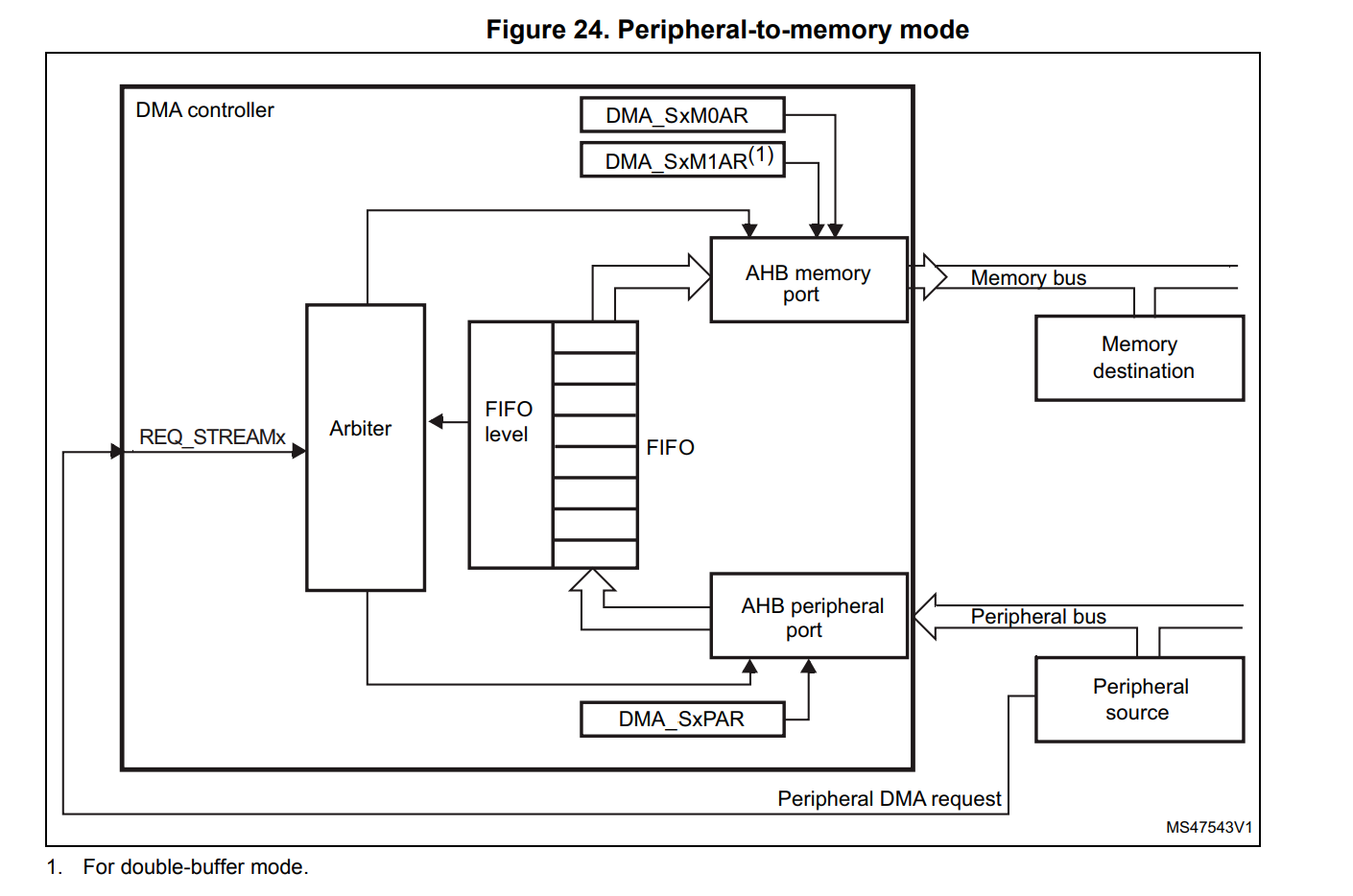

- 下图为DMAC结构图。

2.1 传输方向

2.2 传输过程

- (1)请求

- CPU配置DMA相关寄存器:

- 控制命令寄存器,配置传输数据的发起方式、数据大小、通道。

- 初始地址寄存器,DMAC根据该地址寄存器的值,进行寻址传输数据。

- 之后向I/O接口发出操作命令;外设向DMA控制器发出请求,有单独请求信号线,而不是走AHB总线。

- (2)响应

- DMA控制器对 多个DMA请求 判断优先级以及是否屏蔽请求,之后向总线仲裁模块提出总线请求。

- 当CPU执行完当前任务即可释放总线控制权。DMA控制器获得总线控制权后便开始传输。

- (3)传输

- DMA拿到总线控制权后,CPU无法使用总线,所以它挂起或只执行内部操作;DMA控制器直接控制内部存储器与外设之间的数据交互。

- (4)结束

- 完成数据传送后,DMA控制器释放总线控制权,并向外设发出结束信号,外设需要结束数据传输工作,并向CPU提出中断请求。

- CPU执行中断服务程序,检验DMA传输过程是否出错,以及是否要继续使用DMA传送其它数据块。

3. DMA & CPU 内存分配

- DMA传输需要对内存进行操作,而CPU在DMA传输过程中仍可以继续工作,可能也会对内存进行操作,这就涉及到DMA和CPU怎么分时使用内存。通常有3种传送方式:

- (1)停止CPU访问内存

- DMA控制器向仲裁器申请总线控制权时,CPU交出控制权,处于不工作状态或者保持状态。

- 优点:控制简单;

- 缺点:考虑到外设传送两个数据之间的间隔一般大于内存的存储周期,例如,外设读出两个数据之间的间隔大概32us,内存的存储周期大概为0.5us,那么内存就有31.5us(63个内存周期)的空闲。

- (2)周期挪用(较为常用)

- DMA访问内存和CPU访问内存没有冲突。

- 例如,CPU正在执行乘法操作,从内存取出数据之后可能还要消耗一些周期,此时DMA挪用一两个内存周期也不会影响CPU的程序执行。

- DMA访问内存和CPU访问内存有冲突。

- 需要优先DMA(I/O)访内,因为I/O访问内存有时间要求,这个数据必须在下一个I/O访问请求之前存取/读出完毕。

- 此时可以在CPU访问内存过程中插入DMA请求,挪用一两个CPU的内存周期,用于DMA的数据存取;延缓了CPU对内存空间的操作。

- 但是DMA每次挪用需要有申请总线控制权、归还总线控制权的过程,所以每次读取一个字对于内存来说可能只要一个周期,但是对于DMA控制器却要2-5个内存周期。但是好在大部分的外设读写周期都要大于内存存储周期。

- (3)DMA和CPU交替访问内存

- 主要适用于CPU工作周期比内存存取周期长的多情况。

- 例如CPU周期为1.2us,内存存取小于0.6us,这样就可以将一个CPU周期分为C1和C2两个周期,其中C1为DMA访问内存,C2为CPU访问内存。

- 这种方式不必像(2)中一样需要总线使用权的申请和归还过程,因为总线使用权是C1和C2分时制的。对于总线来说,输入的数据、地址、控制信号等是由C1,C2周期控制的多路选择器的输出。

- 这种方式CPU不会停止主程序的运行,也不会进入等待状态,效率是三种方式中最高的,但是相应的硬件逻辑也更复杂。