1.半加器

- 加法器是数字电路中经常用到的一种基本器件,主要用于两个数或者是多个数相加,加法器又分为半加器(half adder)和全加器(full adder)

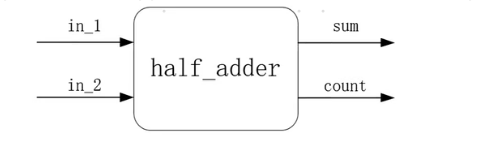

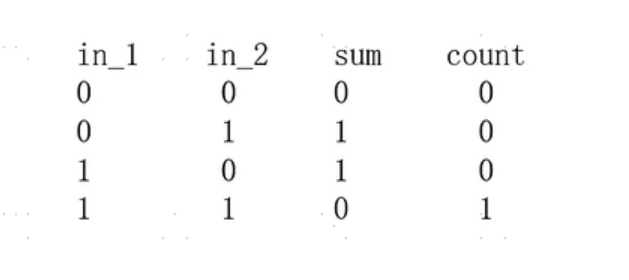

- 半加器电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。是实现两个一位二进制数的加法运算电路。

- 全加器是在半加器的基础上的升级版,除了加数和被加数加和外,还要加上上一级传入进来的进位信号。

2.FPGA设计

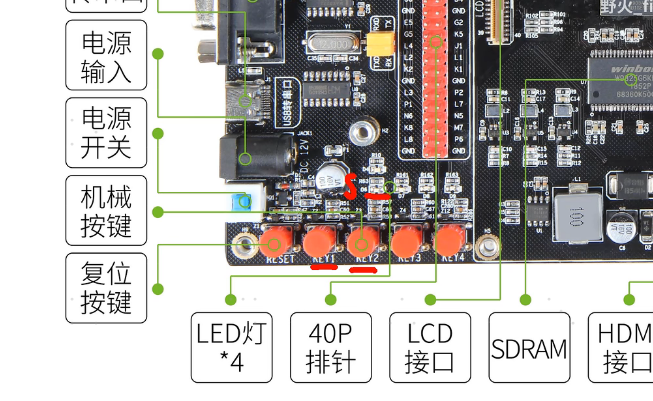

- KEY1,KEY2表示两个加数

- LED6表示和的输出,LED7表示进位的输出

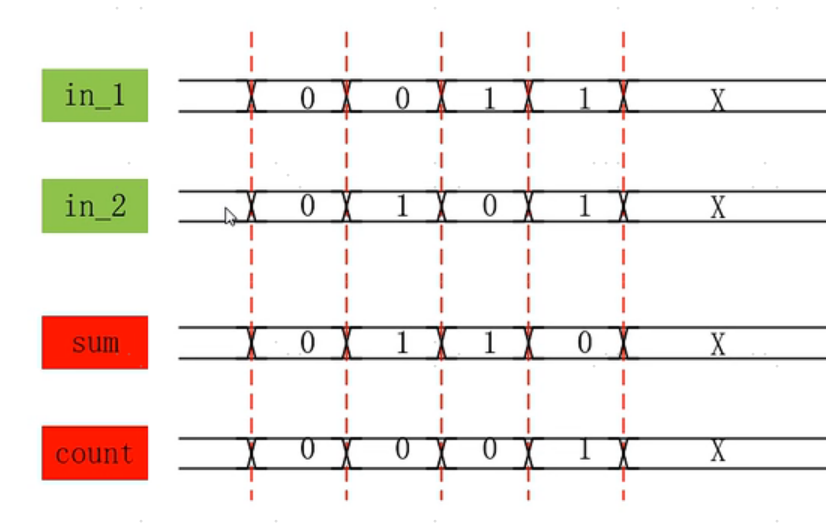

2.1 框图和波形图

- 画波形图的时候,可以借助真值表

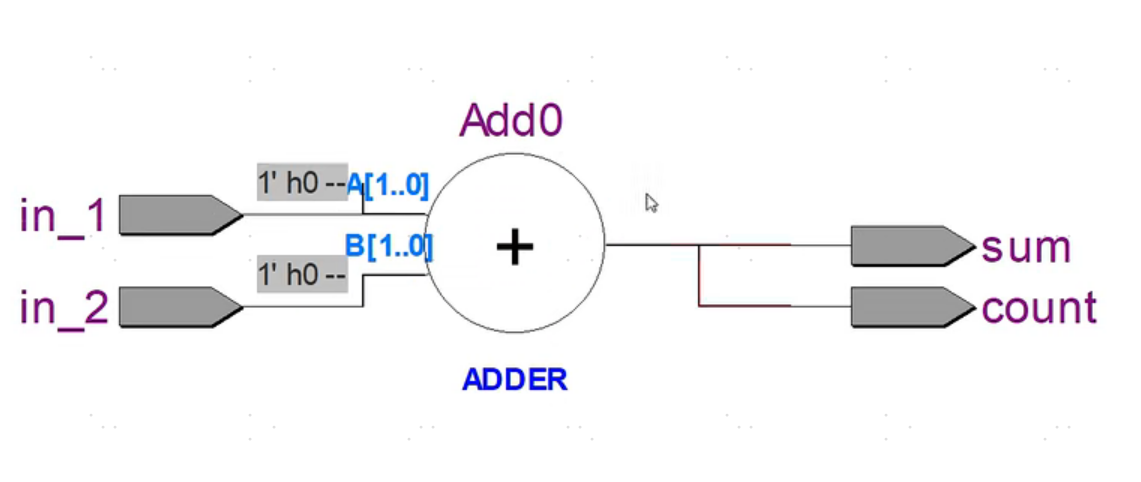

2.2 RTL

module half_adder

(

input wire in_1,

input wire in_2,

output wire sum,

output wire c_in

);

assign {c_in,sum} = in_1 + in_2;

endmodule

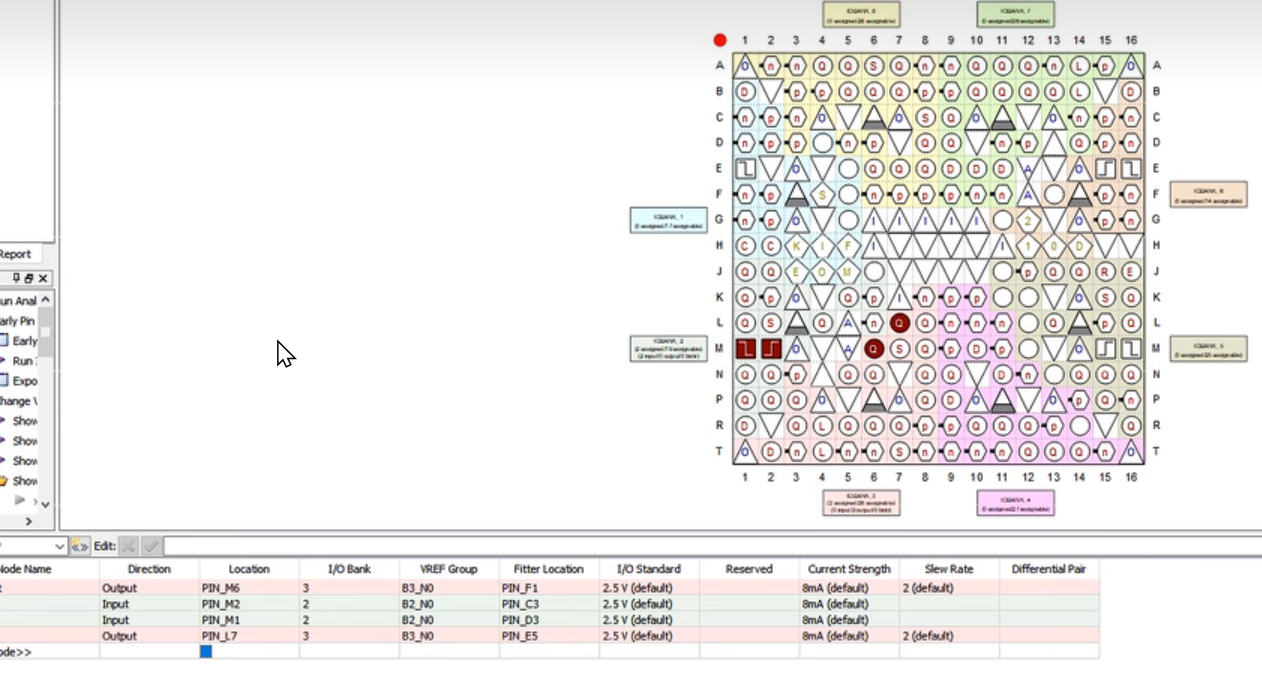

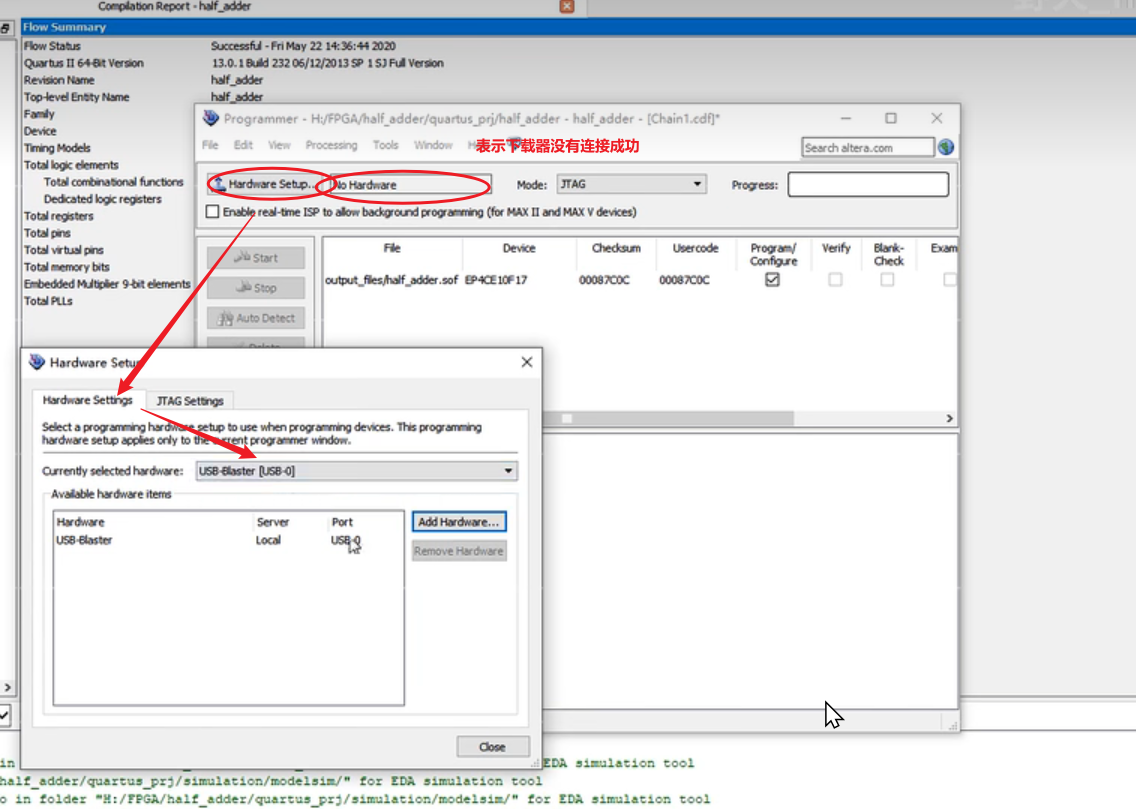

- 创建quartus项目,编译verilog代码

2.3 Testbench

`timescale 1ns/1ns

module tb_half_adder();

reg in_1;

reg in_2;

wire sum;

wire c_in;

initial begin

in_1 <= 1'b0;

in_2 <= 1'b0;

end

initial begin

$timeformat(-9,0,"ns",6);

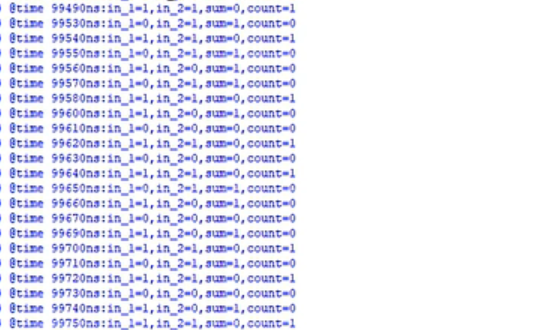

$monitor("@time:in_1 = %b,in_2=%b,sum=%b,count=%b",$time,in_1,in_2,sum,count);

end

always #10 in_1 = {$random} % 2;

always #10 in_2 = {$random} % 2;

endmodule

- 在quartus项目中添加文件,设置仿真,进行仿真

2.4 上板验证