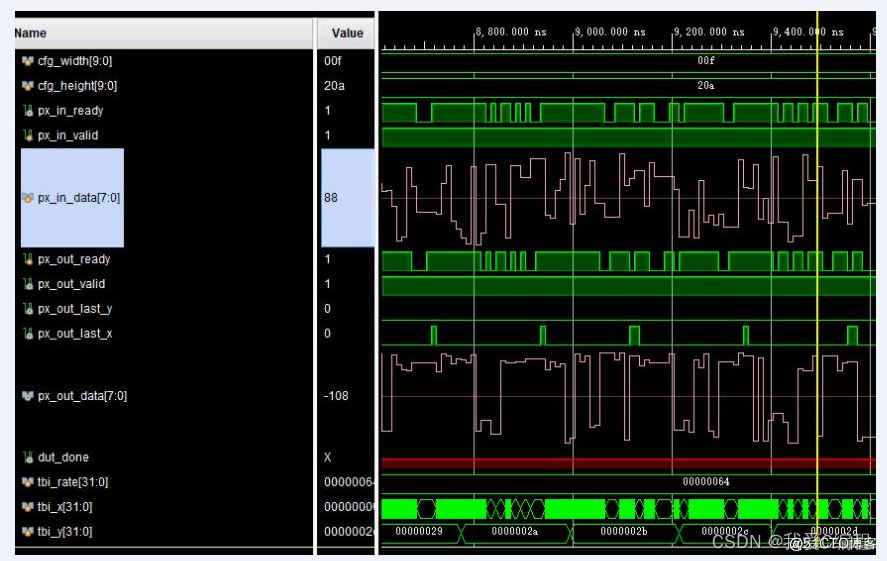

1.算法仿真效果

matlab2022a仿真结果如下:

2.算法涉及理论知识概要

FIR(Finite Impulse Response)滤波器:有限长单位冲激响应滤波器,又称为非递归型滤波器,是数字信号处理系统中最基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响应是有限长的,因而滤波器是稳定的系统。因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。

在进入FIR滤波器前,首先要将信号通过A/D器件进行模数转换,把模拟信号转化为数字信号;为了使信号处理能够不发生失真,信号的采样速度必须满足香农采样定理,一般取信号频率上限的4-5倍做为采样频率;一般可用速度较高的逐次逼进式A/D转换器,不论采用乘累加方法还是分布式算法设计FIR滤波器,滤波器输出的数据都是一串序列,要使它能直观地反应出来,还需经过数模转换,因此由FPGA构成的FIR滤波器的输出须外接D/A模块。FPGA有着规整的内部逻辑阵列和丰富的连线资源,特别适合于数字信号处理任务,相对于串行运算为主导的通用DSP芯片来说,其并行性和可扩展性更好,利用FPGA乘累加的快速算法,可以设计出高速的FIR数字滤波器。

(1) 系统的单位冲激响应h (n)在有限个n值处不为零

(2) 系统函数H(z)在|z|>0处收敛,极点全部在z = 0处(因果系统)

(3) 结构上主要是非递归结构,没有输出到输入的反馈,但有些结构中(例如频率抽样结构)也包含有反馈的递归部分。

设FIR滤波器的单位冲激响应h (n)为一个N点序列,0 ≤ n ≤N —1,则滤波器的系统函数为

H(z)=∑h(n)*z^-k

就是说,它有(N—1)阶极点在z = 0处,有(N—1)个零点位于有限z平面的任何位置。

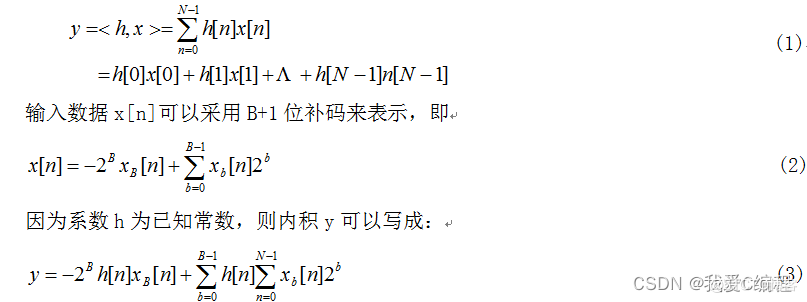

对于FIR(有限长单位冲激响应)滤波器,其基本结构是一个分节的延时线,每一节的输出加权累加,得到滤波器的输出。其输出y就是输入x和系数h的内积:

3.MATLAB核心程序

module xfilter(clk, rst,

i_valid_new_pixel,

i_new_pixel,

i_valid_lpos,

i_valid_cpos,

i_valid_rpos,

i_rowM,

o_valid_filt,

o_filt_pixel,

o_colN,

o_rowM

);

parameter XB = 10;

parameter PB = 8;

input clk;

input rst;

input i_valid_new_pixel;

input [(PB + 2) - 1:0] i_new_pixel;

input i_valid_lpos;

input i_valid_cpos;

input i_valid_rpos;

input i_rowM;

output o_valid_filt;

output [PB - 1:0] o_filt_pixel;

output o_colN;

output o_rowM;

reg [(PB + 4) - 1:0] r_pixel_sum = 0;

reg [PB - 1:0] rr_pixel_sum = 0;

reg r_valid_lpos = 0;

reg r_valid_cpos = 0;

reg r_valid_rpos = 0;

reg r_valid_filt_pixel = 0;

reg rr_valid_cpos = 0;

reg r_valid_pixel_in = 0;

reg rr_valid_pixel_in = 0;

........................................................................

always @(posedge clk)

begin

//read in pixel

r_valid_lpos <= i_valid_lpos;

r_valid_cpos <= i_valid_cpos;

r_valid_rpos <= i_valid_rpos;

rr_valid_cpos <= r_valid_cpos;

r_colN <= i_valid_rpos;

rr_colN <= r_colN;

rrr_colN <= rr_colN;

r_rowM <= i_rowM;

rr_rowM <= r_rowM;

rrr_rowM <= rr_rowM;

if (rst)

begin

r_valid_pixel_in <= 0;

rr_valid_pixel_in <= 0;

r_valid_filt_pixel <= 0;

end

else

begin

r_valid_pixel_in <= c_valid_pixel_in;

rr_valid_pixel_in <= r_valid_pixel_in;

r_valid_filt_pixel <= rr_valid_pixel_in;

end

r_pixel2 <= c_pixel2;

end

wire [PB + 4 - 1: 0] c_pixel_sum = (rr_valid_cpos) ? r_pixel_sum + r_pixel2 + 8: r_pixel_sum + 8;

reg r_valid_new_pixel = 0; //needed to check if new row's data was added

//add filter

always @(posedge clk)

begin

r_valid_new_pixel <= i_valid_new_pixel;

if (r_valid_rpos)

begin

if (r_valid_new_pixel) //new data added to queue

r_pixel_sum <= {c_pixel1, 1'd0} + c_pixel2;

else

r_pixel_sum <= {c_pixel0, 1'd0} + c_pixel1;

end

else

begin

r_pixel_sum <= c_pixel0 + {c_pixel1, 1'd0};

end

rr_pixel_sum <= c_pixel_sum[PB + 4 -1: 4];

end

//3 pixel buffer

queue PIXBUF (.clk(clk),

.i_valid_pixel(i_valid_new_pixel),

.i_pixel(i_new_pixel),

.o_pixel0(c_pixel0),

.o_pixel1(c_pixel1),

.o_pixel2(c_pixel2)

);

endmodule

module queue(clk, i_valid_pixel, i_pixel, o_pixel0, o_pixel1, o_pixel2);

parameter PB = 8;

.....................................................

endmodule