汇总篇:

Xilinx FPGA平台以太网接口(汇总篇)_xilinx ethernet_子墨祭的博客-CSDN博客

一、系统架构

基于TOP-DOWN的设计思路,我们首先需要了解基于FPGA的以太网接口设计的系统模型:

MAC是媒体访问控制器。以太网MAC由IEEE-802.3以太网标准定义。它实现了数据链路层。最新的MAC同时支持10/100/1000Mbps速率。通常情况下,它实现MII/GMII/RGMII等接口,来同行业标准PHY器件实现接口。

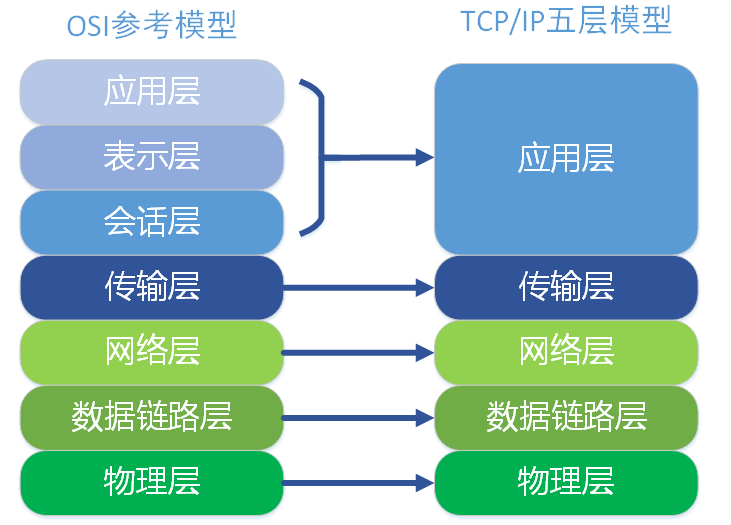

MAC由硬件控制器及MAC通信协议构成。该协议位于OSI七层协议中数据链路层的下半部分,主要负责控制与连接物理层的物理介质。

MAC层可以自己编写代码,也能使用现成的IP。由FPGA来实现。

PHY是TCP/IP协议栈中的物理层器件,也就是我们常说的PHY芯片,如88E1111,支持不同形式的数据转换为以太网所支持的传输媒介,例如支持1000BASE-T、100BASE-T、10BASE-T类型的以太网传输。支持CAT-5类非屏蔽双绞线上的数据收发。可以直接连接到MAC/SWITCH接口,例如FPGA的IP核。支持RMII、GMII、RGMII、SGMII、XAUI等接口。

PHY芯片的作用可以说就是MAC层与双绞电缆间的适配。

RJ45是布线系统中信息插座(即通信引出端)连接器的一种,连接器由插头(接头、水晶头)和插座(模块)组成,插头有8个凹槽和8个触点。RJ是Registered Jack的缩写,意思是“注册的插座”。在FCC(美国联邦通信委员会标准和规章)中RJ是描述公用电信网络的接口,计算机网络的RJ45是标准8位模块化接口的俗称。就是连接器。

在此系统架构基础上,我们继续了解MAC层接口。

PS: 插播一个OSI七层结构与TCP/IP五层结构模型

二、MAC层接口

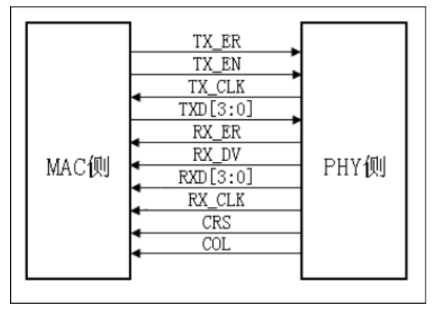

MII接口 : Medium Independent Interface,介质独立接口。 一般应用于以太网硬件平台的MAC层与PHY层之间,MII接口的类型有很多,常用的有MII、RMII、GMII、RGMII、SGMII、XAUI等接口。

MII接口 :

l RXD(Receive Data)[3:0]:数据接收信号,共4根信号线;

l TX_ER(Transmit Error): 发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。对于10Mbps速率下,TX_ER不起作用;

l RX_ER(Receive Error): 接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。对于10Mbps速率下,RX_ER不起作用;

l TX_EN(Transmit Enable): 发送使能信号,只有在TX_EN有效期内传的数据才有效;

l RX_DV(Reveive Data Valid): 接收数据有效信号,作用类型于发送通道的TX_EN;

l TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

l RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。RX_CLK也是由PHY侧提供的。

l CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS就有效,另外,CRS只有PHY在半双工模式下有效;

l COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只有PHY在半双工模式下有效。

接口共16根线。

-----------------------

剩下的RMII、GMII、RGMII等接口就不再这么详细列举了,我们使用一个表格(from:“碎碎思”大佬)对比就能清晰了解,重点关注速率的变化。

|

MII |

基本的100Mbps/10Mbps接口 |

RXD[3:0]、TXD[3:0] TX_ER、TX_EN RX_ER、RX_DV TX_CLK、RX_CLK CRS、COL |

Clock=25MHz or 2.5MHz 数据位宽4bit(一个时钟周期传输4bit数据) 100Mbps=25 MHz *4bit 10Mbps=2.5 MHz *4bit |

|

RMII |

在MII基础上精简的100Mbps/10Mbps接口; 通过提升Clock频率保持与MII一样的速率; |

RXD[1:0]、TXD[1:0] TX_EN RX_ER CLK_REF CRS_DV |

Clock=50MHz 数据位宽2bit(一个时钟周期传输2bit数据) 100Mbps=50 MHz *2bit 10Mbps是利用10个周期采样一次数据,相当于 10Mbps=50MHz/10*2bit |

|

SMII |

串行MII 100Mbps/10Mbps接口; 进一步提升Clock频率保持与MII一样的速率; |

RXD[1:0] TXD[1:0] TX_EN RX_ER CLK_REF CRS_DV |

Clock=125MHz 数据位宽1bit(一个时钟周期传输1bit数据) 串行数据帧:一帧10bit(8bit data+2bit control) 计算有效带宽时需要去掉控制位 100Mbps=125 MHz *(8bit/10bit) 10Mbps是利用10个周期采样一次数据,相当于 10Mbps=(125 MHz/10)*(8bit/10bit) |

|

GMII |

在MII接口基础上提升了数据位宽和Clock频率成为1000Mbps接口 |

RXD[7:0]、TXD[7:0] TX_ER、TX_EN RX_ER、RX_DV GTX_CLK、RX_CLK CRS、COL |

Clock=125MHz 数据位宽8bit(一个时钟周期传输8bit数据) 1000Mbps=125 MHz *8bit |

|

RGMII |

GMII的简化版本 |

RXD[3:0]、TXD[3:0] TX_EN RX_DV TX_CLK、RX_CLK CRS、COL |

Clock=125MHz 数据位宽4bit(一个时钟周期里,上升沿取TX\RX的0-3bit,下降沿取TX\RX的4-7bit,所以实际还是在一个时钟周期里传输8bit数据) 1000Mbps=125 MHz *8bit 100Mbps=25 MHz *8bit 10Mbps=2.5MHz *8bit |

|

SGMII |

串行GMII,在此基础上提升了时钟频率达到1000Mbps |

RXD[0]、TXD[0] RX_CLK |

Clock=125MHz 数据位宽1bit(一个时钟周期传输1bit数据) 串行数据帧:一帧10bit(8bit data+2bit control) 1000Mbps=125.0MHz *8bit 但计算有效带宽时需要去掉控制位 |

重点注意速率的变化,因为当我们使用TRI_MODE三速以太网IP的时候,IP其实就是通过时钟频率来控制MAC层速率的。

另外,在FPGA实现网络通信时,还有一个特殊的接口不得不提,那就是SerDes。万兆以太网通信就是基于SerDes来实现的。我们这里暂时略过。

下一篇,我们开始介绍IP核的配置以及所用接口的介绍。