使用mig ip核控制ddr3的时候有许多配置,尤其是有很多时钟容易混淆,查了很多资料后我稍微总结了一下,可能有不太对的地方,先记录一下防止遗忘。

下面是时钟结构图,图片来源:FPGA大叔

首先要知道DDR3的一些时钟含义:

1.接口时钟:接口与外部FPGA通信的时钟。

2.等效时钟:因为数据在接口双沿采样,因此等效时钟为接口时钟的两倍。

3.芯片内核工作时钟:DDR3存储芯片内部存储阵列的时钟。

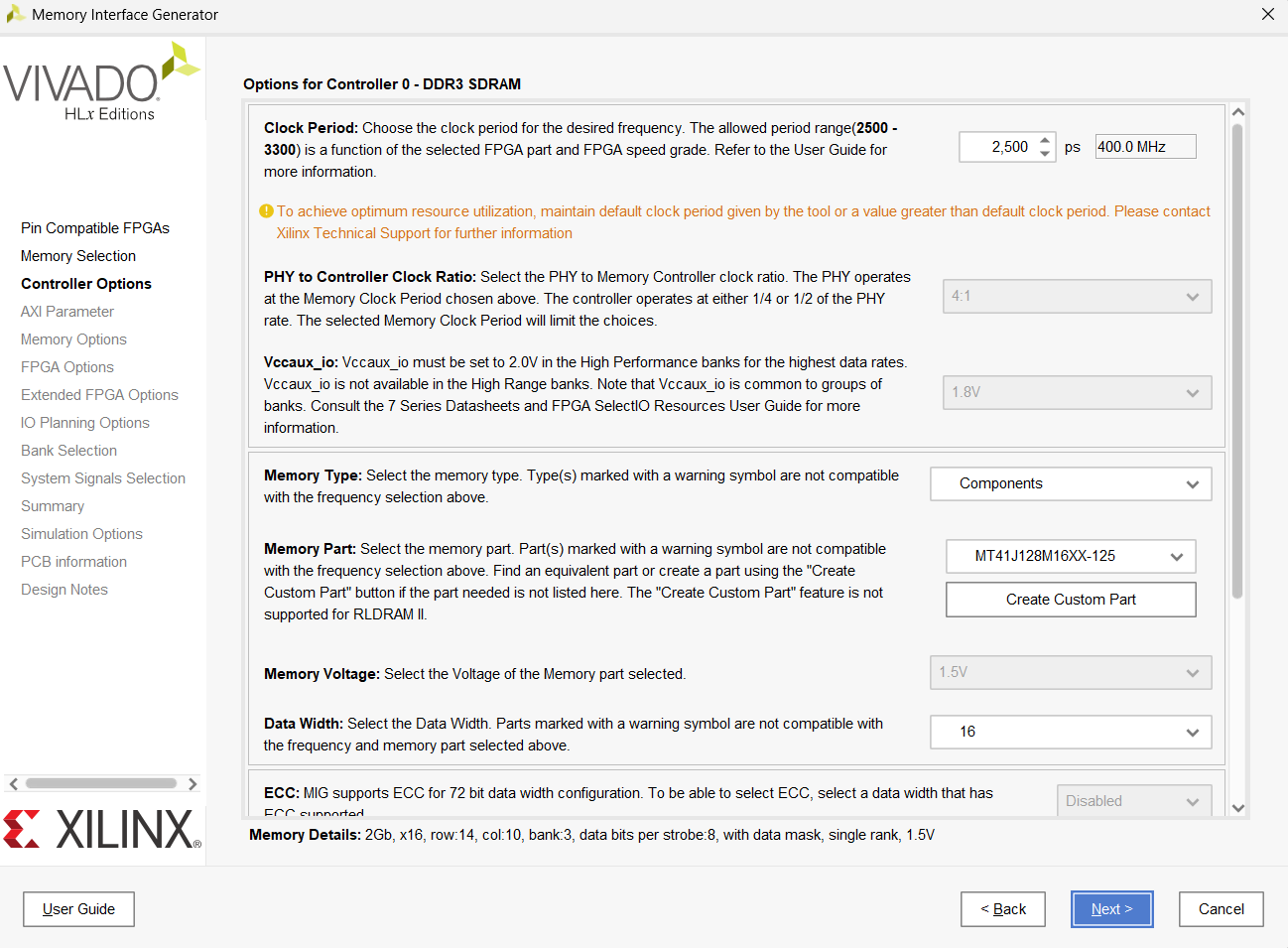

1、这里的Clock Period即为接口时钟频率,也就是ddr3实际工作的时钟。其最大值由板子型号决定。这里选择最大值400MHz。

PHY to Controller Clock Ratio:4:1:接口时钟频率为400MHZ,那么读写的数据到用户逻辑侧,工作时钟就是100MHZ。这个同样会影响用户侧数据位宽。

2、Input Clock Period:输入时钟频率,这是输入给MIG 核的时钟频率,对应的时钟就是MIG核的系统时钟。

3、下一页选择系统时钟和参考时钟,有三个选项:

- single_ended :来源于引脚的单端时钟

- deferential :差分时钟

- no buffer :来源于 FPGA 内部的时钟

System Clock:系统时钟,这里选择No Buffer,用的就是上一页Input Clock Period的200MHz。

Reference clock:参考时钟,这个时钟频率是固定的,如果工作频率>666MHz ,参考时钟固定为300MHz/400MHz,其他工作频率固定为200MHz。如果system clock的频率在199-201MHz之间,会出现一个use system clock 的选项,意思就是用系统时钟作为参考时钟。

4、内部终端电阻值,按照手册来,这里就默认的50 Ohms。

5、这里选择引脚,第一个选项是新设计,第二个选项是导入已经有的引脚约束文件。

6、点击Read XDC/UCF,选择引脚约束文件,然后要点击Validate进行验证才可以下一步。

7、后面就一直next就行了。