- 参考

- APB到AHB的传输主要包括:读传输、写传输、背靠背传输。

1. 读传输

- 单个读传输

- 波形如下,在T1,将地址送到AHB总线上,在T2上升沿采样到HADDR地址信号,组合逻辑判断是APB的某个从机的地址范围,在T2时刻将HADDR赋值给PADDR,并组合逻辑产生APB某个从机对应的片选信号PSEL。

- 在这篇博客中有介绍:APB的数据传输需要两个时钟周期,当PSEL信号被拉高后,进入SETUP阶段,下一周期将PENABLE信号拉高,进入ACCESS阶段。

- ACCESS阶段,将被读的数据送到APB总线上,并送到AHB总线上,即PRDATA = HRDATA = Data1。

- 在系统时钟频率(APB and AHB)要求比较高时,PRDATA位宽如果比较大,那么可能一个APB的时钟周期传送不过去,(例如对于高时钟频率来说,图中PDATA灰色部分占整个周期大部分),那么就需要在T4插入额外的等待时间,以供AHB获取正确的数据。

- 需要注意,由于APB传输数据需要两个时钟周期,所以AHB的HREADY信号需要在第一个时钟周期拉低,为从机插入等待状态。

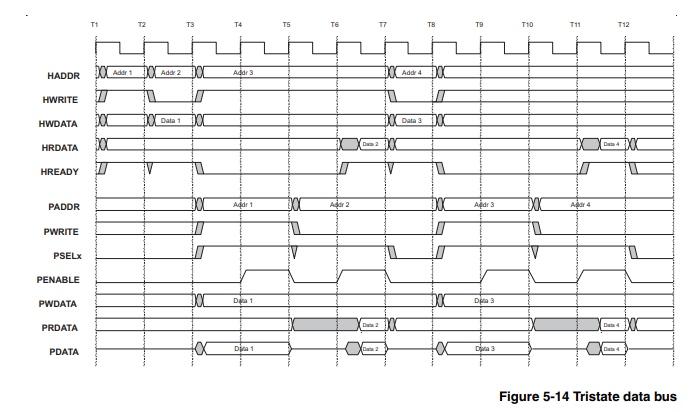

- 突发读传输

- 波形如下,可以很明显的看出APB总线一个数据的传输需要两个周期,AHB的HREADY信号也要相应的拉低。

- 波形如下,可以很明显的看出APB总线一个数据的传输需要两个周期,AHB的HREADY信号也要相应的拉低。

2. 写传输

- 单个写传输

- AHB传输是流水线,但是APB并不是流水线机制,所以需要将HADDR缓存下来,和HWDATA一起给到APB总线上。所以下面波形图中可以看到T3时刻APB才接收到Data1和Addr1.

- T3时刻,根据PADDR和组合逻辑,将APB的某个从机的片选信号拉高,APB的写传输也需要两个周期的传输,在第二个周期PENABLE被拉高后,数据才被写入从机中。

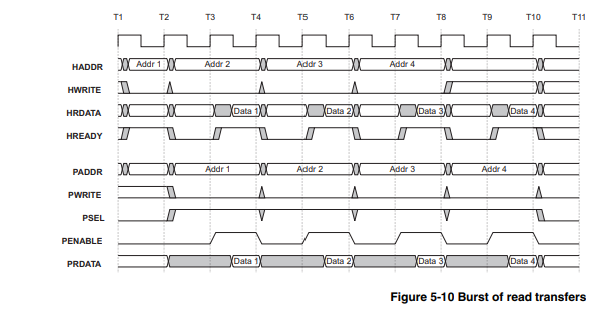

- 突发写传输

- 观察下面波形,可以看到APB桥需要有两个额外的地址寄存器,例如:对于T5周期来说,PADDR需要保存addr2和addr3。

- 观察下面波形,可以看到APB桥需要有两个额外的地址寄存器,例如:对于T5周期来说,PADDR需要保存addr2和addr3。

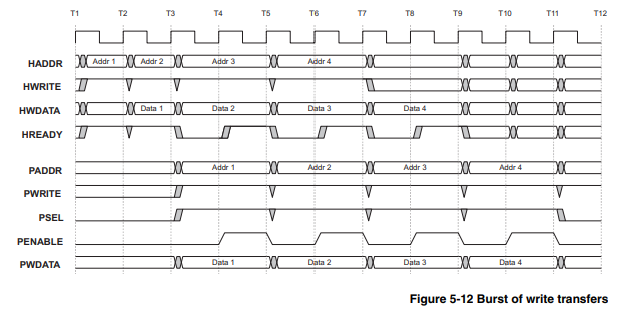

3. 背靠背传输

- 背靠背传输是指写传输之后跟着读传输,之后是写传输再之后是读传输。

- 观察下面波形

- T1-T2期间,HREADY信号被拉高是因为1之前还有一笔传输的完成,才可以进行1这笔传输。T2-T3拉高,表示数据已经传输给从机(AHB2APB Bridge)。

- 只有在时钟上升沿采到的HREADY信号为高,才可以更新HADDR和HWDATA。

- 在T3时刻,数据1和地址1才传送给PDATA和PADDR,需要两个周期,将数据写入从机中。

- 在T5,已经完成了写传输之后,开始读传输,地址2从APB额外的地址寄存器中读出,消耗两个周期读出从机的数据DATA2。在T6将HREADY信号拉高,在T7采到HREADY信号为高,可以开始新的地址和数据的传输。

- T8时刻数据3和地址3才准备好,此时才开始写传输,所以读操作需要3个等待时间。

- T10完成了数据3的写,地址4从APB额外的地址寄存器中读出,消耗两个周期读出从机的数据DATA4。

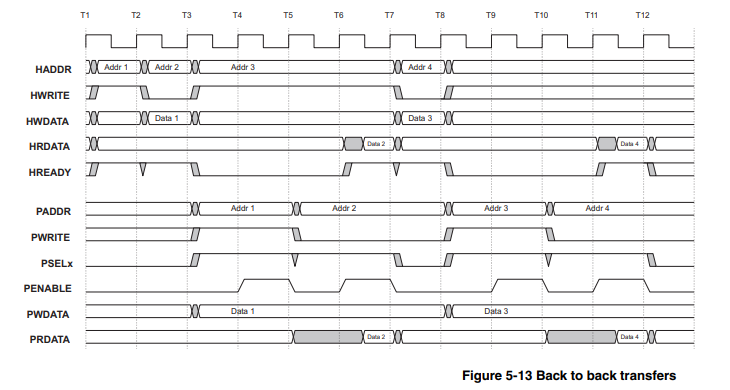

4. 三态数据总线的实现

- 三态:0,1,高阻态;一般的门电路输出只会有逻辑1或者0,可能会有个疑惑学习verilog时,还有x态和z态,但x和z是针对仿真设置的,实际电路x不定态一定会以0/1的形式表现。

- 使用三态门可以得到除0和1之外的高阻态,实际电路并不可能直接将某根线断开,所以是使用三态门给出一个高阻状态的输出。

- 总线与三态

- 总线空闲,即其它器件都以高阻态形式连接在总线上;当主机要发起通信时,会驱动总线,发出地址和数据,其它以高阻态形式连接在总线上的器件片选SEL信号拉高后,开始传输,传输完成后,将总线让出,再次变成高阻态。

- 三态可以有效避免总线上的设备发生冲突。

- 对于APB总线,可以分别使用读写数据总线实现,但是如果使用三态总线,那么读写数据总线可以合并成一根,因为APB的读写也不会同时发生。合并后的三态总线如下波形图。