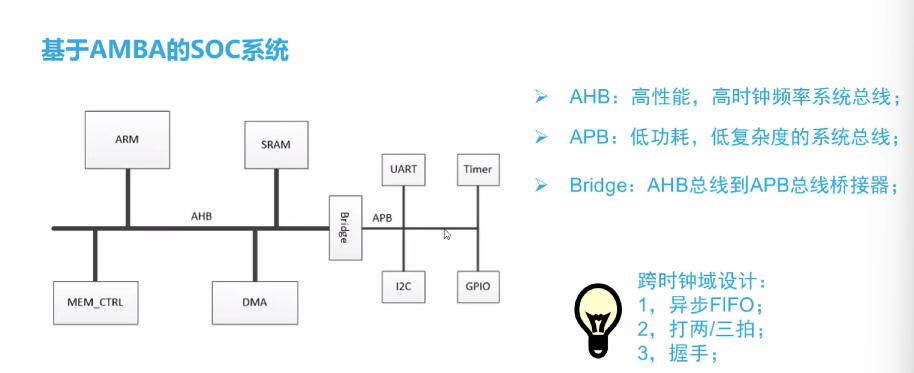

AHB2APB Bridge位置

- AHB子系统时钟在200Mhz左右,APB时钟在几十Khz到几十Mhz

- 所以要进行跨时钟域处理,从AHB高时钟频率转到APB低时钟频率

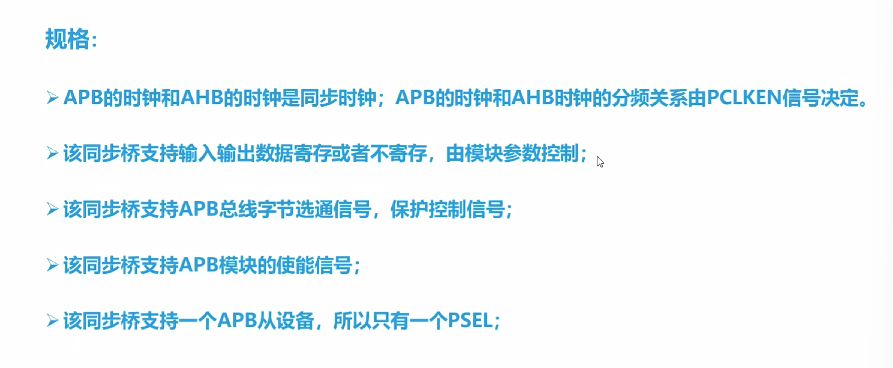

AHB2APB Bridge规格说明

- Bridge是APB总线上唯一的主机(也可以通过设计使APB支持多个Master)

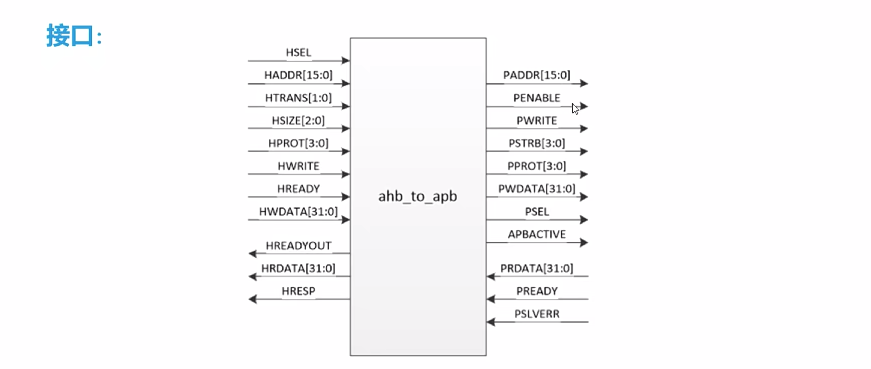

AHB2APB Bridge接口

- Bridge是连接AHB总线和APB总线的桥梁,所以接口有AHB总线和APB总线

- Bridge是APB总线的Master,是AHA的Slave

- psel - 有多少个外设就有多少个psel信号

- penable - 时钟选通信号

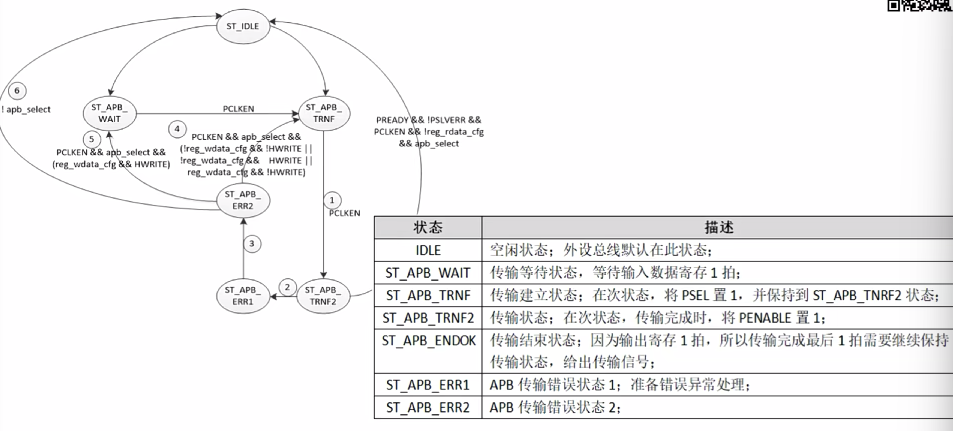

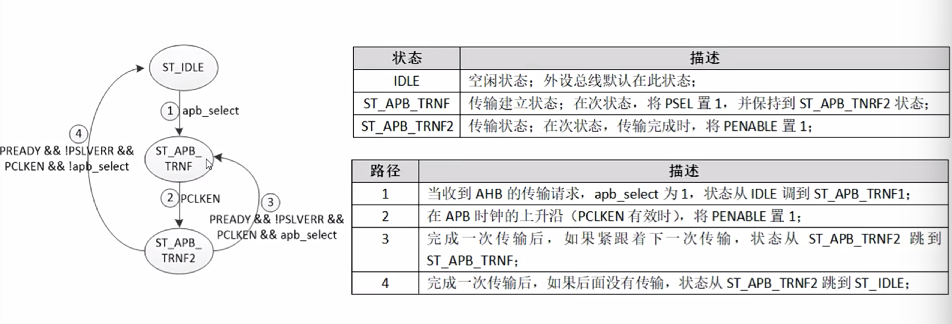

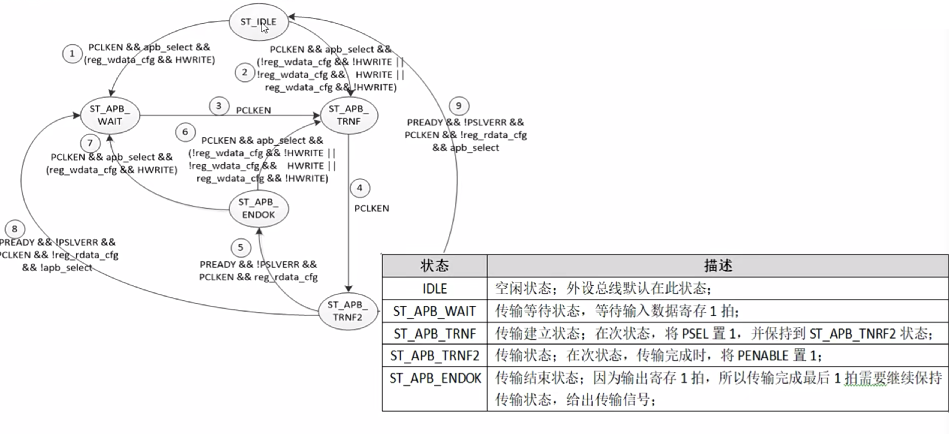

AHB2APB Bridge状态机

- Bridge开始的时候处于IDLE状态,当Bridge收到AHB总线的传输信号之后,进入到setup状态,在setup状态将AHB控制和地址信号进行锁存并将psel置于1,进入到enable状态,可以进行apb的读写操作

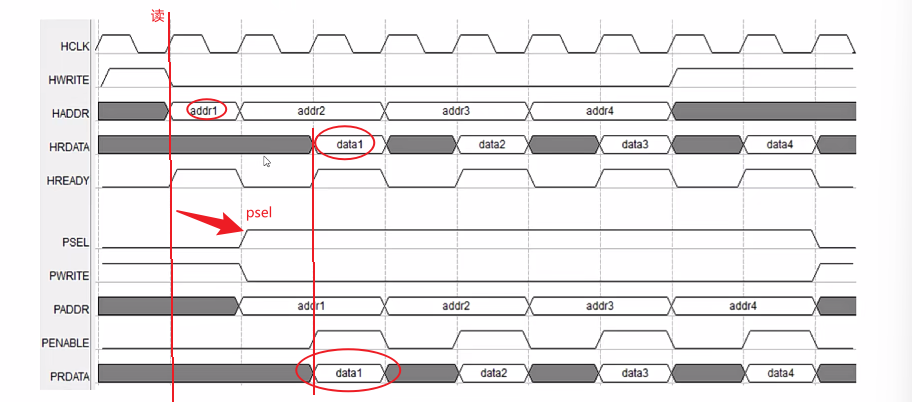

AHB2APB Bridge读时序

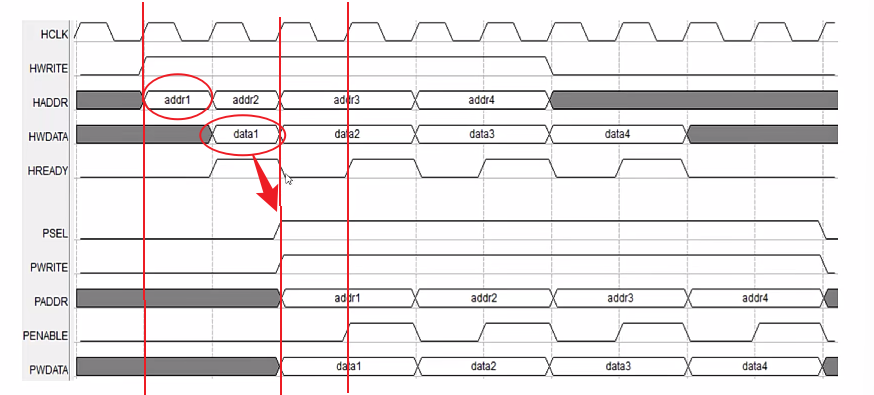

AHB2APB Bridge 写时序

AHB2APB Bridge设计

设计规格

- 对于输入输出数据进行寄存或者不寄存,由模块控制,主要是为了时序

接口信号

- APBACTIVE - APB激活信号

状态机1:输入输出不寄存

状态机2:输入输出数据寄存

状态机:发生传输错误