参考:Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog

https://zhuanlan.zhihu.com/p/359327167

https://wuzhikai.blog.csdn.net/article/details/122874278

https://www.cnblogs.com/lyc-seu/p/12441366.html

个人导航网站:yun916831.github.io

第1章 亚稳态

亚稳性是指在设计的正常操作过程中的某个时间段内,在某些时间段内未呈现稳定的0或1状态的信号。在多时钟设计中,无法避免亚稳性,但是可以抵消亚稳性的不利影响。

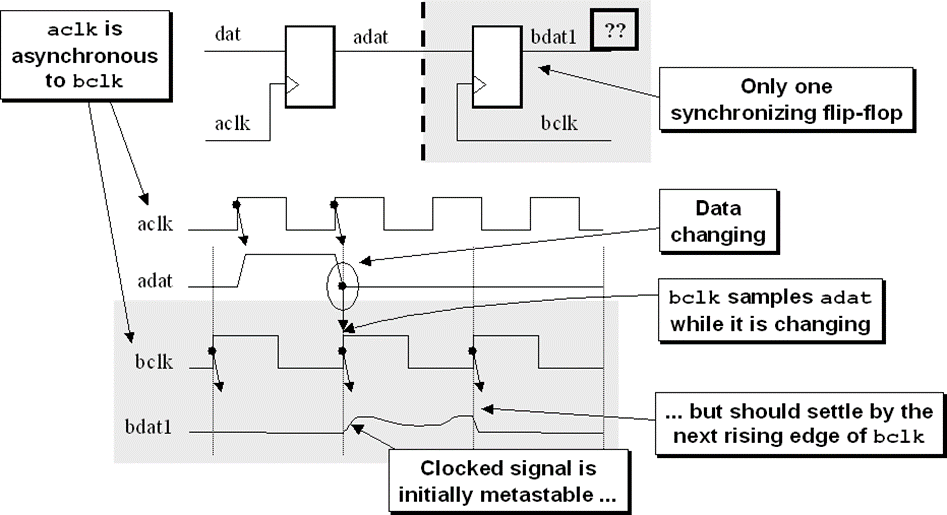

Figure 1 - Asynchronous clocks and synchronization failure

“当用时钟对不断变化的数据信号进行采样时……事件的顺序决定了结果。事件之间的时间差越小,确定哪个先发生所需的时间就越长。当两个事件非常靠近地发生时,决策过程可能需要比分配的时间更长的时间,并且会发生同步失败。”

图1显示了在一个时钟域中生成的信号被采样得太靠近来自第二个时钟域的时钟信号的上升沿时发生的同步故障。同步失败是由于输出变为亚稳态并且在必须再次采样输出时未收敛到合法稳定状态而引起的。

亚稳态的产生是由于寄存器采样不满足建立时间或保持时间要求导致的,亚稳态的产生是无法避免的,我们能做的只是想办法降低其发生的频率。在跨时钟域设计中,由于时钟域存在跨域,如果不采取手段,则会有很大概率会引入亚稳态。

1.1 亚稳态?

图2显示,穿越接收时钟域中附加逻辑的亚稳态输出会导致非法信号值在整个设计的其余部分传播。由于CDC 信号可能会波动一段时间,因此接收时钟域中的输入逻辑可能会将波动信号的逻辑电平识别为不同的值,从而将错误信号传播到接收时钟域中。

Figure 2 - Metastable bdat1 output propagating invalid data throughout the design

上图显示了当在一个时钟域(aclk)中生成的信号adat被送到了另一个时钟域(bclk)中采样,由于采样时间太靠近第二个时钟的上升沿时,发生的同步失败。同步失败是由于输出bdat1变为亚稳态,而在bdat1再次被采样时没有收敛到合法的稳定状态。

任何设计中使用的每个触发器都有一个指定的建立和保持时间,或者在时钟上升沿之前和之后数据输入不被合法允许改变的时间。这个时间窗口被精确指定为一个设计参数,以防止数据信号变化太接近另一个同步信号,从而导致输出进入亚稳态。

亚稳态最大的危害就是会将系统引入一个未知状态,对于许多设计而言,这无疑是致命的。

1.2 为什么会产生亚稳态

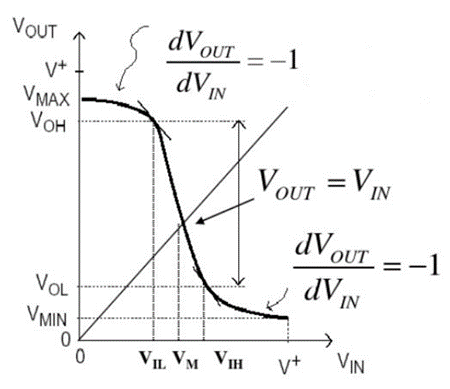

存储元件如交叉耦合反相器、SR锁存器、D锁存器和D触发器等都有两个稳定的状态,即0和1,也就是能存储0和1这两个状态。亚稳态就是既不是0又不是1的状态,或者说可能0也可能是1,不能确切知道它的状态。为什么会出现亚稳态呢?这是因为我们在分析元器件时,是把元器件抽象为理想器件以简化分析,但实际的元器件并不是理想的。比如对于一个理想的CMOS反相器的电平传输特性如下所示。

理想CMOS反相器的电平传输特性

可以看到,在0<VIN<V+/2时,VOUT=V+; 在V+/2<VIN<V+时,VOUT=0;

这里理想化的是这个变化过程,刚好在V+/2这个点就能瞬时完成“突变”,界限十分分明。但是实际上不可能是这样的,变化是有一个过程的,这种理想的器件现实世界是生产不出来的。

实际的CMOS反相器电平传输特性如下:

实际CMOS反相器的电平传输特性

可以看到:

在0<VIN<VIL时,VOH<VOUT < Vmax;

在VIH<VIN<V+时,Vmin<VOUT <VOL;

在VIL<VIN<VIH时,VOUT=VIN; (VOL<VOUT<VOH)

如果后一级的判断电路把低于VOL的电压判断为0,把高于VOH的电压判断为1,那么在输入为VIL~VIH这个范围的电压产生的VOUT后一级的电路就不能判断当前是0还是1,有可能是0,也有可能是1,不能准确预测它的输出。

补充一下,数字化电路都是二值化的,只有0和1,理想情况下,如果输入电压高于Vth那么就是1,如果低于VH就是0,Vth叫做判断阈值。但是实际情况往往不是这样的,没有一个点来作为分界线,实际的电路做不出来。实际上是高于VH才算1, 低于VL才算0,VH>VL,也就是说高阈值VH和低阈值VL之间是有一段距离的。

结合上面的分析,我们很容易就知道,数字信号跳变,0->1 或者 1->0,对应的是电压的变化,实际情况下,这个变化需要时间的。如果输入信号刚好在寄存器不能判断的区间(VL~VH),那么,输出就不能判断是0还是1,也就是亚稳态。

也就是说当输入数据不满足寄存器的建立时间或者保持时间的时候,寄存器就很可能捕捉到输入数据的电平在未定义的电平区间,输出处于亚稳态。

这里的建立时间和保持时间,就可以粗略的看作电压变化到VL或者VH所需要的时间。

不是每个违反寄存器建立保持时间的信号翻转都会导致亚稳态。一个寄存器进入亚稳态和从亚稳态进入稳态的时间依赖于制造商的制造工艺和使用环境。大部分情况下,寄存器会很快的进入一个定义的稳态中。

第2章 同步器

在时钟域之间传递信号时,要问的一个重要问题是,我是否需要对从一个时钟域传递到另一个时钟域的信号的每个值进行采样?

2.1 两种同步场景

跨CDC 边界传递信号时可能出现两种情况,确定哪种情况很重要:

允许错过在时钟域之间传递的样本。

在时钟域之间传递的每个信号都必须被采样。

第一种情况:有时不需要对每个值都进行采样,但重要的是采样值必须要准确。一个例子是标准异步FIFO设计中使用的一组格雷码计数器。在正确设计的异步FIFO 模型中,同步格雷码计数器不需要从相反的时钟域中捕获每个合法值,但至关重要的是采样值必须准确以识别何时发生满和空情况。

第二种情况:CDC 信号必须被正确识别或识别和确认,然后才允许对CDC 信号进行更改。

在这两种情况下,CDC 信号都需要某种形式地同步到接收时钟域中。

并不是所有设计都需要全部数据都被采样。例如,异步FIFO设计中,就可以允许漏采的存在。因为异步FIFO的设计最重要的是正确(或者说不错误)地判断FIFO的空和满。漏采一些数据并不会对其判断空满造成错误,某种意义上还会使其设计更加安全。

2.2 双触发器同步器

数字设计人员使用的最简单常见的同步器是双触发器同步器,如图3 所示。第一个触发器将异步输入信号采样到新的时钟域中并等待一个完整的时钟周期以允许第一阶段输出信号上的任何亚稳态衰减,然后第一阶段信号被同一时钟采样到第二阶段触发器,其预期目标是第2 阶段信号现在是一个稳定且有效的信号,同步并准备好在新的时钟域内分配。

理论上,当信号被计时到第二级以导致第二级输出信号也进入亚稳态时,第一级信号仍然可能是亚稳态。同步失败之间的时间间隔(MTBF) 概率的计算是多个变量的函数,包括用于生成输入信号和为同步触发器计时的时钟频率。

对于大多数同步应用,两个触发器同步器足以消除所有可能的亚稳态。 双触发器同步,即为经典的打两拍,可适用大多数的一般设计。

Figure 3 - Two flip-flop synchronizer

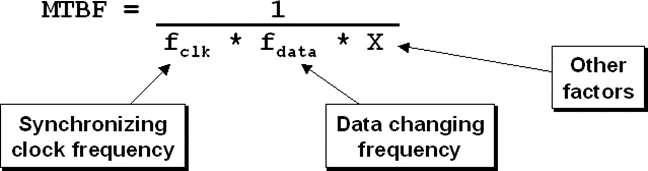

2.3 MTBF平均无故障工作时间

对于大多数应用而言,重要的是对任何跨越CDC 边界的信号运行平均无故障工作时间(MTBF) 计算。在这个意义上,失败意味着一个信号被传递到同步触发器,在第一级同步器触发器上变为亚稳态,并在一个周期后在它被采样到第二级同步器触发器时继续保持亚稳态。由于信号在一个时钟周期后并未稳定到已知值,因此在采样并传递到接收时钟域时,信号仍可能处于亚稳态,从而导致相应逻辑的潜在故障。

在计算MTBF 数字时,较大的数字优于较小的数字。较大的MTBF 数字表示潜在故障之间的时间间隔较长,而较小的MTBF数字表明亚稳态可能经常发生,同样会导致设计失败。

在不重复方程式和分析的情况下,应该指出直接影响同步器电路MTBF 的两个最重要因素是采样时钟频率(信号被采样到接收时钟域的速度)和数据更改频率(跨越CDC 边界的数据更改速度有多快)。

从上面的部分方程可以看出,在更高速度的设计中,或采样数据变化更频繁时,故障发生的频率更高(MTBF 更短)。

MTBF=etr/τ/T0fa

通常,MTBF越大说明系统采样失败的可能越小。可见,对于高速的设计,MTBF是更容易发生的。对于一个典型的 0.25µm 工艺的 ASIC 库中的一个触发器,我们取如下的参数:

tr = 2.3ns, τ = 0.31ns, T0 = 9.6as, f=100MHZ, a = 10MHZ, MTBF = 2.01 days

也就是说触发器以100MHZ工作,假设异步事件触发的频率,也就是数据变化的频率跟采样时钟频率相同。我们用10MHZ的频率去不停地采它的数据,每个上升沿数据都会发生变化,则每两天就可能采集到一次亚稳态。如果使用单锁存器同步,b的时钟上升沿采集a的数据时很可能采到亚稳态数据。

2.4 减少亚稳态的方法

亚稳态是不可避免的,这是器件的固有属性,并没有理想器件。但是我们可以减少亚稳态的发生和传播,避免亚稳态带来的消极影响。只要遵循一定的规则,即使如CPU/GPU这些超级规模的芯片,都能做到Zero-bug。

减少亚稳态的方法有以下几种:

使用同步器:也就是我们常用的2级或者多级FF打拍的方法;

降低频率:如果能满足功能要求,那么降低频率能够减少亚稳态的产生;

避免变化过快或者过于频繁的信号进行跨时钟采样;

采用更快的触发器:更快的触发器,也可以减少亚稳态的产生。

2.5 三触发器同步器

对于一些非常高速的设计,双触发器同步器的MTBF 太短,添加第三个触发器以将MTBF 增加到令人满意的持续时间。当然,满意与否是由设计师决定的。

对于军工级或其相同级别设计、或者超高速设计,又或者可靠性要求较高的设计,可能需要打三拍,或者更多拍,这个取决于设计要求或公司规定。

2.6 同步来自发送时钟域的信号

关于 CDC 设计的常见问题:在将信号传递到接收时钟域之前寄存来自发送时钟域的信号是否是个好主意?问题中隐含的假设是CDC 信号将同步到接收时钟域;因此,它们不需要在发送时钟域中同步。这种合理化是不正确的,通常应该需要在发送时钟域中寄存信号。

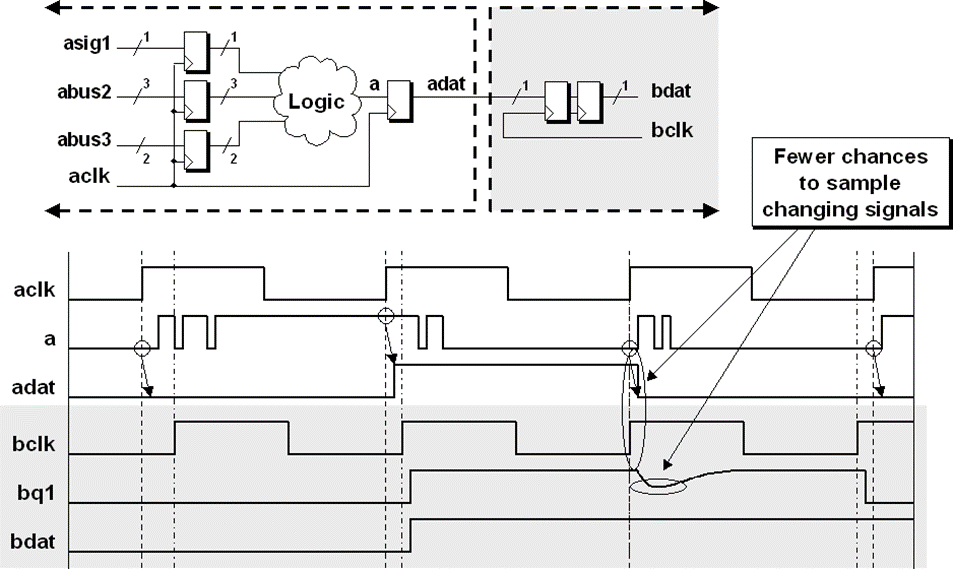

考虑一个示例,其中发送时钟域中的信号在传递到接收时钟域之前未寄存,如图6 所示。

在此示例中,发送时钟域的组合输出可能会在CDC 边界处经历组合毛刺。这种组合毛刺大大增加了数据变化频率,可能会产生少量的振荡数据突发,从而增加在变化时可以采样的边沿数量,相应地增加采样变化数据和生成亚稳态信号的可能性。

2.7 将信号同步到接收时钟域

发送时钟域中的信号在传递到CDC 边界之前应该同步。来自发送时钟域的信号同步减少了可以在接收时钟域中采样的边沿数量,有效地降低了MTBF 方程中的数据更改频率,从而增加了计算失败之间的时间数据更改频率对MTBF 的影响。

在图7 中,aclk 逻辑在被传递到bclk 域之前在adat 触发器上建立。adat 触发器滤除触发器输入(a) 上的组合毛刺,并将干净的信号传递给bclk 逻辑。

显然,在数据被同步到异步时钟域前,首先需要在自己的时钟域寄存一拍,以消除组合逻辑产生的毛刺。防止毛刺被传播到其他时钟域,从而在数据采样时存在多个边沿,造成采样失败而发生亚稳态。

Figure 6 - Unregistered signals sent across a CDC boundary

Figure 7 - Registered signals sent across a CDC boundary