1.算法仿真效果

本系统进行了两个平台的开发,分别是:

Vivado2019.2

Quartusii18.0+ModelSim-Altera 6.6d Starter Edition

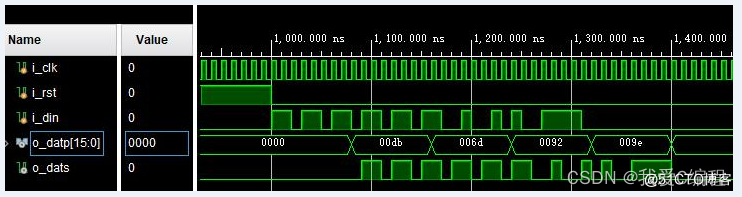

其中Vivado2019.2仿真结果如下:

分别进行2路,4路,8路,16路并行串行转换

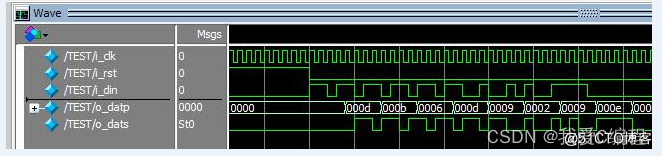

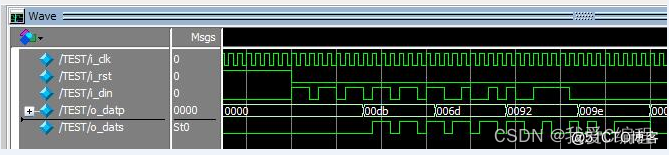

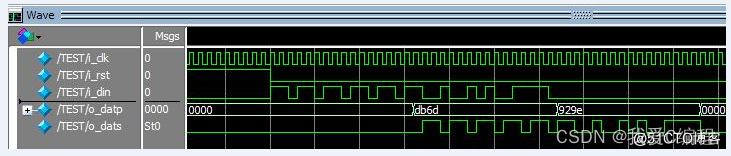

Quartusii18.0+ModelSim-Altera 6.6d Starter Edition的测试结果如下:

2.算法涉及理论知识概要

串并转换是将串行数据转换为并行数据的过程,即将一串数据按位拆分成多个并行数据。串并转换器的输入为串行数据流,输出为并行数据流。在串并转换器中,需要使用移位寄存器来存储串行数据,并使用多路选择器来选择数据位,将其输出到并行总线上。

并串转换是将并行数据转换为串行数据的过程,即将多个并行数据合并成一串数据。并串转换器的输入为并行数据流,输出为串行数据流。在并串转换器中,需要使用多路选择器来选择数据位,并使用移位寄存器来存储并行数据,将其按位合并成串行数据。

2.1 串并转换的FPGA实现

串并转换器的FPGA实现需要使用移位寄存器和多路选择器来实现。具体步骤如下:

设计移位寄存器:根据输入数据位数和输出数据位数,设计移位寄存器的大小,并将输入数据流存储到移位寄存器中。

设计多路选择器:根据输出数据位数和移位寄存器的大小,设计多路选择器的大小,并使用多路选择器选择数据位,将其输出到并行总线上。

设计时序逻辑:设计时钟控制电路和移位控制电路,控制数据的移位和选择。

设计输出接口:设计并行输出总线和输出接口,将并行数据输出到外部设备。

2.2 并串转换的FPGA实现

并串转换器的FPGA实现需要使用移位寄存器和多路选择器来实现。具体步骤如下:

设计移位寄存器:根据输入数据位数和输出数据位数,设计移位寄存器的大小,并将输入数据存储到移位寄存器中。

设计多路选择器:根据输入数据位数和输出数据位数,设计多路选择器的大小,并使用多路选择器选择数据位,将其合并成串行数据。

设计时序逻辑:设计时钟控制电路和移位控制电路,控制数据的移位和选择。

设计输入接口:设计并行输入总线和输入接口,将并行数据输入到移位寄存器中。

3.Verilog核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/05/07 19:40:52

// Design Name:

// Module Name: TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST();

reg i_clk;

reg i_rst;

reg i_din;

wire[15:0]o_datp;

wire o_dats;

s2p s2pu1(

.i_clk (i_clk),

.i_rst (i_rst),

.i_sel (2'b00),//00锛?路01:4路10鈥?路11锛?6路

.i_din (i_din),

.o_datp (o_datp)

);

p2s p2su2(

.i_clk (i_clk),

.i_rst (i_rst),

.i_sel (2'b00),//00锛?路01:4路10鈥?路11锛?6路

.i_din (o_datp),

.o_dats (o_dats)

);

initial

begin

i_clk=1'b1;

i_rst=1'b1;

#1000

i_rst=1'b0;

end

always #5 i_clk=~i_clk;

initial

begin

i_din=1'b0;

#1000

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b0;

#10

i_din=1'b0;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b1;

#10

i_din=1'b0;

#500

$stop();

end

endmodule