Verilog 数值处理,在处理除法的时候,需要注意位宽。

实例:

quotient=a/b;

reside=a%b;

module si_div(

input signed [9:0] a,

input signed [7:0] b,

output signed[9:0] quotient,

output signed[7:0] reside

);

assign quotient=a/b;

assign reside=a%b;

endmodule

仿真代码:

1 module si_div_tb; 2 reg sys_clk; 3 reg signed [9:0] a; 4 reg signed [7:0] b; 5 wire signed[9:0] quotient; 6 wire signed[7:0] reside; 7 8 initial sys_clk =1; 9 always #1 sys_clk = ~sys_clk; 10 //a = 8'h7f; 11 //b = 8'h2; 12 13 si_div si_div_test( 14 .a (a), 15 .b (b), 16 .quotient(quotient), 17 .reside(reside) 18 ); 19 initial begin 20 a=0;b=0; 21 #2 22 a=-256;b=5; 23 24 #2 25 a=253;b=-128; 26 #2 27 a=61;b=108; 28 #2 29 a=-511;b=35; 30 end 31 endmodule

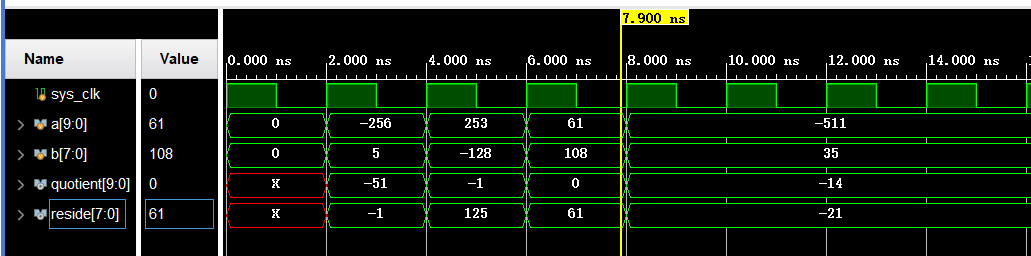

Vivado仿真结果如下:

该模块只能实现商与余数分别存储,由于存在无法整除情况,无法直接存储结果。