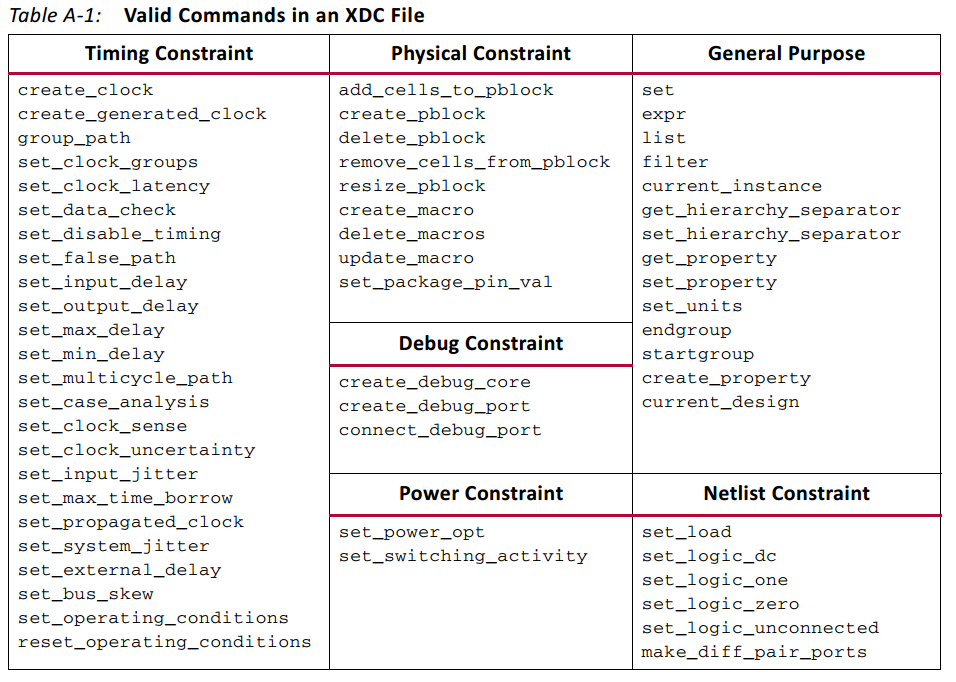

1.常见的xdc约束命令

2.对异步时钟进行时序约束

对异步时钟组和时钟域交汇进行约束

在“Clock Interaction”(时钟交互)报告中可快速明确异步关系:无公用基准时钟的时钟对或者无公共周期(未扩展)的时钟对。即使时钟周期相同,从不同时钟源生成的时钟仍为异步关系。必须仔细审查异步“Clock Domain Crossing (CDC)”(时钟域交汇 (CDC))路径以确保这些路径使用的同步电路正确,此类同步电路不依赖时序正确性,并且可以最大限度降低发生亚稳态的概率。异步 CDC 路径通常具有较高的偏差要求和/或不现实的路径要求。因此不应使用默认时序分析来对其进行时序约束,此分析无法证明其能否在硬件中正常工作。

Report CDC

Report CDC (report_cdc) 命令可执行设计中时钟域交汇的结构分析。您可使用此信息来识别潜在不安全的 CDC,此类 CDC 可能导致亚稳态或数据一致性问题。Report CDC 类似于“Clock Interaction”(时钟交互)报告,但 Report CDC 侧重于结构和相关的时序约束。Report CDC 不提供时序信息,因为时序裕量对于跨异步时钟域的路径没有意义。

Report CDC 可识别如下最常见的 CDC 拓扑结构:

单位同步装置

多位总线同步装置

异步复位同步装置

由 MUX 和 CE 控制的电路系统

同步装置前组合逻辑

多时钟扇入到同步装置

扇出到目标时钟域

如需了解有关 report_cdc 命令的更多信息,请访问此链接以参阅 Vivado Design Suite 用户指南:设计分析与收敛技巧(UG906) 中的相应内容。另请参阅 Vivado Design Suite Tcl 命令参考指南(UG835) 中的 report_cdc。

应采用特定约束以避免异步时钟域交汇上执行默认时序分析。

双向时钟间的全局约束

对应各 CDC 路径的约束

双向时钟间的全局约束

如果无需限制最大时延,即可使用时钟组。以下是忽略 clkA 与 clkB 之间的路径的示例:

set_clock_groups -asynchronous -group clkA -group clkB

当 2 个主时钟及其相应的生成时钟构成 2 个异步域,并且这 2 个异步域之间的所有路径均已正确完成同步时,即可立即对多个时钟应用时钟组约束:

set_clock_groups -asynchronous \

-group {clkA clkA_gen0 clkA_gen1 …} \

-group {clkB clkB_gen0 clkB_gen1 …}

或者直接执行:

set_clock_groups -asynchronous \

-group [get_clocks -include_generated_clock clkA] \

-group [get_clocks -include_generated_clock clkB]

对应各 CDC 路径的约束

如果 CDC 总线使用格雷编码(例如,FIFO)或者如果需要限制 1 个或多个信号上的 2 个异步时钟之间的时延,则必须使用 set_max_delay 约束及 -datapath_only 选项来忽略这些路径上的时钟偏差和抖动,并覆盖时延要求的默认路径要求。通常使用源时钟周期作为最大延迟值就足够了,这只是为了确保在任意给定时间,CDC 路径上最多仅存在一项数据。

当时钟周期之间的比率较高时,选择源时钟周期和目标时钟周期的最小值同样足以降低传输时延。简单标准的异步 CDC 路径的源时序单元与目标时序单元之间不应存在任何逻辑,因此实现工具很容易就可以满足“Max Delay Datapath Only”(仅最大延迟数据路径)约束。

某些异步 CDC 路径要求在总线的各个位之间施加偏移控制,而无需对总线时延施加约束。使用总线偏移约束可防止接收时钟域在同一时钟沿上锁存总线的多个状态。您可使用 set_bus_skew 命令来对总线设置总线偏移约束。例如,您可将 set_bus_skew 应用于使用格雷编码代替“Max Delay Datapath Only”(仅最大延迟数据路径)约束的 CDC 总线。欲知详情,请访问此链接以参阅 Vivado Design Suite 用户指南:使用约束(UG903) 中的相应内容。

对于不需要时延控制的路径,您可定义 1 个点对点伪路径约束。

时钟例外相对于 set_max_delay 的优先顺序

编写 CDC 约束时,请验证是否遵循相应的优先顺序。如果在 2 个时钟之间至少 1 条路径上使用 set_max_delay -datapath_only,那么无法在相同时钟之间使用 set_clock_groups 约束,并且只能在 2 个时钟之间的其他路径上使用 set_false_path 约束。