! https://zhuanlan.zhihu.com/p/675099851

本系列是lpddr5x spec的分享。

spec版本:JESD209-5B。

4 LPDDR5X:初始化和训练

4.1 上电、初始化和下电流程

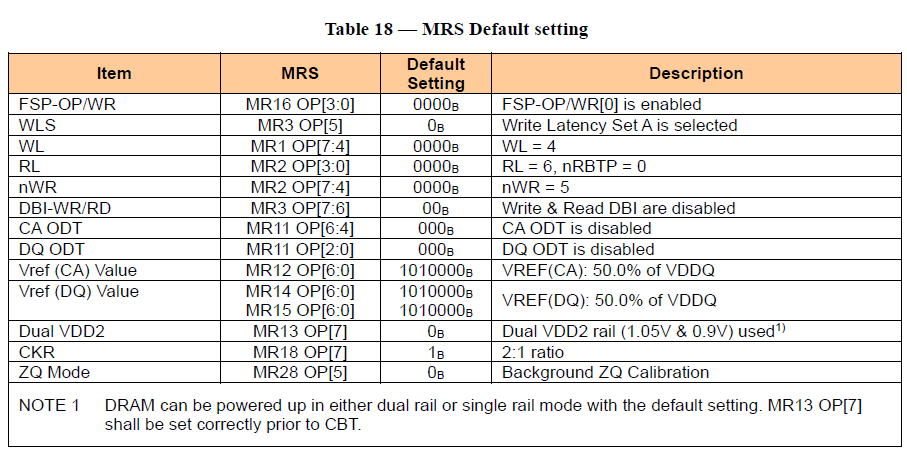

上电和复位初始化时,避免DRAM功能异常,按照下表默认值设置MR。

4.1.1 电压爬坡和器件初始化

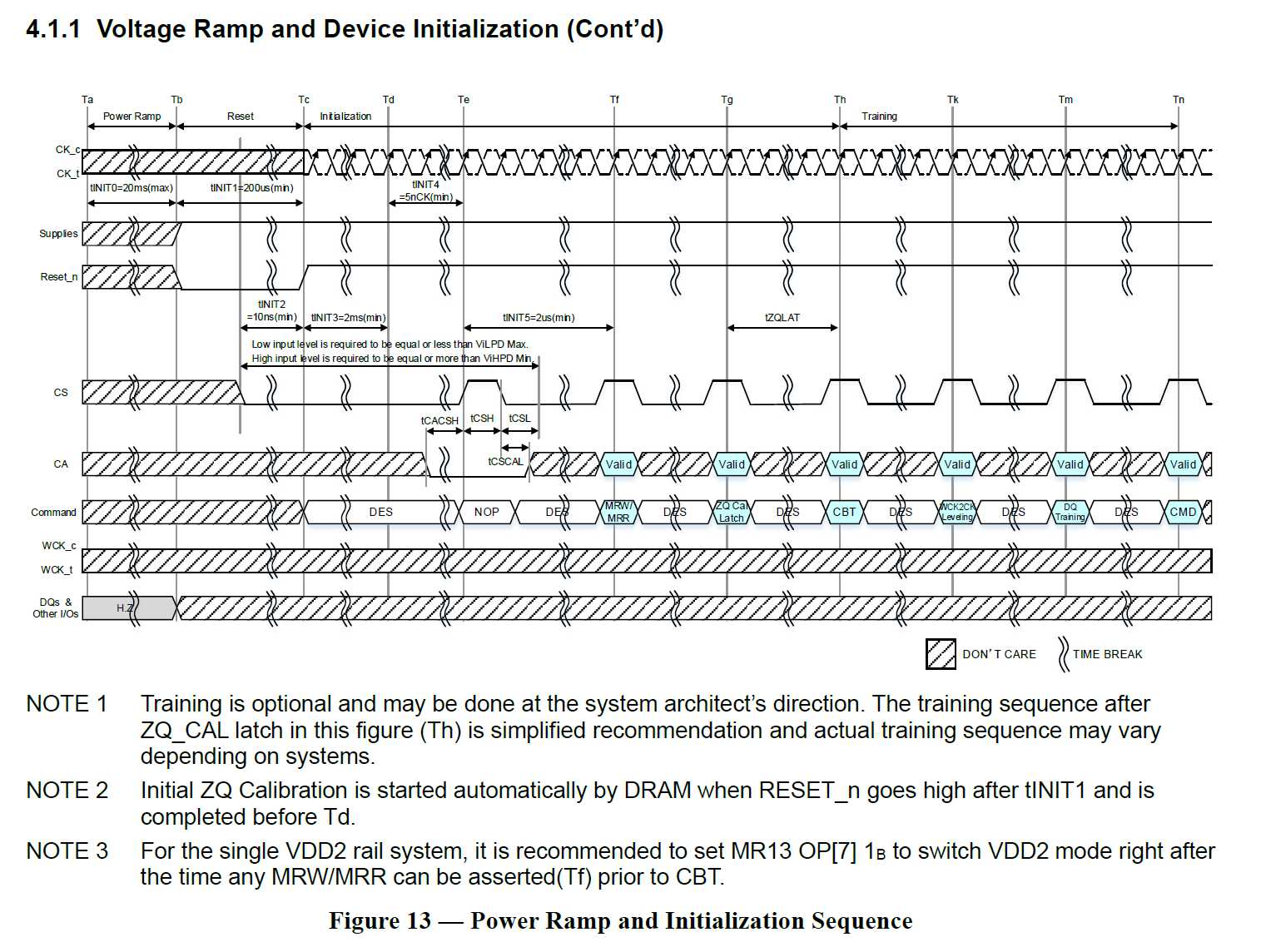

采用以下序列上电LPDDR5,除非特别指定,否则这些步骤是强制性的。

1)上电后(Ta时间后),RESET_n建议保持低电平(<= 0.2 x VDD2H),且其他所有的输入端口保持在VILmin和VIHmax之间。当RESET_n保持低电平时,SDRAM的输出处在高阻状态。表19提供了电源爬坡要求,VDD1必须比VDD2H早上电或2个同时上电。VDD2H必须比VDD2L早上电或同时上电。VDD2L必须比VDDQ早上电或同时上电。

2)电压爬坡完成后(Tb时间),RESET_n必须保持低电平。电压爬坡期间,DQ、DMI、WCK_t和WCK_c、RDQS_t、CK_t、CK_c和CA的电压必须在VSS和VDDQ之间,避免latch-up。CS的电平要求 <= ViLPD的最大值,防止开始点tINIT2(后面会介绍)之前出现故障。

3)从Tb时间开始,RESET_n必须保持低电平至少tINIT1时间(Tc),之后RESET_n可以解置位为高电平。

4)几乎在RESET_n解置位的同时,CK_t和CK_c需要开始翻转且电平互补。

5)在CS引脚接收到1个触发(Te时间)之前,CK_t和CK_c要求开始翻转(Td)且稳定到tINIT4。

6)tINIT4时间之后,至少等待tINIT5时间后才发起任何MRR或MRW命令(Tf)。当发起第1个命令时(Tf),时钟频率必须在定义的tCKb范围内。

在系统被正确配置完之前,一些AC参数(比如tWCKCK)可能放宽时序要求(比如tWCKCKb)。

7)由于LPDDR5在上电爬坡后自动完成初始化Z Q校准,所以应该发出ZQ Latch命令。在满足tZQLAT(Th)之后,command bus(内部的VREF(CA

Q校准,所以应该发出ZQ Latch命令。在满足tZQLAT(Th)之后,command bus(内部的VREF(CA

)、CS和CA)应该通过发出MRW命令(Com mond Bus Training Mode)来训练到更高速度。该命令用于校准SDRAM的内部VREF,并将CS/CA与CK进行对齐,以实现高速运行。LPDDR5 SDRAM将于配置为低速操作的接收器一起上电,VREF(CA)设置为默认的出场设置。在command bus训练完成之前,可能无法在比tCKb更高的时钟速率下完成正常的SDRAM操作。

mond Bus Training Mode)来训练到更高速度。该命令用于校准SDRAM的内部VREF,并将CS/CA与CK进行对齐,以实现高速运行。LPDDR5 SDRAM将于配置为低速操作的接收器一起上电,VREF(CA)设置为默认的出场设置。在command bus训练完成之前,可能无法在比tCKb更高的时钟速率下完成正常的SDRAM操作。

/blog/3364937/202401/3364937-20240102004026964-268709136.png)

备注:command bus 的training MRW命令使用CA bus作为输入,进行校准数据流的操作,在DQ bus上异步输出结果。4.2.2章节详细描述如何进入和退出训练模式(training mode)。

8) 在command bus训练之后,DRAM控制器必须执行WCK2CK调频,当MR18-OP[6]寄存器配置为高时(Tk时间),使能WCK2CK调频模式。4.2.5.2章节详细描述了WCK2CK调频进入和退出序列。在完成WCK2CK调频后,确定tWCK2CK,即确定CK到WCK的关系,并进行WCK和CK的同步。该过程是以优化后的裕量执行该操作。

9)

未完待续,点个关注,笔者会坚持每周往下更新。