1.算法仿真效果

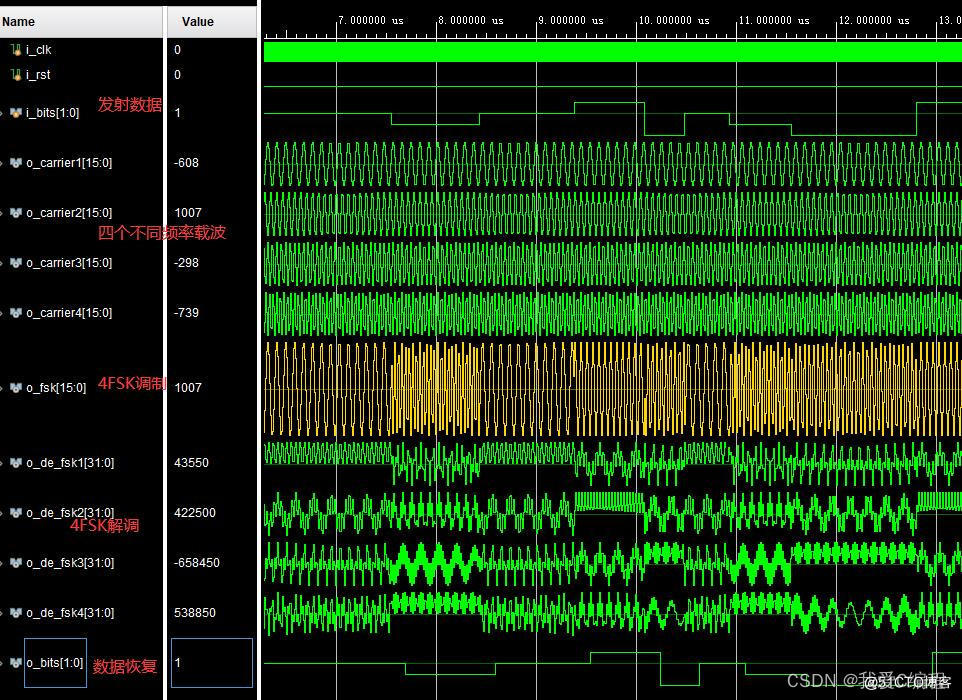

vivado2019.2版本开发,仿真结果如下:

2.算法涉及理论知识概要

四频移键控(4FSK)是一种常用的数字调制方法,具有较高的频带利用率和抗干扰性能。它利用不同的频率来传输二进制数据,通常应用于无线通信和数据传输等领域。

2.1、原理与数学公式

4FSK调制的基本原理是将输入的二进制数据转换为不同频率的信号,以实现数据的传输。解调则是将接收到的不同频率的信号还原为原始的二进制数据。

在4FSK调制中,输入的二进制数据被分为两组,每组有两个比特。根据这两个比特的值,选择相应的频率输出。具体来说,有四个频率f1、f2、f3、f4与之对应,每个频率都代表一个二进制组合(00、01、10、11),即十进制的0,1,2,3。

频率选择:根据输入的比特组合选择相应的频率输出。例如,当输入为“00”时,选择频率f1;当输入为“01”时,选择频率f2;当输入为“10”时,选择频率f3;当输入为“11”时,选择频率f4。

调制信号:将选择的频率进行幅度调制,以便在传输过程中具有更好的抗干扰性能。通常采用开关键控(OOK)或脉冲幅度调制(PAM)等方法进行幅度调制。

解调信号:在接收端,根据不同频率的信号进行解调。首先通过带通滤波器将所需的频率信号提取出来,然后通过解调器将其还原为原始的二进制数据。解调方法通常采用相干解调或非相干解调。

2.2、FPGA实现过程

基于FPGA的4FSK调制解调系统实现过程如下:

输入数据流:首先,将输入的二进制数据流分为两组,每组两个比特。可以使用一个时钟信号来同步数据的输入。

频率选择:根据每组两个比特的值,选择相应的频率输出。可以使用一个4输入的MUX来实现频率选择功能。根据输入的比特组合选择相应的频率输出信号。

传输信号:将调制后的信号通过发射器发送出去。在这个过程中,可能需要添加一些滤波器和其他信号处理模块来优化传输性能。

接收信号:在接收端,接收到信号后首先通过滤波器将所需的频率信号提取出来。这个过程可以通过FPGA上的数字滤波器实现。

解调信号:将滤波后的信号送入解调器进行解调。可以使用Verilog中的相关模块来实现解调功能。例如,通过检测脉冲信号的上升沿和下降沿来确定解调的比特值。

通过将FPGA的高速度和并行性特点与4FSK调制解调技术相结合,可以实现高速、高效的数字通信系统。这种实现方法具有广泛的应用前景,可以应用于无线通信、数据传输、物联网等领域。

3.Verilog核心程序

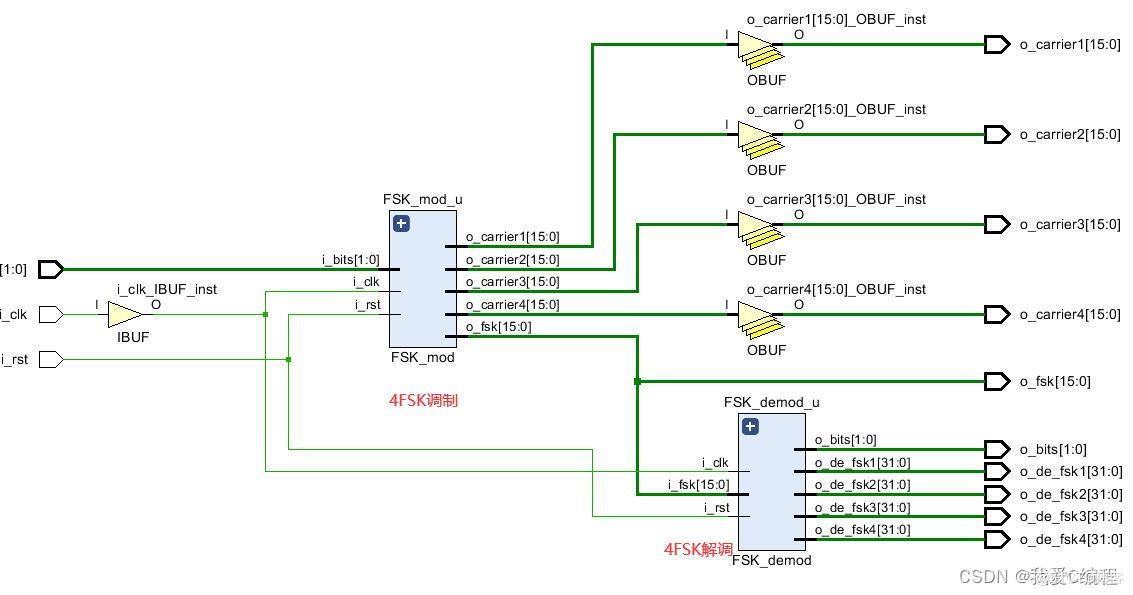

系统RTL结构如下:

`timescale 1ns / 1ps

//

//

module FSK(

input i_clk,

input i_rst,

input[1:0]i_bits,

output signed[15:0]o_carrier1,

output signed[15:0]o_carrier2,

output signed[15:0]o_carrier3,

output signed[15:0]o_carrier4,

output signed[15:0]o_fsk,

output signed[31:0]o_de_fsk1,

output signed[31:0]o_de_fsk2,

output signed[31:0]o_de_fsk3,

output signed[31:0]o_de_fsk4,

output [1:0]o_bits

);

//调制

FSK_mod FSK_mod_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_bits (i_bits),

.o_carrier1(o_carrier1),

.o_carrier2(o_carrier2),

.o_carrier3(o_carrier3),

.o_carrier4(o_carrier4),

.o_fsk (o_fsk)

);

解调//解调//解调//解调//解调//解调//解调//解调//解调//解调//解调//解调//解调

FSK_demod FSK_demod_u(

.i_clk(i_clk),

.i_rst(i_rst),

.i_fsk(o_fsk),

.o_de_fsk1(o_de_fsk1),

.o_de_fsk2(o_de_fsk2),

.o_de_fsk3(o_de_fsk3),

.o_de_fsk4(o_de_fsk4),

.o_de_ffsk1(),

.o_de_ffsk2(),

.o_de_ffsk3(),

.o_de_ffsk4(),

.o_bits(o_bits)

);

endmodule