减法器

半减器

半减器用于计算两比特Xi和Yi的减法,输出结果Di和向高位的借位Bo(Borrow output)。其真值表、逻辑表达式、Verilog描述和门电路图如下:

module half_subtract( input xi, input yi, output di, output bo); assign di=xi^yi; assign bi=(~xi)&yi; endmodule

Di=Xi⊕Yi;Bo=Xi’Yi

|

输入 |

输出 |

||

|

Xi |

Yi |

Di |

Bo |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

2.2 全减器

全减器不同于半减器在于,全减器输入来自低位的借位Bi(Borrow input),另外两个输入Xi,Yi,输出为Di和向高位的借位Bo。其真值表、逻辑表达式、Verilog描述和门电路图如下:

module full_subtract( input xi, input yi, input bi output di, output bo); assign di=xi^yi^bi; assign bi=(~xi)&bi | (~xi)&yi | yi&bi ; endmodule

|

输入 |

输出 |

|||

|

Xi |

Yi |

Bi |

Di |

Bo |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

Di= Xi⊕Yi Bi;

Bo=Xi' Bi+Xi'Yi+YiBi

减法器可以用对输入取补码,然后按照加法计算。

D=A-B=A+(~B+1);

利用全减器设计减法器

module cbs #(width=16)(

input [width-1 : 0] X,

input [width-1 : 0] Y,

input Bi,

output [width-1:0] D,

output Bo

);

wire [width:0] B_temp;

assign B_temp[0]=Bi;

assign Bo=B_temp[width];

genvar i; generate

for(i==0;i<width;i++)begin

full_subtract u_full_sub(

.xi( X[i] ),

.yi( Y[i] ),

.bi(B_temp[i] ),

.di( D[i] ),

.bo(B_temp[i]) );

end

endgenerate

endmodule

行波进位执行加减法

module rca_as #(width=16)(

input [width-1 : 0] op1,

input [width-1 : 0] op2,

input is_add_sub,

output [width-1:0] sum,

output cout

);

wire [width:0] temp;

wire [width-1:0] op2_xor;

assign temp[0]=is_add_sub; //0:add;1:sub;

op2_xor={width{is_add_sub}}^op2;

assign cout=temp[width]^is_add_sub;

genvar i; generate

for(i==0;i<width;i++)begin

full_adder u_full_add(

.a( op1[i] ),

.b( op2_xor[i] ),

.cin(temp[i] ),

.cout( temp[i+1] ),

.s(sum[i])

);

end

endgenerate

endmodule

根据此1bit全减器参考行波进行加法器即可搭建16比特减法器,如下图所示,姑且称之为行波借位减法器。

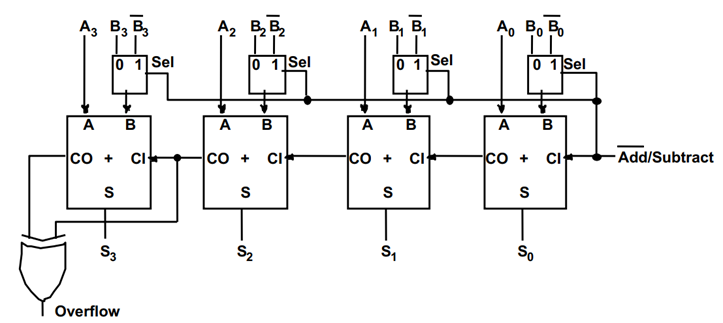

“行波借位减法器”,除了使用半减器和全减器搭建减法器外,借助二进制补码,减法器使用控制信号便可以与加法器共用相同的结构。X与Y均采用二进制补码表示,则:D=A-B=A+(~B+1); 其中~B表示对B按比特取反。

异或门也可以用二选一mux实现: