VCS代码保护

在新思公司的一些vip的实现中,一些代码进行了加密,导致无法查看源码,加密的方法也是使用新思的工具VCS。

在编译的命令行添加+protect选项,在代码前后加上编译指示,则生成对应的加密vp、svp文件,中间的部分被加密。

https://blog.csdn.net/woodhorse007/article/details/524455/

`protect

always @(posedge clk)

...

`endprotect

SOC中的复位电路

https://blog.csdn.net/l471094842/article/details/103141918

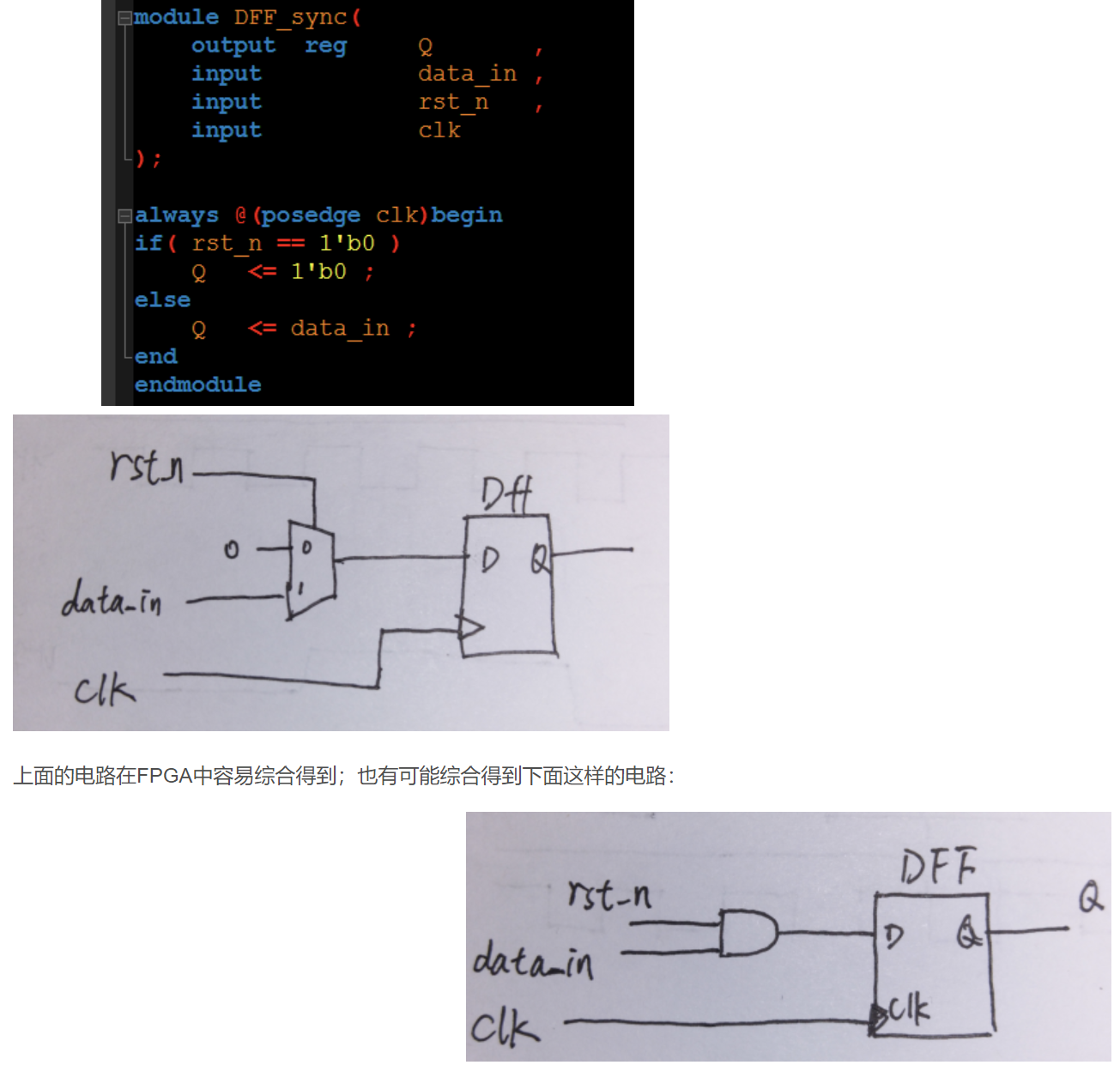

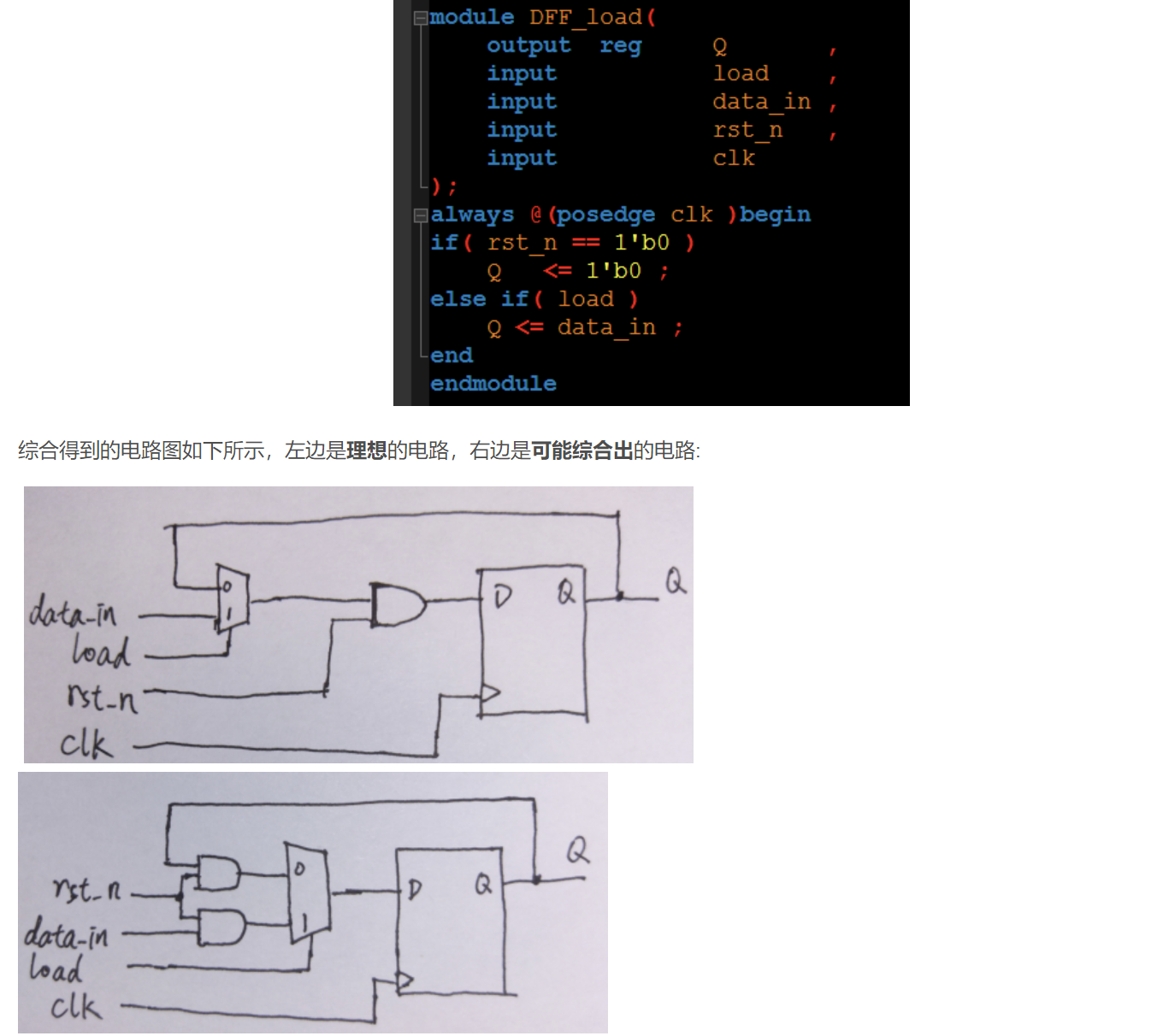

这部分内容其实和综合(RTL和代码的对应关系有关)

同步复位的优点

- 综合出来的电路简单

- 过滤复位毛刺

同步复位的缺点

- 同步复位电路在综合以后,复位信号本身需要更靠近触发器。否则,当rst_n变化的速度晚了一点,而data_in和load的速度早,则容易直接通过触发器获得data_in和load的变化,却忽略了rst_n的作用。该问题需要综合工具处理。

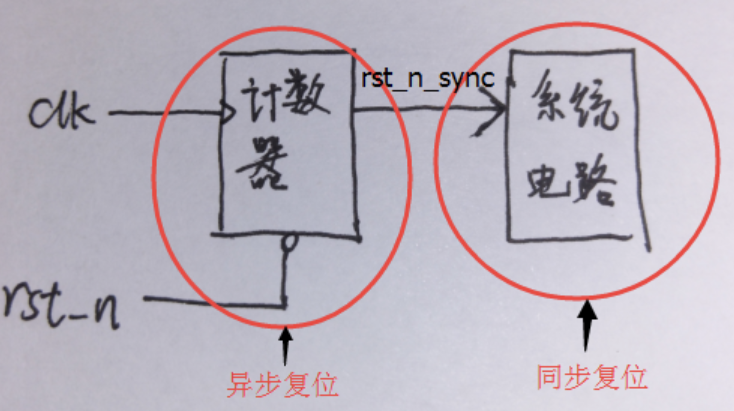

- 有时候需要让复位毛刺(复位时间不满足)生效的时候,需要额外补充电路,如计数器电路。

- 门控时钟可能无效掉同步复位,导致复位已经拉起,但是输出值仍然保持原值,输出值没有被复位。(毕竟复位的有效依赖于时钟的使能)

- 初始上电时候,由于同步复位依赖于时钟,但是始终可能未启动,则导致端口处于x态,可能引发多个端口竞争同一端口情况,烧坏电路。需要额外补充保护电路。

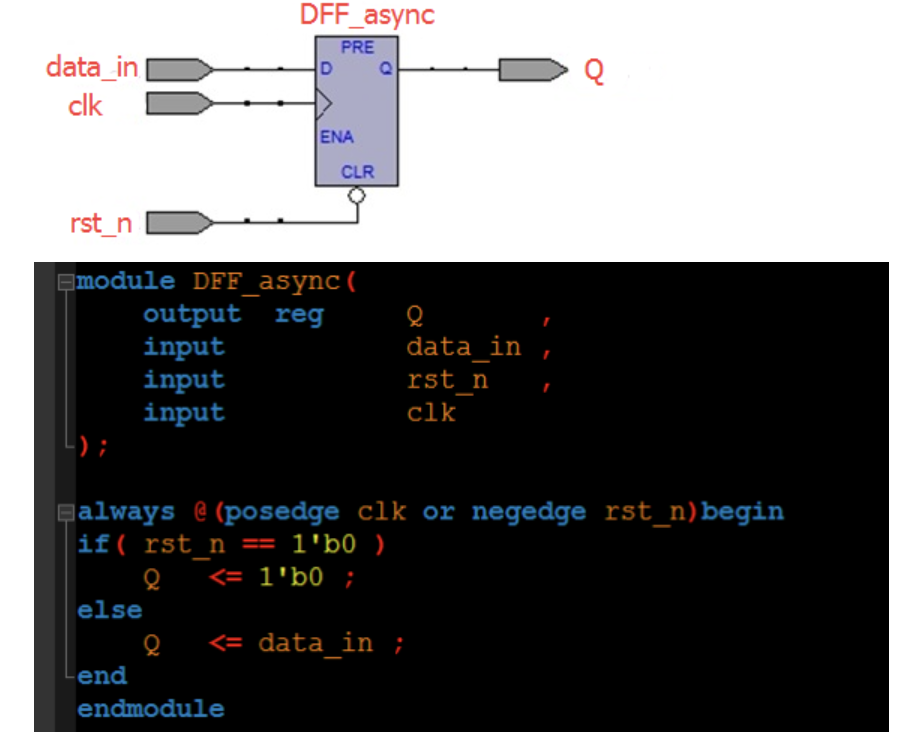

异步复位的优点

- 异步复位必定直连触发器,不出现同步复位的门延时影响。也不受时钟影响,和时钟没有关联

异步复位的缺点

- 复位信号在取消复位的时候,需要和时钟联动,满足建立保持时间,以确保是否在某个时钟采样边沿使得复位取消生效,或者不生效。

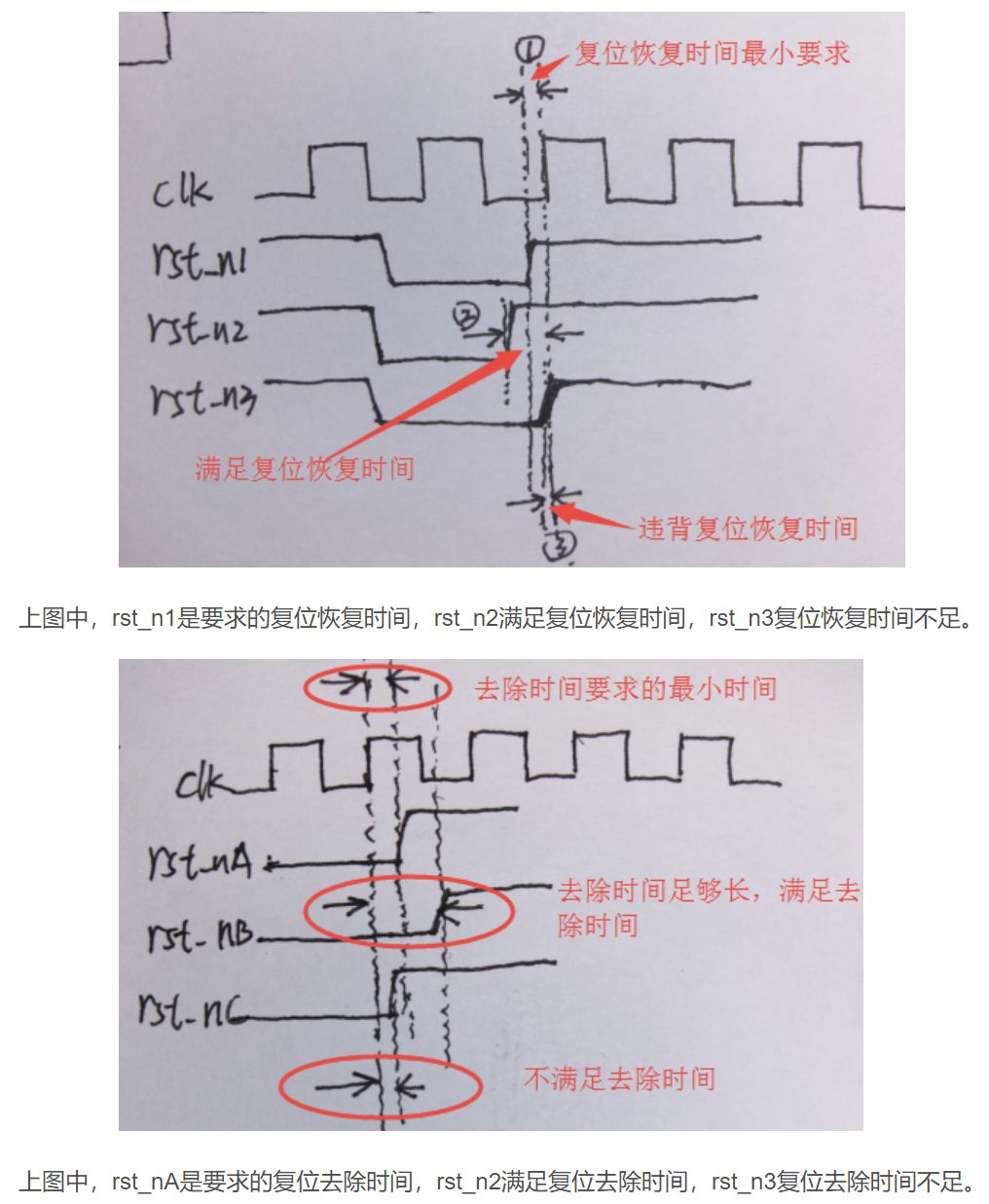

下面第一个图中,在上升沿的时候,如果想要后一个上升沿生效,能够正常采样数据,则复位的取消应该提前一定时间,否则复位信号的取消不一定被时钟发现,预期效果可能不同。

下面第二个图中,在上升沿的时候,如果想要当前上升沿已经触发复位,则复位应该保持一定的时间,否则复位是否生效可能和预期不同。

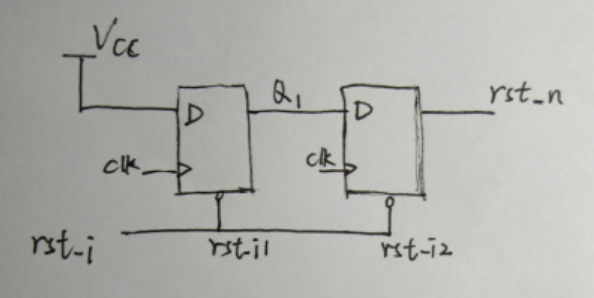

为了缓解复位信号在取消复位时候的问题,引入两级触发器,其中的输出rst_n和时钟进行过二级同步(常用消除亚稳态的方法吧),rst_n送出后,异步复位的取消复位,总在时钟上升沿后送出,这样似乎满足了取消复位的条件,将在下一个时钟边沿获得取消复位的效果。

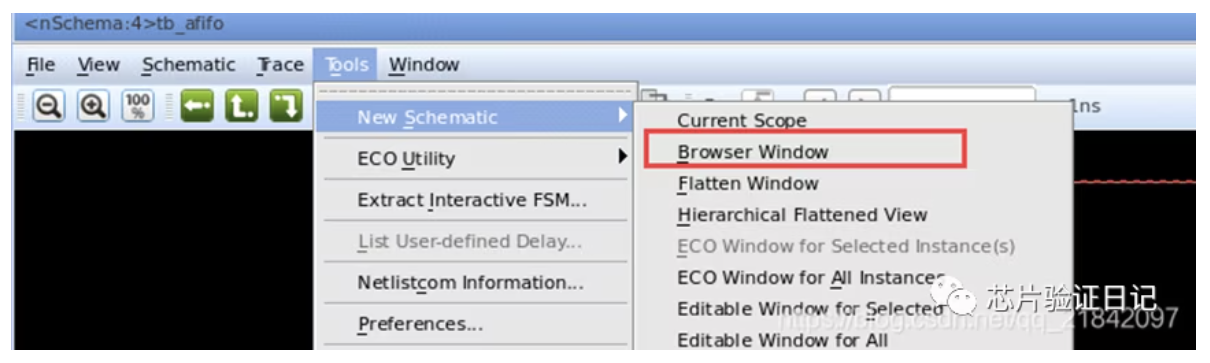

verdi生成部分原理图

用来查看与选择特定信号有关的逻辑/模块

选择需要查看的信号(可以通过shift键来选择多个信号),创建新原理图,浏览窗口。

nSchema还有其他很多功能,在view下选择可视化部分,在schematic下查找某个信号,在tools追踪信号等。

具体查看链接,关于nschema的部分。

https://www.eet-china.com/mp/a194262.html

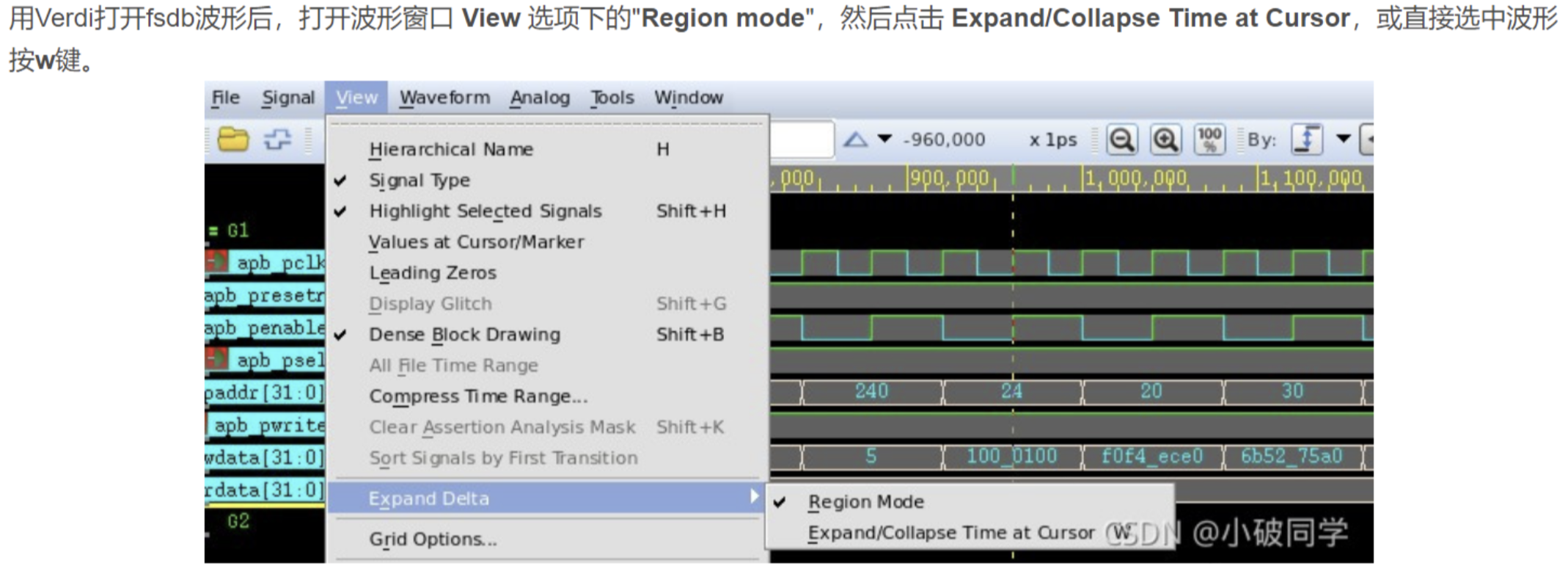

verdi查看delta cycle

在使用VCS仿真时,可以在仿真simv命令后添加选项 +fsdb+region。

然后打开verdi,在nwave窗口下,打开view下的expand delta即可。

自定义的原语Primitives UDP

用于做仿真。Verilog数字系统设计教程 440页。

https://www.cnblogs.com/alifpga/p/8078555.html

格式为:

primitive<元件名称>(<输出端口名>,<输入端口名1>,输入端口名1>...输入端口名n>);

输出端口类型声明(output);

输入端口类型声明(input);

输出端口寄存器 变量说明(reg);

元件初始状态说明(initial);

table

<table 表项1>;

<table 表项2>;

......

<table 表项n>;

endtable

endprimitive

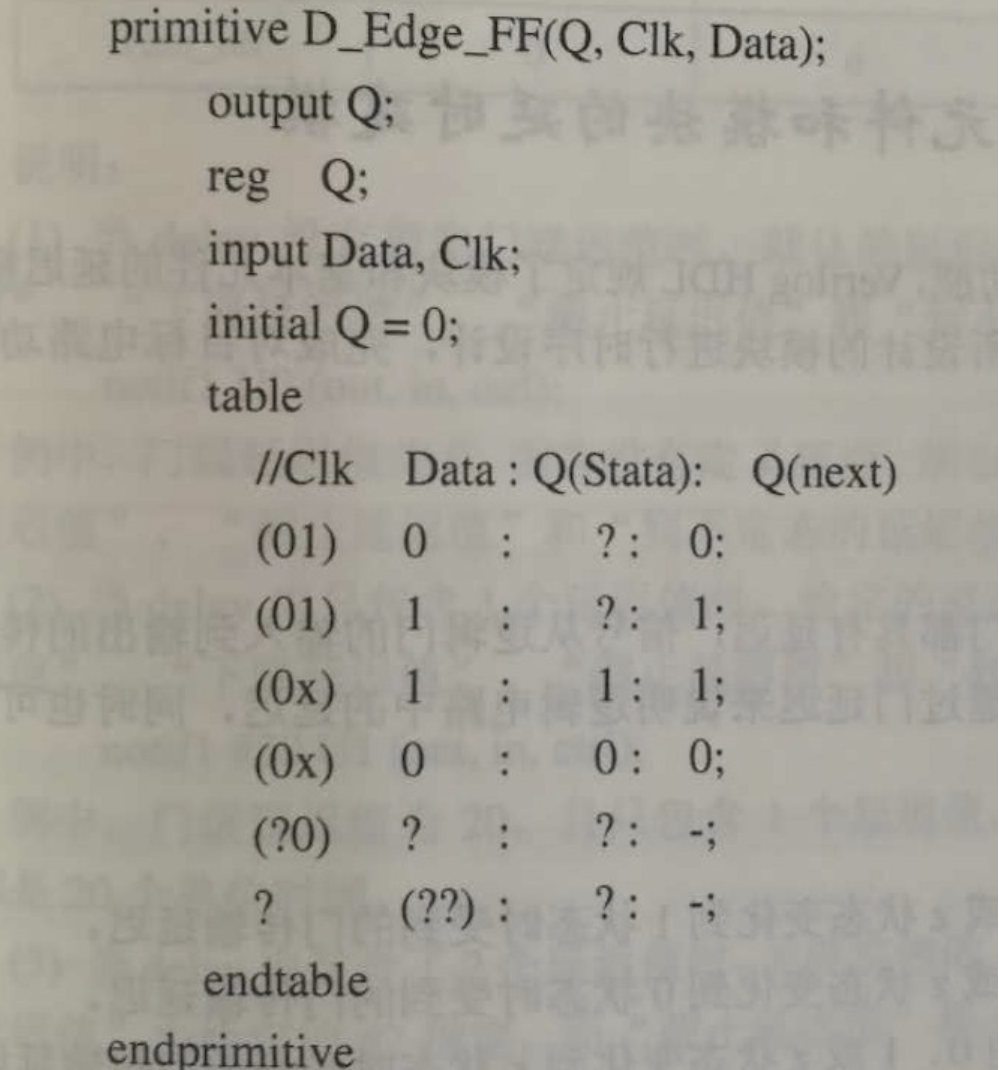

例子:

符号说明:

assert和cover

https://www.cnblogs.com/csjt/p/15593875.html

这两个功能我都不用。感觉不到断言相比于task,在验证上的优势。

assert是执行了这段断言并且成功了就会覆盖,否则报错,当需要用断言去验证时序正确性的时候,可以用assert; cover则是执行了这段断言,成功就覆盖,没成功不会报错,当用断言去覆盖时序的异常场景时,可以用cover;

specify和路径延迟

https://www.runoob.com/w3cnote/verilog2-specify.html

basic

module and4(

output out,

input a, b, c, d);

specify

specparam ab_2_out = 2.5 ;

specparam cd_2_out = 2.5 ;

(a => out) = ab_2_out ;

(b => out) = ab_2_out ;

(c => out) = cd_2_out ;

(d => out) = cd_2_out ;

endspecify

wire an1, an2 ;

and (an1, a, b);

and (an2, c, d);

and (out, an1, an2);

endmodule

if和ifnone

specify 中的 if 语句不能使用 else 结构,可以使用 ifnone 描述条件缺省时的路径延迟。

specify

if (a) (a => out) = 2.5 ;

if (~a) (a => out) = 1.5 ;

if (b & c) (b => out) = 2.5 ;

if (!(b & c)) (b => out) = 1.5 ;

if ({c, d} == 2'b01)

(c,d *> out) = 3.5 ;

ifnone (c,d *> out) = 3 ;

endspecify

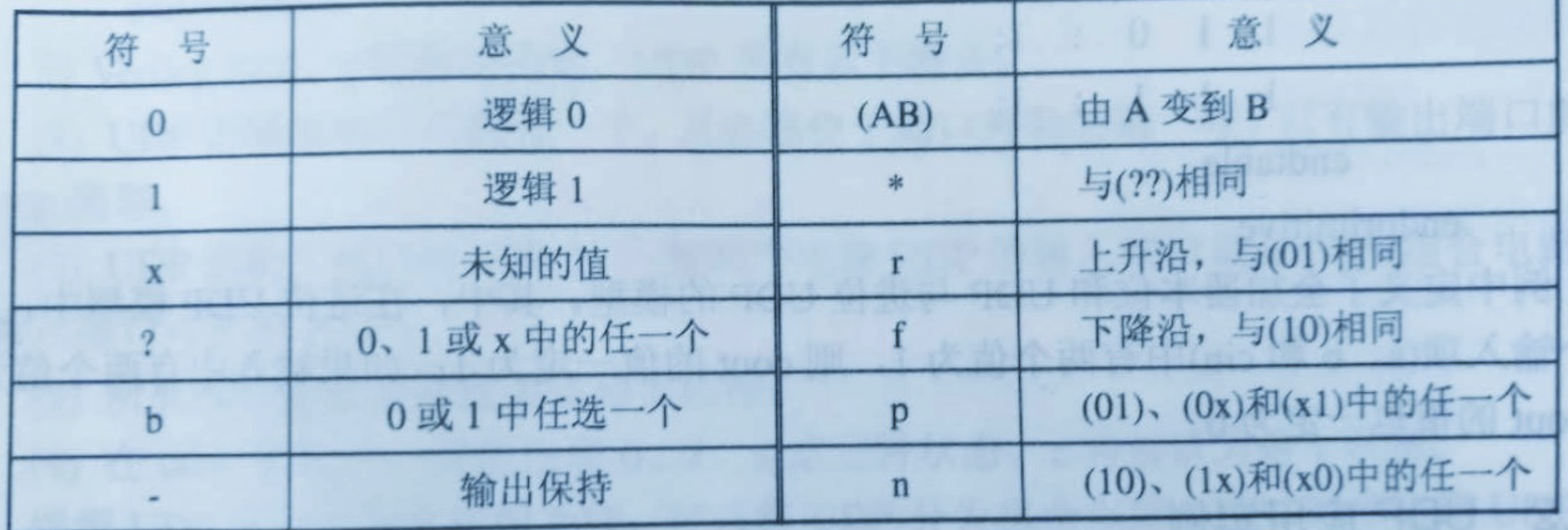

gate_path

门延迟(上升延迟、下降延迟、关断延迟)的数值也可以通过路径延迟的方法来描述。

module gate_path(

input d,

input clk ,

output reg q);

//min/typical/max

specify

specparam t_rise = 1:1.5:1.8;

specparam t_fall = 1:1.8:2 ;

specparam t_turnoff = 1.1:1.2:1.3 ;

(clk => q) = (t_rise, t_fall, t_turnoff) ;

endspecify

always@(posedge clk)

q <= d ;

endmodule

全连接

用星号,而不是等号

module and4(

output out,

input a, b, c, d);

specify

(a,b *> out) = 2.5 ;

(c,d *> out) = 3.5 ;

endspecify

wire an1, an2 ;

and (an1, a, b);

and (an2, c, d);

and (out, an1, an2);

endmodule

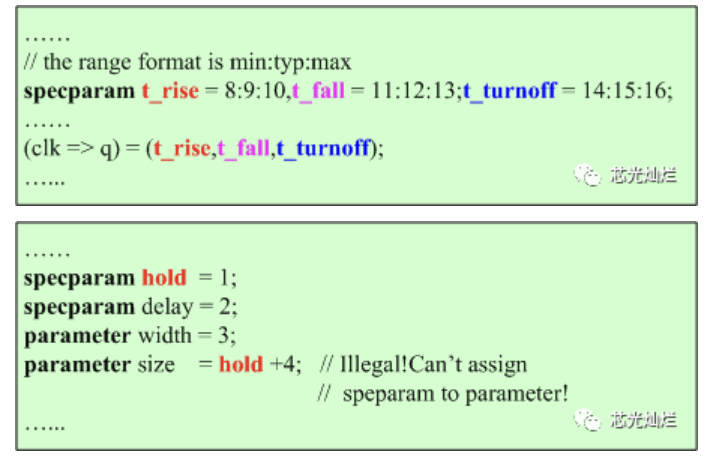

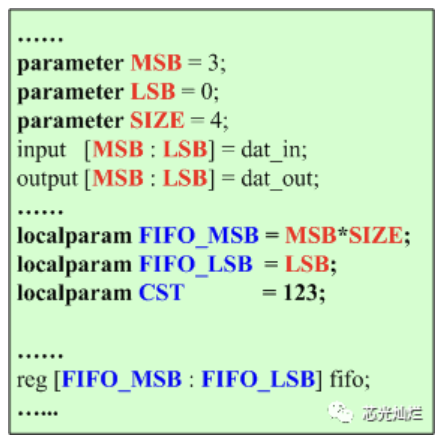

参数三姐妹-parameter-localparam-specparam

https://www.cnblogs.com/xgcl-wei/p/9090918.html

-

specparam参数,可在模块(module)内或specify块内使用,可以通过specparam或者parameter指定的参数赋值,常用于时序约束,在本模块中声明定义,用于specify块,还能指定范围。

-

parameter参数,在本模块中声明定义,常用于模块间参数传递,通过defparam或者模块例化修改原参数值。

localparam参数,只能通过parameter参数赋值,不可直接进行参数传递,在本模块中声明定义 -

localparam参数,在本模块中声明定义,不可直接进行参数传递,不能通过defparam进行修改,只能通过修改parameter的值间接修改。

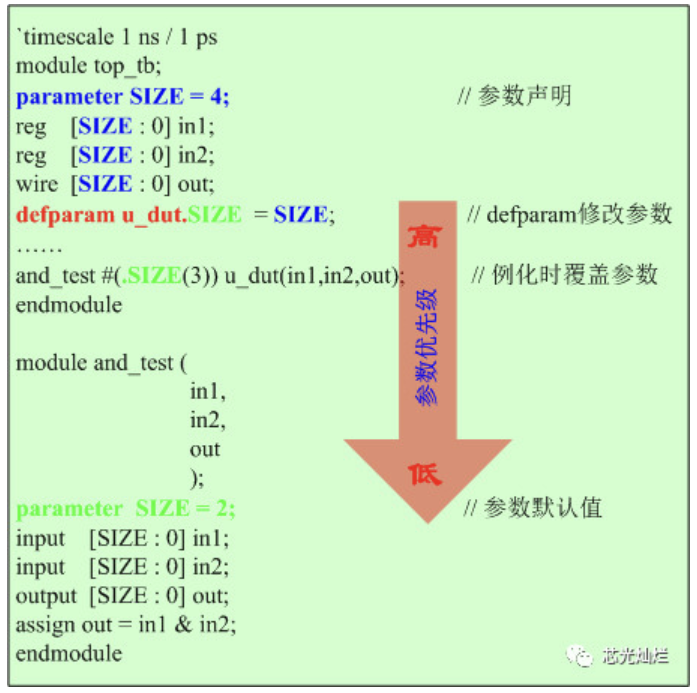

时间单位和时间精度的打印

timescale中包括两部分:时间单位和时间精度。

在一个验证环境中,有多个timescale,不论先后顺序,\(realtime以其中的最小的时间精度精度为单位,打印出数字。 注意,\)realtime拿到的数字本身是带有时间单位的,该单位是最小时间精度的单位。

在一个验证环境中,有多个timescale,关系到先后顺序,其中定义出的浮点数字所表示的时间单位,是该scope使用的时间单位。

当$realtime拿到的数字和手动写的浮点数字做比较,本身会依据各自的时间单位做转换后,以时间本身做比较,而不是以打印出来的值做比较。最终得到比较结果。