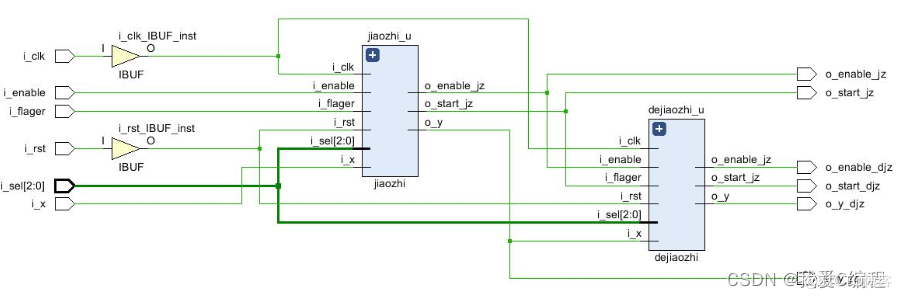

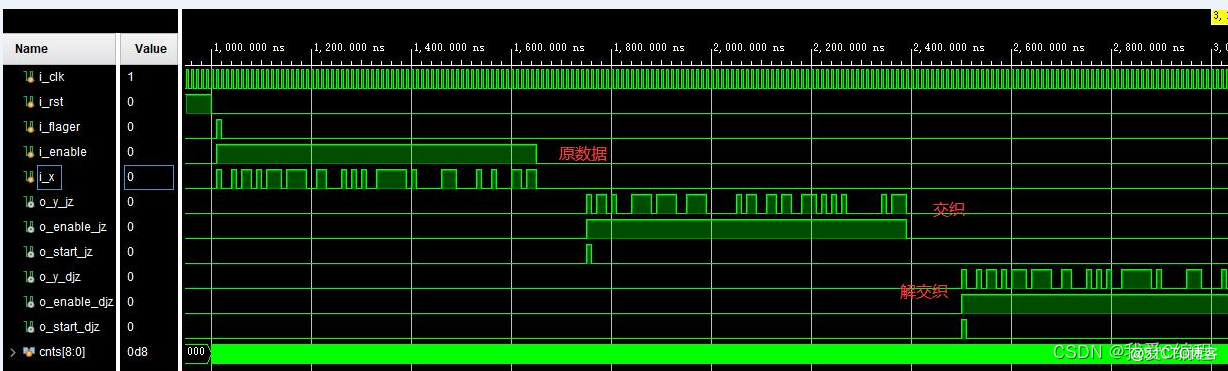

1.算法仿真效果

其中Vivado2019.2仿真结果如下:

2.算法涉及理论知识概要

交织解交织系统是一种数据传输技术,广泛应用于通信系统中,以提高数据传输的可靠性和抗干扰能力。该系统通过将数据在发送端进行交织处理,然后在接收端进行解交织处理,使数据的各个位分散到不同的位置上,从而降低信道噪声和干扰的影响,提高数据传输的可靠性。

具体来说,交织解交织系统的工作流程如下:

交织:将发送端的数据按照一定的规则进行交织处理,将数据的各个位分散到不同的位置上。

编码:将交织后的数据进行编码,以提高数据传输的可靠性。常见的编码方式包括卷积码、纠正码等。

调制:将编码后的数据进行调制,以适应信道传输的特性。常见的调制方式包括ASK、FSK、PSK等。

传输:将调制后的数据通过信道传输到接收端。

解调:在接收端对传输的信号进行解调,得到接收端的数字信号。

解码:将接收端的数字信号进行解码,以恢复原始数据。解码过程需要考虑信道噪声和干扰的影响。

解交织:将解码后的数据按照与交织规则相反的规则进行解交织处理,恢复原始数据的顺序。

以上就是交织解交织系统的基本原理。下面我们将介绍如何在FPGA中实现交织解交织系统。

FPGA实现交织解交织系统的一般步骤如下:

设计交织规则:交织规则是交织处理的核心,它决定了数据的交织顺序和交织方式。在实际应用中,需要根据具体情况设计合适的交织规则。

设计交织模块:交织模块是整个交织解交织系统的核心,它实现了交织规则。交织模块通常包括一个缓存区和一个交织器。缓存区用于存储输入数据,交织器用于实现交织规则。

设计解交织模块:解交织模块与交织模块相似,但是它需要实现与交织规则相反的规则,以恢复原始数据的顺序。

设计编码模块:编码模块用于将交织后的数据进行编码,以提高数据传输的可靠性。常见的编码方式包括卷积码、纠正码等。

设计调制模块:调制模块用于将编码后的数据进行调制,以适应信道传输的特性。常见的调制方式包括ASK、FSK、PSK等。

设计解调模块:解调模块用于在接收端对传输的信号进行解调,得到接收端的数字信号。

设计解码模块:解码模块用于将接收端的数字信号进行解码,以恢复原始数据。解码过程需要考虑信道噪声和干扰的影响。

设计解交织模块:解交织模块用于将解码后的数据按照与交织规则相反的规则进行解交织处理,恢复原始数据的顺序。

设计控制模块:控制模块用于控制整个交织解交织系统的工作流程,包括数据输入输出、模块的启停等。

以上就是在FPGA中实现交织解交织系统的一般步骤。在实际应用中,需要根据具体情况进行调整和优化。

交织解交织系统是一种数据传输技术,可以提高数据传输的可靠性和抗干扰能力。在FPGA中实现交织解交织系统需要设计交织规则、交织模块、解交织模块、编码模块、调制模块、解调模块、解码模块、解交织模块和控制模块等模块。FPGA具有可编程性和高并行性等优势,在实现交织解交织系统时具有一定的优势。在实际应用中,需要根据具体情况进行调整和优化。

本课题,我们主要开发单独的交织和解交织模块。

3.Verilog核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/05/12 19:58:30

// Design Name:

// Module Name: tops

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tops(

input i_clk,

input i_rst,

input [2:0]i_sel,//配置2*2交织和4*4交织

input i_flager,

input i_enable,

input i_x,

output o_y_jz,

output o_enable_jz,

output o_start_jz,

output o_y_djz,

output o_enable_djz,

output o_start_djz

);

//交织

jiaozhi jiaozhi_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_sel (i_sel),//配置2*2交织和4*4交织

.i_flager (i_flager),

.i_enable (i_enable),

.i_x (i_x),

.o_y (o_y_jz),

.o_enable_jz (o_enable_jz),

.o_start_jz (o_start_jz)

);

//解交织

dejiaozhi dejiaozhi_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_sel (i_sel),//配置2*2交织和4*4交织

.i_flager (o_start_jz),

.i_enable (o_enable_jz),

.i_x (o_y_jz),

.o_y (o_y_djz),

.o_enable_jz (o_enable_djz),

.o_start_jz (o_start_djz)

);

endmodule