光通信 章节fpga 07

模拟器在物联网通信中的应用:实现设备之间的通信和数据交换

[toc] 物联网技术的发展,使得各种设备之间的通信和数据交换变得更加方便和实时。模拟器在物联网通信中的应用,则是实现设备之间的通信和数据交换的有效手段之一。本文将介绍模拟器在物联网通信中的应用,以及实现这种应用的基本步骤和流程。 ## 1. 引言 随着物联网技术的不断发展,越来越多的设备和传感器被 ......

2023.6.15 07.数据库存储过程

07.数据库存储过程 存储过程 MySQL 存储过程是⼀组 预编译的 SQL 语句 ,可以在 MySQL 数据库中 定义和存储 ,并在 需要时执⾏ 。存储过程可 以接受参数、执⾏条件判断、循环、异常处理等操作,使得开发⼈员可以把⼀系列操作组合成⼀个可重复使⽤的单 元,从⽽提⾼代码的复⽤性和可维护性。 ......

https通信的整理

通信流程 1.客户端使用https的url访问web服务器,要求与web服务器建立ssl连接。 2.web服务器收到客户端请求后,会将网站的证书信息(证书中包含公钥)传送一份给客户端。 3.客户端浏览器与web服务器协商ssl连接的安全等级,即信息加密的等级。 4.客户端浏览器根据安全等级,建立会话 ......

Vue 中 组件通信 - 子传父(自定义事件)

# Vue 中 组件通信 - 子传父(自定义事件) ``` Vue 中 组件通信 - 子传父(自定义事件)子传父步骤:在子组件的 data 里面定义好 要传递的数据在子组件的模版里面正常使用 该数据(一般是通过一定的动作,如点击,滑动等,来自定义事件向父组件传递,这里以 click 为例)在子组件的 ......

web网络通信

## WEB通信流程 静态数据:png,css,js,gif,mp4 动态数据:从mysql数据库中读取出来的数据 1. 访问DNS服务器,通过DNS获取相应的域名对应IP 2. 通过IP对应服务器后,简历TCP连接 3. 等浏览器发送完HTTP Request包后,服务器接收到请求包后才开始处理请 ......

微信小程序如何使用原生Websocket与Asp.Net Core SignalR 通信

# 背景 如题,这可能算是.net 做小程序的服务端时,绕不开的一个问题,老生常谈了。同样的问题,我记得我2018/19年的一个项目的解决方案是: **修改官方的SignalR.js的客户端**:把里面用到浏览器的Websocket改成微信小程序的官方api的。目前网上也有不少这样的方案,已经改好开 ......

进程间通信

### 进程间通信 - 每个进程的用户空间都是独立的,一般不能相互访问,但是又有许多情况需要进程间进行相互通信来完成系统的某项功能。进程间通信依靠内核空间来完成 - 进程间通信的方法主要有: - 管道 - 信号量 - 消息队列 - 信号 - 共享内存 - 套接字 #### 管道 - 半双工、只能用于 ......

企业即时通信软件有哪些?要如何选择?

随着企业数字化转型的加速,即时通信软件已成为企业日常沟通的重要工具。但是市面上的企业即时通信软件种类繁多,如何选择适合自己企业的即时通信软件呢?本文将为大家介绍几款常用的企业即时通信软件以及如何选择。 企业微信 企业微信是腾讯公司推出的一款专为企业打造的即时通信软件,为企业提供了办公、沟通、协同、服 ......

vue实现子父组件之间通信

<template> <div> <button @click="handleClick" :disabled="isLoading"> {{ isLoading ? "loading" : "submit" }} </button> <div class="err">{{ error }}</di ......

代码随想录day07

第三章 哈希表part02 454.四数相加II 383. 赎金信 15. 三数之和 18. 四数之和 454.四数相加II 思路:采用分为两组,HashMap 存一组,另一组和 HashMap 进行比对。 首先求出 A 和 B 任意两数之和 sumAB,以 sumAB 为 key,sumAB 出现 ......

m基于FPGA的CRC循环冗余校验系统verilog实现,包含testbench

1.算法仿真效果 本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: Quartusii18.0+ModelSim-Altera 6.6d S ......

m基于FPGA的AGC自适应增益控制系统verilog实现,包含testbench

1.算法仿真效果 Vivado2019.2仿真结果如下: 放大后可以看到: 2.算法涉及理论知识概要 数字AGC(Automatic Gain Control)是一种广泛应用于通信系统中的自动增益控制技术。它可以自动调节接收信号的增益,以使信号的强度保持在适当的范围内,从而保证接收到的信号质量。 数 ......

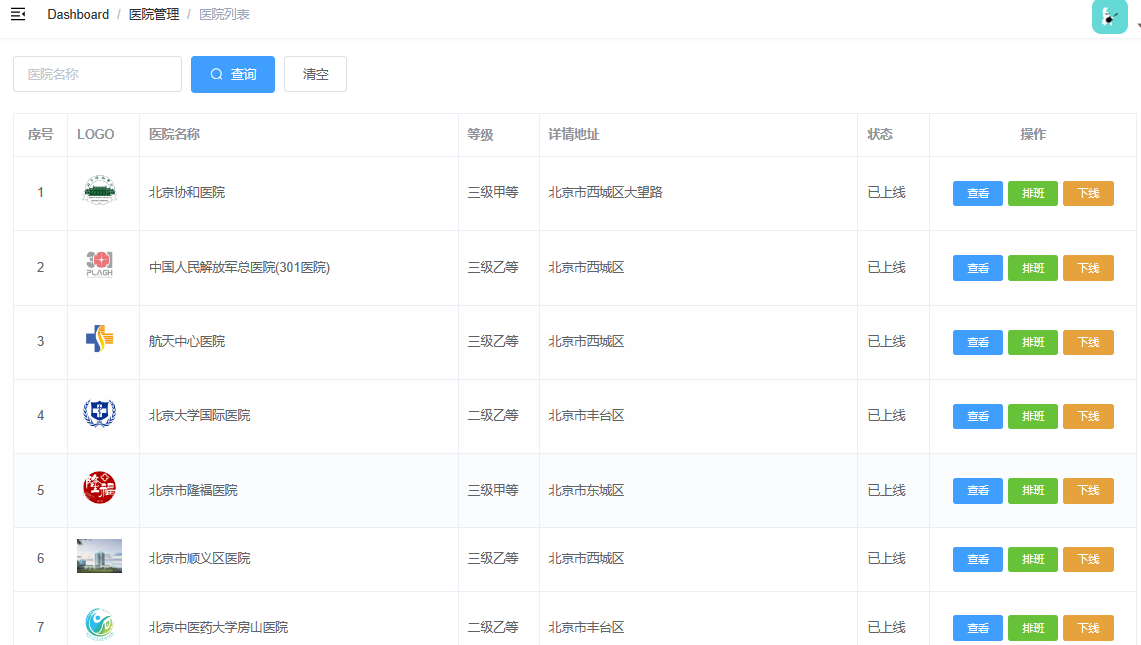

尚医通-day07【医院管理详细步骤】(内附源码)

# 页面预览 ## 列表页  ## 批量导入数据 为了方便测试,我们可以将更多的医院信息数据批量导入到系统中。将资料中的json数据和测试用例复 ......

js 0.07*100竟然是7.000000000000001

无意中发现了一个问题:0.07*100=7.000000000000001,而不是7。 结果为什么是7.0000000000000001? 其实JavsScript中,变量在存储时并不区分number和float类型,而是统一按float存储。而javascript使用IEEE 754-2008 标 ......

第四届计算机科学与通信技术国际学术会议(ICCSCT 2023)

第四届计算机科学与通信技术国际学术会议(ICCSCT 2023)将于2023年7月26-28日在中国武汉召开。会议旨在为计算机科学和通信技术领域的各专家学者,研究员,从业人员以及老师学生等科研人士提供一个学术交流的平台和机会。热忱欢迎计算机科学和通信技术专家学者踊跃投稿参会~ ★重要信息 大会时间: ......

m基于FPGA的基础OFDM调制解调verilog实现,包括IFFT和FFT,包含testbench

1.算法仿真效果 其中Vivado2019.2仿真结果如下 2.算法涉及理论知识概要 正交频分复用(Orthogonal Frequency Division Multiplexing, OFDM)是一种多载波调制技术,其基本原理是将高速数据信号分成多个低速子载波,在每个子载波上调制数据,将所有子载 ......

m基于FPGA的16QAM调制解调通信系统verilog实现,包含testbench,不包含载波同步

1.算法仿真效果 本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: Quartusii18.0+ModelSim-Altera 6.6d S ......

Kafka通信模型/流程

Kafka的Producer、Broker和Consumer之间采用的是一套自行设计的基于TCP层的协议 由于UDP协议是一种不可靠的传输协议,所以Kafka系统采用TCP协议作为服务间的通信协议 通信 通信模型 Reactor线程模型 Java NIO中的selector模型。最简单的Reacto ......

0x07 进制

对于整数,有四种表示方式 1. 二进制:0,1,满2进1 在 Go 语言中,不能直接使用二进制来表示一个整数,它沿用了 C 语言的特点。 2. 十进制:0-9,满10进1 3. 八进制:0-7,满8进1,以数字0开头表示 4. 十六进制:0-9及A-F,满16进1,以 `0x` 或 `0X` 开头表 ......

java串口通信

###实体 ```java package com.hwd.campus.common.common.utils.http; import gnu.io.SerialPort; /** * 串口参数封装类 * @author Administrator * */ public class Seria ......

[Qt开发]一口气搞懂串口通信

🐊🐊🐊🐊🐊好多小鳄鱼 # 一、关于串口通信: Qt的确有自己的串口通信类,就是QSerialPort,但是我们在使用过程中因为要更加定制化的使用串口通信类减小开发的难度,所以我们会提供一个串口通信类,也就是这个SerialPortHelper类。 首先我们要知道什么是串口,串口通信就是机器 ......

Xilinx GTH 简介 ,CoaXpress FPGA PHY 部分

## 什么是GTH GTH 是Xilinx UltraScale系列FPGA上高速收发器的一种类型,本质上和其它名称如GTP, GTX等只是器件类型不同、速率有差异;GTH 最低速率在500Mbps,最高在16Gbps ![](https://img2023.cnblogs.com/blog/274 ......

[TSG开发日志2]串口通信?VS下FaroSDK编译环境?一文搞定

艹,不知道为什么我之前写的法如sdk没有保存,总而言之就是莫名其妙整个工程没有了,后来我想了想,也有可能就是我自己删掉了,因为在配置法如工程的时候遇到了一些小问题,不过现在也解决了。 # 一、关于串口通信: Qt的确有自己的串口通信类,就是QSerialPort,但是我们在使用过程中因为要更加定制化 ......

m基于FPGA的通信数据帧加扰解扰verilog实现,包含testbench

1.算法仿真效果 本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: Quartusii18.0+ModelSim-Altera 6.6d S ......

m基于FPGA的QPSK调制解调通信系统verilog实现,包含testbench,不包含载波同步

1.算法仿真效果 本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: Quartusii18.0+ModelSim-Altera 6.6d S ......

透过 Go 语言探索 Linux 网络通信的本质

## 前言 各种编程语言百花齐放、百家争鸣,但是 “万变不离其中”。对于网络通信而言,每一种编程语言的实现方式都不一样;但其实,调用的底层逻辑都是一样的。linux 系统底层向上提供了统一的 Socket 通信系统函数,动态链接库 `/lib64/libc.so` 中就是实现网络通信的关键类库。下面 ......

第四天打卡|24. 两两交换链表中的节点 ● 19.删除链表的倒数第N个节点 面试题 02.07. 链表相交 142.环形链表II

24. 两两交换链表中的节点 :简单的交换 19.删除链表的倒数第N个节点: ● 面试题 02.07. 链表相交 :这题没看过答案真的写不出来。太巧妙了 142.环形链表II : 这题写过但是忘记怎么解的了还是看的答案。下次不能忘记 ......

代码随想录算法训练营第四天|24. 两两交换链表中的节点 , 19.删除链表的倒数第N个节点 , 面试题 02.07. 链表相交 , 142.环形链表II

24. 两两交换链表中的节点 个人感觉这个不太难,刚开始打算用步进值为2,来搞,但是没有想到链表应该是怎么样的,原来可以直接用: 1 cur = cur->next->next 学到了,这是我自己写的代码: 1 ListNode* MyLinkedList::swapPairs(ListNode* ......

m基于FPGA的BPSK调制解调通信系统verilog实现,包含testbench,包含载波同步

1.算法仿真效果 vivado2019.2仿真结果如下: 对比没载波同步和有载波同步的仿真效果,我们可以看到,当不存在载波同步时,数据的包络会有一个缓慢的类正弦变换,这是由于存在频偏导致的。而当加入载波同步之后,数据的包络会存在少量起伏,但数据反转的情况已经没有了, 说明频偏得到了补偿。 2.算法涉 ......