简易verilog fifo

Flask + SocketIO实现简易实时在线聊天室

下面是一个简单的示例,演示了使用 Python(使用 Flask 框架)作为服务端,以及 HTML、JavaScript 和 Socket.io 作为前端,实现一个简单的实时聊天室。 首先,确保你已经安装了 Flask 和 Flask-SocketIO: pip install Flask Flas ......

SQL注入攻击的原理以及如何防止SQL注入(简易)

🍟SQL注入攻击的原理 SQL 注入(SQL Injection)是发生在 Web 程序中数据库层的安全漏洞,是网站存在最多也是最简单的漏洞。主要原因是程序对用户输入数据的合法性没有判断和处理,导致攻击者可以在 Web 应用程序中事先定义好的 SQL 语句中添加额外的 SQL 语句,在管理员不知情 ......

verilog学习笔记1

第一课的学习任务是: ①搞清楚常用语法,重点是赋值方式这部分,对应实际电路和实现的思路 ②能够写出ppt里的简单程序 ③会使用modelsim软件、编写testbench,验证自己的代码 一、数据流建模 1、连续赋值语句 格式是assign a = xxx;被赋值的变量必须是wire类型 语句定义了 ......

进程间通信-信号-pipe-fifo

进程间通信-信号-pipe-fifo 编译fifo文件夹的程序 运行fifo文件夹的程序 代码说明 1.consumer.c 文件包含一个用来从 FIFO(命名管道)读取数据的 C 程序。以下是它的主要组件和系统调用的分解: main() 函数: 初始化文件描述符(pipe_fd)、返回状态(res ......

Golang实现简易的顺序执行协程池

countable_executor.go // 一个可计数的单线程顺序任务执行器 type CountableExecutor struct { name string // 名称 taskQueue chan iCountableTask // 任务队列 bufferSize int // 缓冲 ......

verilog设计行为仿真和时序仿真不一致, 原来是敏感信号的问题

描述 最近在vivado中设计一个计算器: 28bit有符号加减法,结果出现行为仿真和时序仿真不一致情况 代码 r_a, r_b : 对计算数据a, b的寄存器存储, 也是计算器的数据输入 s_bit : 符号位 cout : 28bit计算器的进位输出 cout[27] : 最高位进位, 用来判断 ......

上机编程-简易DHCP服务器

题目描述 DHCP服务器的功能是为每一个MAC地址分配唯一的IP地址。现假设:分配的IP地址范围从 192.168.0.0 到 192.168.0.255 总共256个可用地址(以点分十进制表示)。请实现一个简易的DHCP服务器,功能如下: 分配Request:根据输入的MAC地址分配IP地址池中的 ......

第7天 FIFO与鼠标控制

获取按键编码 当中断程序处理完毕之后需要相8259A发送一个处理完毕的信号,这样8259A才知道中断已经处理完毕,可以接收下一个中断信号了,不然的话,我们的键盘中断一直阻塞在哪里没办法进行处理下一个按键操作。 io_out8(PIC0_OCW2, 0x61);就是为了满足这个操作的。键盘的中断是IR ......

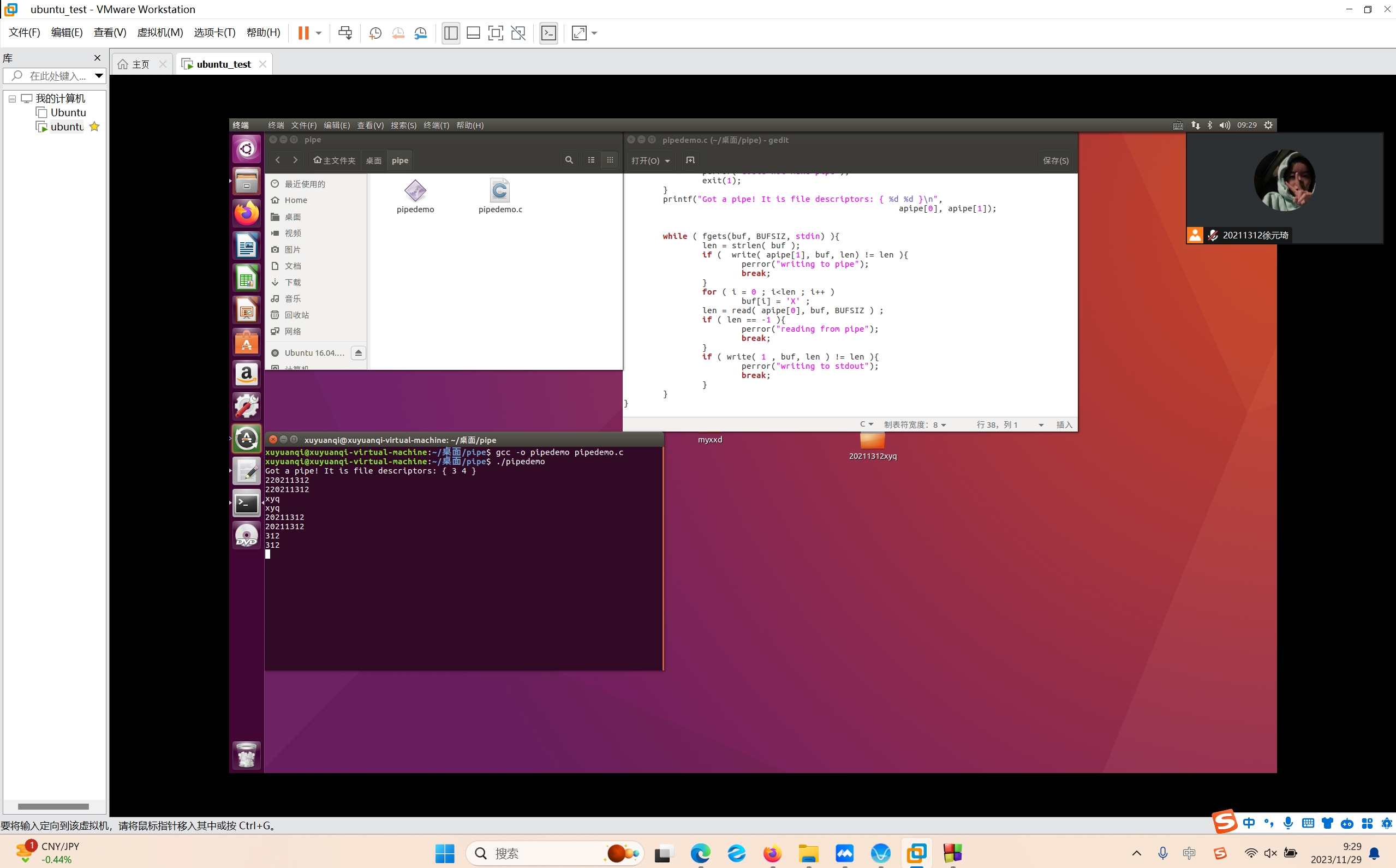

进程间通信-信号-pipe-fifo

编译运行 Fifo Consumer Producer 一起运行 Testmf pipe文件夹 Pipe Listarg 理解 ()Pipe 概念: 管道是一种在两个进程之间进行通信的机制。个进程的输出可以通过管道传递给另一个进程的输入创建: 在C语言中,可以使用pipe系统调用创建管道。管道有两端 ......

一个简易的vim下c语言开发环境配置 vimrc很短

vimrc修改的部分短到可以随口背下来 没有一些复杂的提示或者自动补全,只有基本的自动补全和换行操作,用来写一些玩具一样的小程序足够了。比较适合用来在OJ上刷题用。 vim &g++ & gdb,就能解决非常多的问题了,整个流程都可以在terminal下完成,不失为一种高效的方法。 ......

进程间通信-信号-pipe-fifo(课上测试)

一.运行结果 二.代码说明 consumer.c 该程序是一个使用FIFO(命名管道)进行进程间通信的示例。首先定义了FIFO的名称和缓冲区的大小。然后在主函数中,打开了一个以只读方式打开的FIFO,并读取FIFO中的数据直到读取完毕,最后关闭FIFO。 相关系统调用说明:1. open:打开FIF ......

基于Redis的简易延时队列

基于Redis的简易延时队列 一、背景 在实际的业务场景中,经常会遇到需要延时处理的业务,比如订单超时未支付,需要取消订单,或者是用户注册后,需要在一段时间内激活账号,否则账号失效等等。这些业务场景都可以通过延时队列来实现。 最近在实际业务当中就遇到了这样的一个场景,需要实现一个延时队列,用来处理订 ......

scrapy框架之自定义简易scrapy框架

自定义low版Scrapy框架: 1 from twisted.internet import reactor #事件循环(终止条件,所有的socket都已经移除) 2 from twisted.web.client import getPage #socket对象(如果下载完成..自动从事件循环中 ......

C#读取SQL数据库,并将读取的数据上传至服务简易Demo

1.使用的NuGet包 2.IRepository 接口 { IEnumerable<Package> GetAllPackages(); void DeleteByCodePackages(string code); // void InitRepository(); } 3.SimpleRepo ......

m基于FPGA的OFDM系统verilog实现,包括IFFT,FFT,成型滤波以及加CP去CP,包含testbench

1.算法仿真效果 vivado2019.2仿真结果如下: CP加入,删除效果: 系统RTL结构图: 2.算法涉及理论知识概要 正交频分复用(Orthogonal Frequency Division Multiplexing,OFDM)是一种高效的无线通信技术,已经被广泛应用于无线通信领域。OFDM ......

m基于FPGA的8PSK调制解调系统verilog实现,包含testbench测试文件

1.算法仿真效果 vivado仿真结果如下: 借助matlab看8PSK的星座图: 2.算法涉及理论知识概要 随着通信技术的不断发展,相位调制技术因其高频谱效率和抗干扰能力而广泛应用于无线通信系统中。其中,8PSK(8相位相移键控)作为一种高阶调制方式,具有更高的频谱效率和更强的抗干扰能力,因此备受 ......

简易计算机的搭建

简易计算机的搭建 1、一些无关紧要的前置知识 现代计算机类设备的主流架构一般有两种:一为冯诺依曼体系架构;一为哈弗架构。 主流计算机采用的架构一般为冯诺依曼体系,是将程序和数据放在一起存储的架构; 单片机设备一般采用哈弗架构,是将程序与数据分开存储的一种架构。 以下基本都是有关冯诺依 ......

第二次作业——基于SpringBoot框架开发的包含登录界面的简易计算器

一.设计思路: 1.简要说明: 本次作业是基于SpringBoot框架开发的, 使用SpringBoot框架有很多好处,比如SpringBoot简化了原始Spring框架的使用,它本身内嵌了tomcat容器。 对于计算器部分,新做了纯前端(html,js)实现的一个能实现单括号混合运算的计算器,没有 ......

编写简易scanner计算器

要求: 具有加、减、乘、除功能 能够循环接收新的数据 通过用户交互实现(Scanner) 思路推荐: 写4个方法:加、减、乘、除 利用循环+switch进行用户交互 传递需要操作的两个数 输出结果 疑问: 要求不太明确,“循环接收新数据”是指要求“能重复进行两个数的四则运算”,还是“实现连续四则运算 ......

Verilog实现Mips五级流水CPU

MIPS 项目仓库请见https://github.com/ZhangFirst1/MIPS 使用Verilog实现的Mips CPU,实现了简易的五级流水。项目使用Vivado构建。 实现了ori、or、and、xor、sll、jal、beq、sw、lw、subu、addu指令。解决了流水线数据相 ......

消息传递:管道和FIFO

一、简介 管道是没有名字的,管道创建的资源由内核管理,单个程序中不同进程通过管道描述符fd进行通信,对于程序和程序之间是无法通信的。 FIFO是有名字的(也称为 有名管道),每一个FIFO都有一个文件与之关联,但仅限于同一主机程序与程序之间通信,无法通过在NFS上创建FIFO通信。 二、管道 所有管 ......

环形缓冲区FIFO

最近学习一个LwRB开源环形缓冲区FIFO设计,即先入先出缓冲区。LwRB 是一个开源、通用环形缓冲区库。 1、只有单个任务写和单个任务读时,线程是安全的 2、只有单个中断写和单个中断读时,中断是安全的 3、支持内存间的 DMA 操作,实现缓冲区和应用程序内存之间零拷贝 4、对于读数据,提供 pee ......

基于百度云API的简易机器翻译

import okhttp3.*;import org.json.JSONArray;import org.json.JSONObject; import javax.swing.*;import java.awt.*;import java.awt.event.ActionEvent;import ......

进程间通信-信号-pipe-fifo(

与饱和(saturation)截位

转自 https://blog.csdn.net/yan1111112/article/details/118498533 重点: 1、正数截位:直接看截掉的最高位是不是一,是的话进一。 负数截位:截的最高位为1且其它位不全是0进一 2、饱和,也就是大于求的结果,整数变为符号位为0,其它位为1;负数 ......

verilog实现 floor, round 四舍五入 和 saturation 操作

floor, round和saturation是进行bit位削减时常用的方法,floor 和round用于削减低位,saturation用于削减高位。floor和round的区别在于,floor是将低位直接丢掉,而round则是在丢掉低位前先进行四舍五入。round和saturation的使用范例如 ......

实现一个简易的golang版本的CompletetableFuture

背景 将入侵4.0 java代码迁移到入侵5.0 golang项目时,有些并行处理的功能用到了java的CompletetableFuture框架,但是golang中好像没有类似的框架(可能我没有找到),所以打算手动写一个简易的golang版本的CompletetableFuture。 在入侵jav ......