*本文为明德扬原创文章,转载请注明出处!作者:Vito*

第二周的试用计划是实现常见低速协议(UART,I2C,SPI)的FPGA工程,记录自己实现的过程,包括协议基本理解,实现思路,仿真调试,上板验证4个流程。虽然低速协议相对简单,但是每次自己动手写又会发现之前没有注意到的问题,又能从中巩固自己的逻辑思维;这些看似简单的低速协议是后续所有高速接口协议的基础,只有基础牢靠,在后续的进阶应用中才会游刃有余。特别是对于我这样的FPGA新人来说,基础是重中之重。

下面开始介绍我的低速协议的实现情况。

协议理解

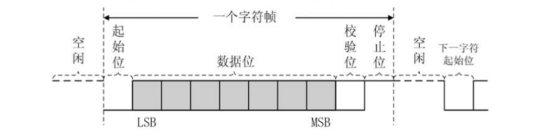

UART真的算是最经典的通信协议之一了吧,特别是在产品设计调试阶段,串口几乎成了一个必备的功能。硬件信号简单,2根信号线(TX,RX),当然不同设备连接时还需要一根共地线;3根线就能实现数据传输了。协议数据格式如下图所示

数据收发过程分为:空闲,起始位,数据位,校验位(可选),停止位。对于异步的设备来说,怎样知道每一位传输的时间宽度呢?这是通过波特率来指定的。事先双方先约定好传输的波特率是多少就可以了,当然除了波特率,一般数据位长度,奇偶校验,停止位长度都是要2方确定好,不然就无法正确通信了。

实现思路

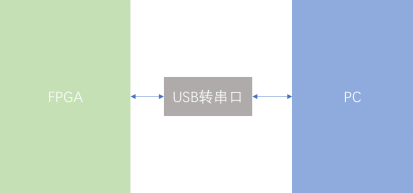

本次实现FPGA和上位机通信的串口工程,连接如下图所示;具体功能是利用PC的串口工具向usb转串口模块发送随机数据,FPGA通过接收usb转串口模块的数据并进行解析,并将解析的串口数据发回usb转串口;通过查看PC上的接收数据和发送数据是否一致。

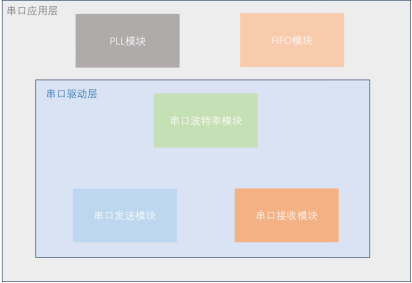

根据上述功能需求,进行模块划分设计,如下图所示

根据模块划分,下面就需要明确模块的接口信号,这里为了举例就只列出tx和rx的接口信息。这里总结一下接口信号的思路:时钟复位以及tx/rx信号就不说了,这里还加了握手信号,增加每一帧数据收发的可靠性,在处理一帧数据时不会被下一帧数据到来中断而导致混乱。

信号接口设计完成之后就是每个模块代码的编写了,这里我就简单总结一下tx和rx设计思路。对于发送模块:握手逻辑如果收到应用层一帧数据的有效信号,拉低ready信号,同时拉高发送数据的标志位。当发送标志位置1,发送计数器开始计数一帧数据的个数,直到一帧数据的周期数记完并清零,表示一帧数据发送完成;于此同时,tx信号根据发送计数器值依次将应用层的并行数据移位送出。对于接收模块:当检测到rx信号的下降沿之后,接收计数器开始计数,计数值为一帧数据的周期长度;并根据计数值移位采样rx数据,转化成并行数据,并拉高valid有效信号,表示一帧数据的接收过程。

仿真调试

编写完串口驱动模块之后,需要进行仿真调试,下面是仿真波形。

仿真激励中,发送数据给的是1,2,3……255 数据,可以看到图中紫色部分为收发数据的波形,可以看到收发数据一致,因此仿真调试ok。

上板验证

在实际应用中,需要考虑更多的非理想环境。1.罪魁祸首就是异步时钟问题,运行时间越长,所累积的时钟误差就会越来越大;所以很可能运行一段时间就会出现错误数据,因此需要加上时钟矫正减少时钟累积误差,解决办法就是用高频时钟采集rx信号,当检测到一次数传输时再打开串口接收时钟,当发送完成之后再将串口接收时钟关闭从而解决累积偏差。2.收发数据时有时一帧数据还没有处理完成,可是下一帧数据已经到来,如果不缓存就会出现丢帧的问题,因此在应用层增加了一个fifo,用于缓存来不及处理的数据。

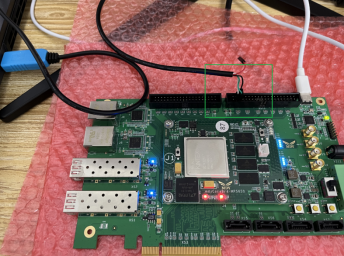

我之前看原理图底板上是有FT232usb转串行的芯片的,但是好像只连接了JTAG接口,电脑并没有识别到串口号,所以我只能在扩展口找2个IO了。翻遍了原理图和手册都没有找到一个XS11的引脚对应关系,没办法只能先通过原理图猜测信号所对应的实际引脚位置,好在我手边有万用表,然后通过测量知道了实际对应位置,希望之后将一些接口的实际信号做一个图示,自己找信号位置太麻烦了。。。这里我挑了2个IO:J23/J24作为uart的tx 和 rx,连接一个usb转串口模块,然后连接电脑,实际连接如下图所示。

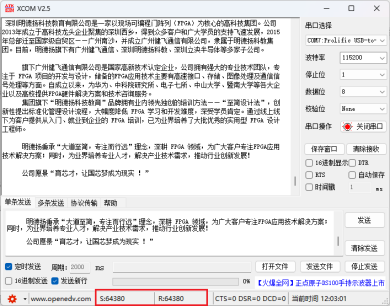

下载bitstream之后,打开电脑串口软件,定时一直发送数据,观察收发数据是否一致,测试结果如下图所示。

可以看到,经过一段时间的连续运行,收发数据量一致,且结果正确。因此该串口工程上板成功。

众所周知,XILINX-Kin[te]x系列以性价比著称,在高性能低功耗的前提下,价格也相对较低,目前市场上不存在缺货的情况,所以当使用量大的时候,价格也会更有优势。所以在研发工作中,

这个款核心板是非常适用于二次开发和产品使用的。明德扬推出0元试用核心板活动正在进行中,了解详情