VCS和Verdi联合仿真小实验

基础准备

环境安装略过

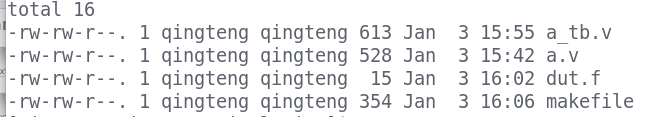

新建一个文件夹,文件夹下一共需要四个文件,分别是头文件命名为 a.v、仿真文件命名为 a_tb.v、文件名的list文件命名为 dut.f、还有makefile文件

头文件

首先是头文件 a.v

module a(

clk ,

rst_n ,

dout

);

parameter DATA_W = 8;

input clk ;

input rst_n ;

output[DATA_W-1:0] dout ;

wire add_cnt;

wire end_cnt;

reg [5:0] cnt;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt <= 0;

end

else if(add_cnt)begin

if(end_cnt)

cnt <= 0;

else

cnt <= cnt + 1;

end

end

assign add_cnt = 1;

assign end_cnt = add_cnt && cnt== 8;

assign dout = cnt;

endmodule

仿真文件

然后是仿真文件 a_tb.v 其中需要插入生成fsbd波形的函数 并设置相应的仿真结束条件

`ifdef DUMP_FSDB

initial begin

#100000;

$finish;

end

initial begin

$fsdbDumpfile("tb.fsdb");

$fsdbDumpvars("+all");

end

`endif

具体代码如下:

`timescale 1 ns/1 ns

module test();

reg clk ;

reg rst_n;

wire dout0;

wire[7:0] dout1;

parameter CYCLE = 20;

parameter RST_TIME = 3 ;

a uut(

.clk (clk ),

.rst_n (rst_n ),

.dout (dout1 )

);

initial begin

clk = 0;

forever

#(CYCLE/2)

clk=~clk;

end

initial begin

rst_n = 1;

#2;

rst_n = 0;

#(CYCLE*RST_TIME);

rst_n = 1;

end

`ifdef DUMP_FSDB

initial begin

#100000;

$finish;

end

initial begin

$fsdbDumpfile("tb.fsdb");

$fsdbDumpvars("+all");

end

`endif

endmodule

list 文件

文件名为 dut.f 其中包含所有的头文件和仿真文件

./a.v

./a_tb.v

makefile

makefile文件作用是自动化编译,使用相关脚本

#!/bin/make

all: comp sim

comp:

vcs -full64 -timescale=1ns/1ps -V -R -sverilog -debug_access+all +vc +v2k -kdb -l vcs.log -f dut.f +define+DUMP_FSDB=1 -top test

sim:

./simv -l simv.log

show:

verdi -ssf tb.fsdb &

clean:

rm -rf *~ core csrc simv* vc_hdrs.h ucli.key urg* *.log novas.* *.fsdb* verdiLog 64* DVEfiles *.vpd verdi_config_file

效果演示

文件列表图

编译后的效果图

通过make all 使用vcs编译文件

查看波形

通过make show打开verdi

生成波形通过ctrl+w将其添加到下面看波形