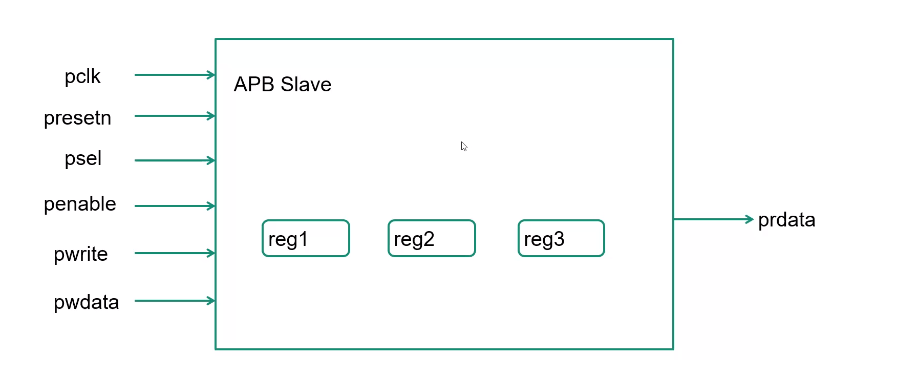

APB Slave Design

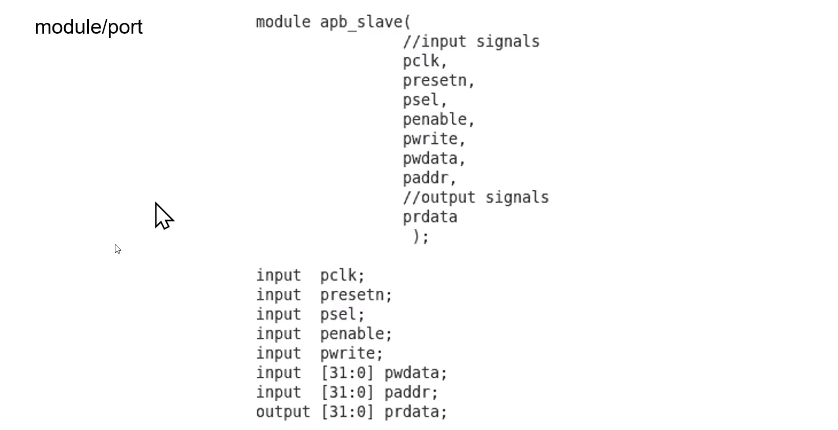

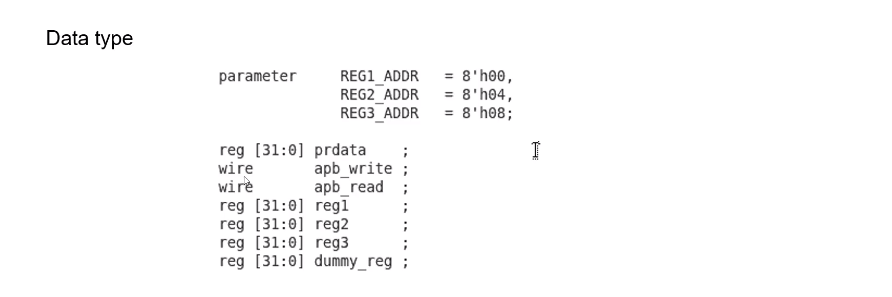

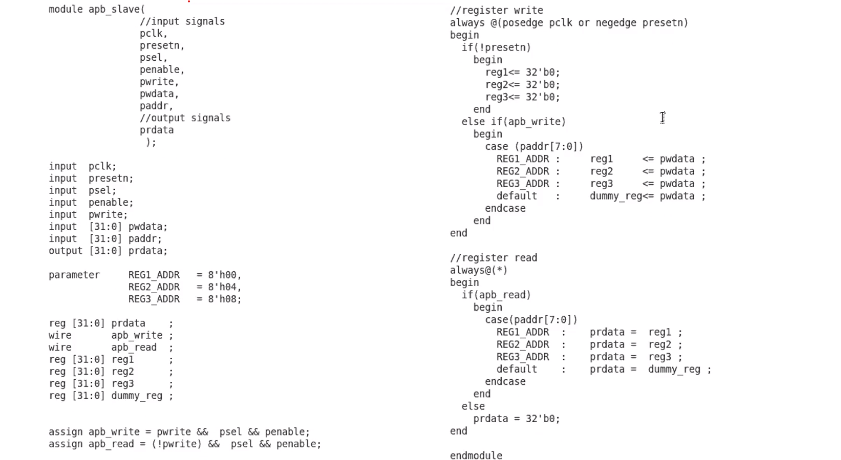

module apb_slave

#(

REG1_ADDR = 8'h00,

REG2_ADDR = 8'h04,

REG3_ADDR = 8'h08

)

(

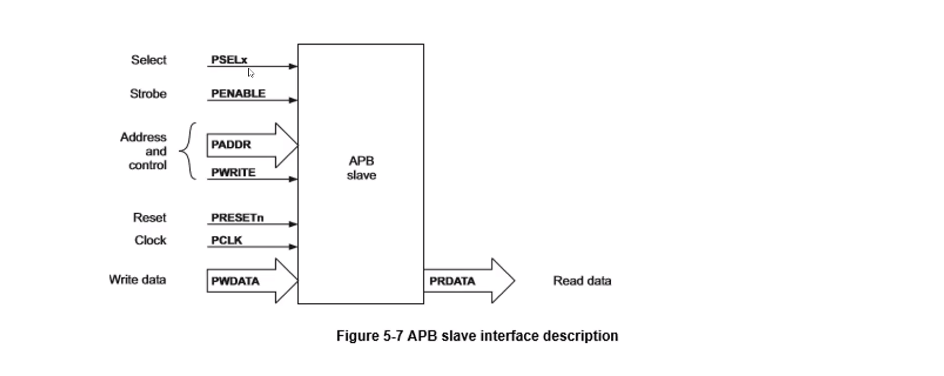

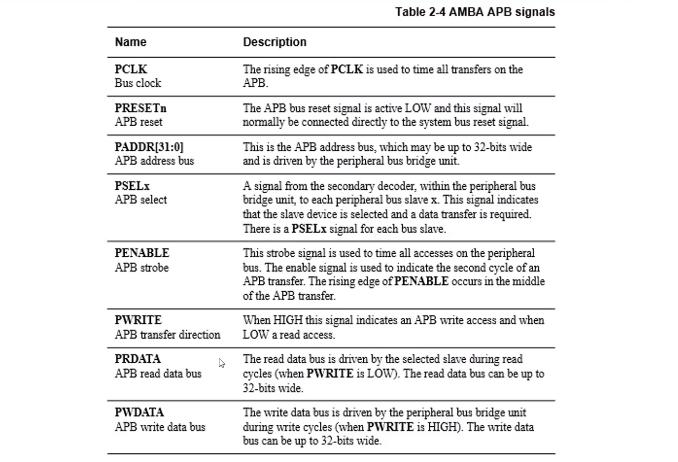

// input signals

input pclk,

input presetn,

input psel,

input penable,

input pwrite,

input [31:0] pwdata,

input [31:0] paddr,

output reg [31:0] prdata,

);

// 读写信号

wire apb_write;

wire apb_read;

// 定义三个寄存器

reg [31:0] reg1;

reg [31:0] reg2;

reg [31:0] reg3;

reg [31:0] dummy_reg;

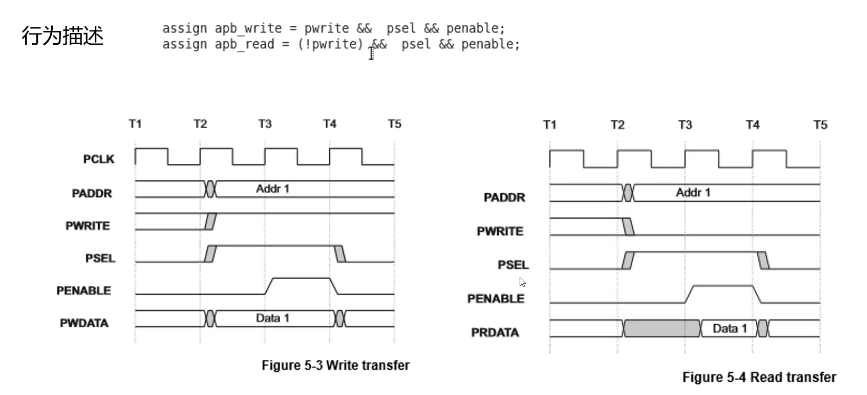

// 产生读写信号

assign apb_write = pwrite && psel && penable;

assign apb_read = (!pwrite) && psel && penable;

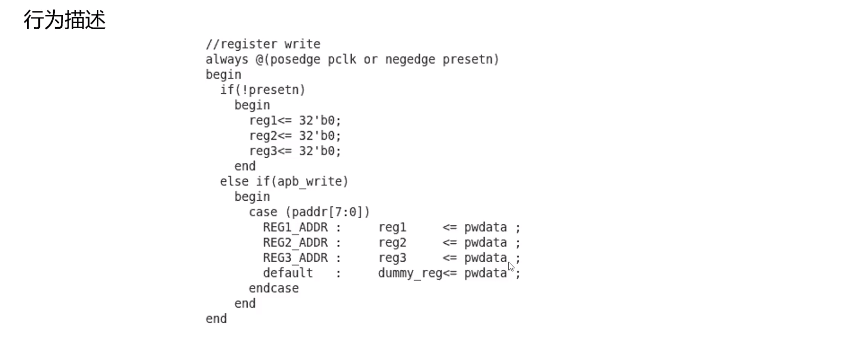

// 写操作

always @ (posedge pclk or negedge presetn) begin

if(!presetn)

begin

reg1 <= 32'b0;

reg2 <= 32'b0;

reg3 <= 32'b0;

end

else if(ahb_write)

begin

case (paddr[7:0])

REG1_ADDR:reg1 <= pwdata;

REG2_ADDR:reg2 <= pwdata;

REG3_ADDR:reg3 <= pwdata;

default:dummy_reg <= pwdata;

endcase

end

end

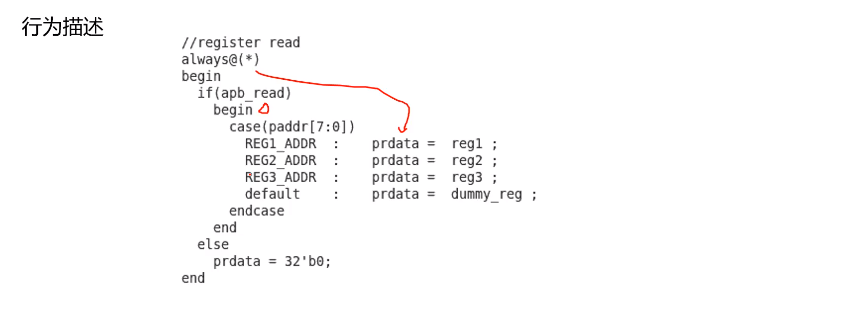

always @ (posedge pclk or negedge presetn) begin

if(ahb_read)

begin

case (paddr[7:0])

REG1_ADDR:prdata <= reg1;

REG2_ADDR:prdata <= reg2;

REG3_ADDR:prdata <= reg3;

default:prdata <= dummy_reg;

endcase

end

end

endmodule

总结

- 硬件思维和软件思维需要区分,Verilog是并行执行的

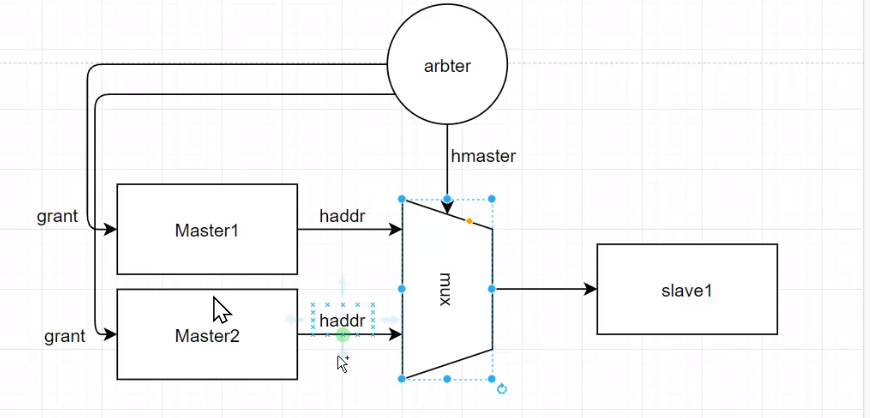

- 多个master,其中一个被grant,其他的master发送的信号仍然存在,所以需要mux通过hmaster进行选择master