APB Usage

- APB主要用于寄存器和外设(GPIO\TIMER\UART)的访问

- CPU 通过AXI接口发出transaction访问外设,AXI-based interconnect接收到AXI transaction,然后通过DRAMC接收到axi访问的请求,访问DRAM数据

- DRAMC中含有寄存器,其中寄存器的值是通过APB进行访问的,所以在AXI-based interconnect中有axi2apb_bridge,进行协议的转化

- CPU访问DMA中的寄存器也是通过APB总线访问

- ARM系统中有CoreSight debug&trace subsystem,调试模块,其于CPU的交互也是通过APB总线

The advantage of APB

- 协议简单

- 频率比较低,功耗低

- 性能比较差

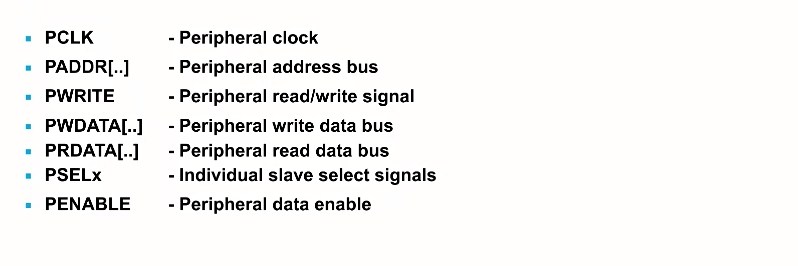

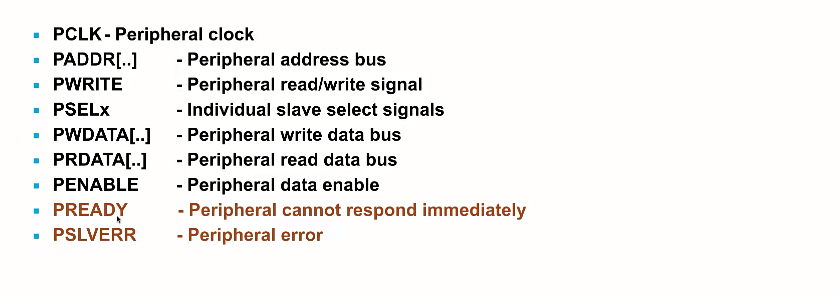

APB2 signals

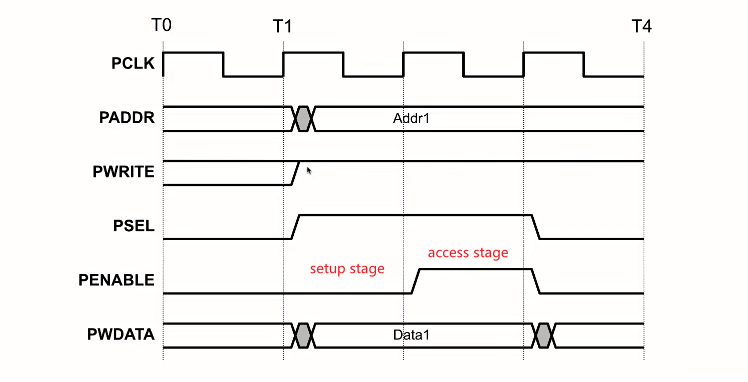

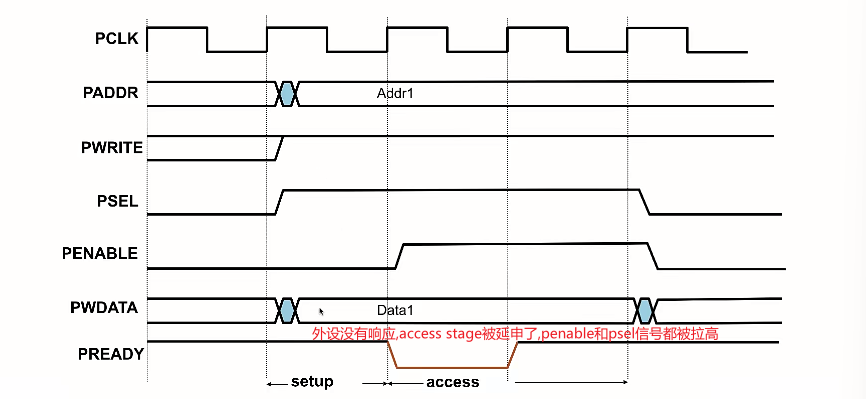

APB Write Timing

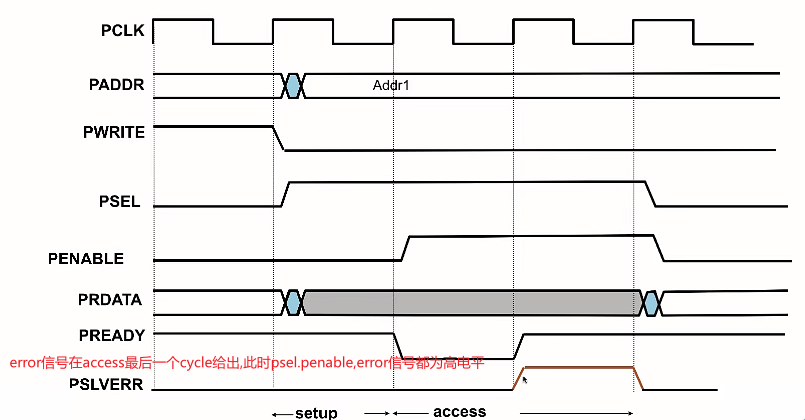

APB read timing

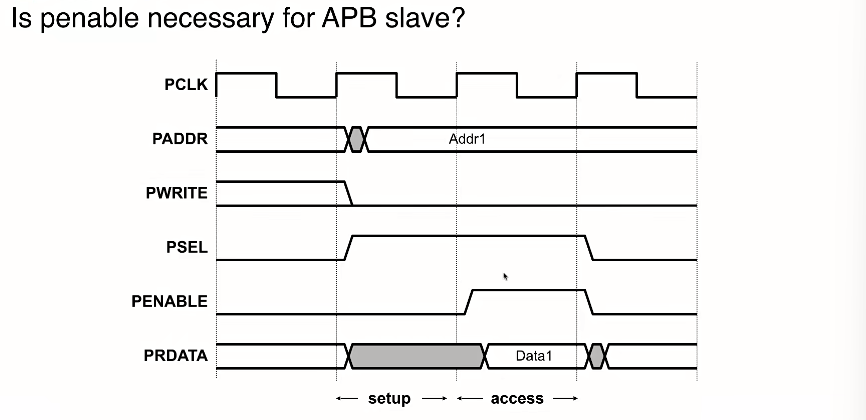

- 一次读写操作需要两个周期,penable为低的时候,处于setup stage,当penable为高的时候处于access stage

Question-1

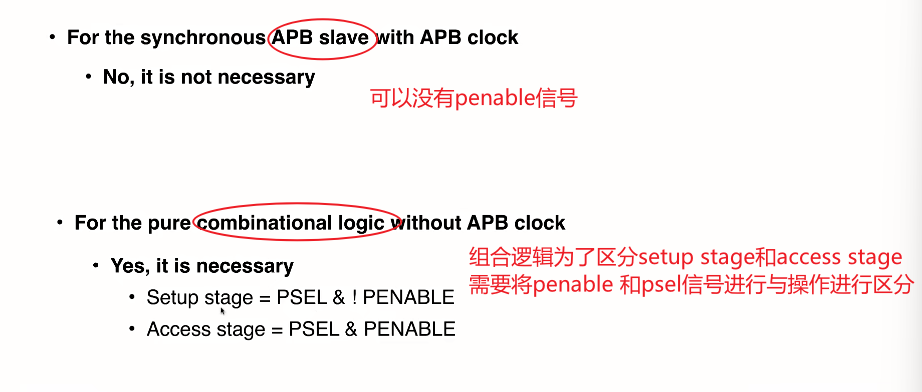

如果没有penable,是否可以? 在设计APB slave的时候,只要使用psel的第二个时钟上升沿返回数据即可,不需要penable(前提是有clk存在)

Question-2

-

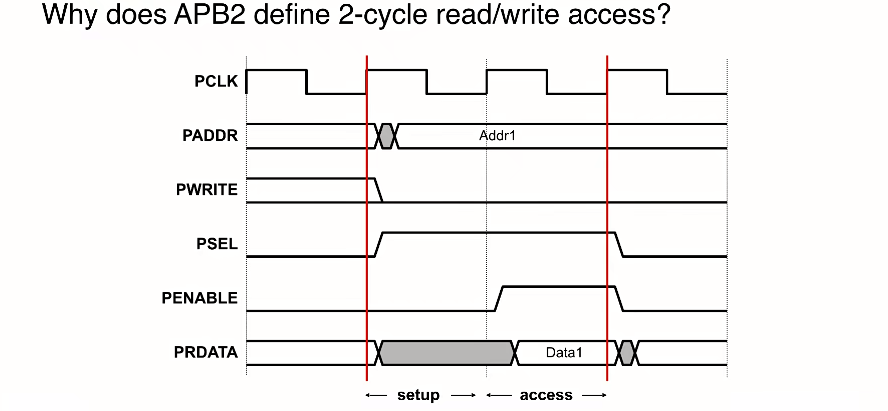

APB2只定义两个cycle的读写操作?两个cycle是否真的满足APB slave数据的响应?

-

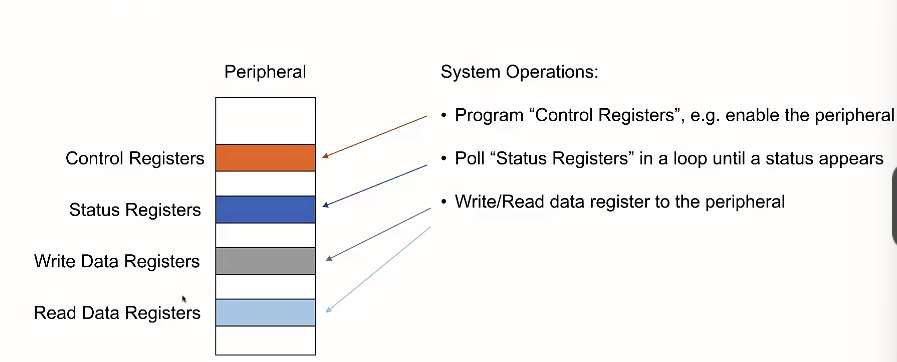

对于外设而言是由寄存器构成的,通过APB对于外设进行访问和操作,通常是通过寄存器进行的;通常先要program control register,使能外设;查询状态寄存器,状态寄存器满足条件,对相应的数据寄存器进行访问,对于寄存器操作,两个cycle就够了

-

对于外设内部操作而言,对于如果两个周期没有完成操作,会反应到status register,对于CPU而言,会一直查询status register,状态寄存器满足条件,才能对于数据寄存器进行访问和操作,对于APB而言都是操作寄存器,所以两个cycle是足够的

-

系统通过软件的方式不断查询外设的状态寄存器,查询外设是不是ready,如果ready执行下一步操作(软件的操作)

AHB3 signal

APB3 write cycle with wait states

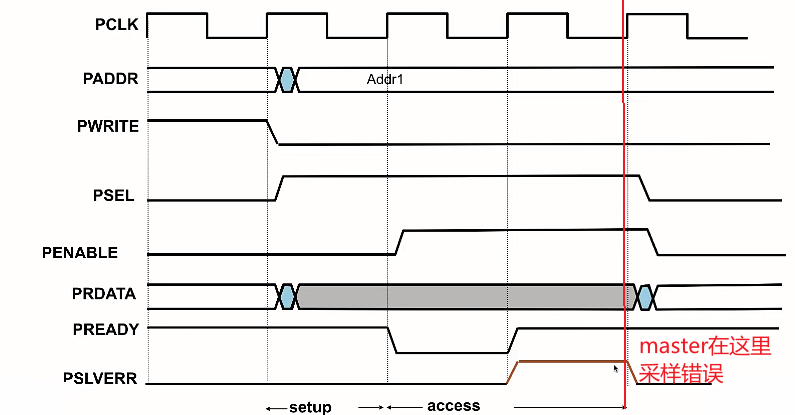

APB3 read cycle with slave error

- 当PSEL、PENABLE或PREADY为低电平时,建议但不是必须将PSLVERR驱动为低电平。

- 读传输也可能以错误响应结束,这表明没有有效的读数据可用。上图显示读取传输完成,并有一个错误响应。

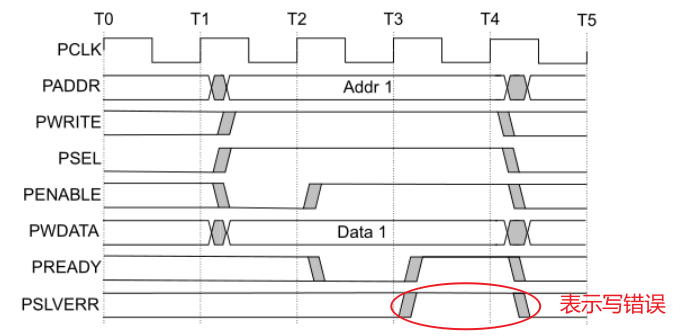

APB3 write error

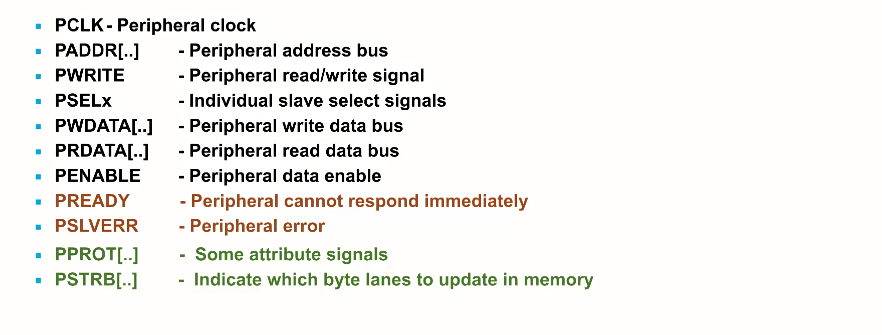

APB4 signals

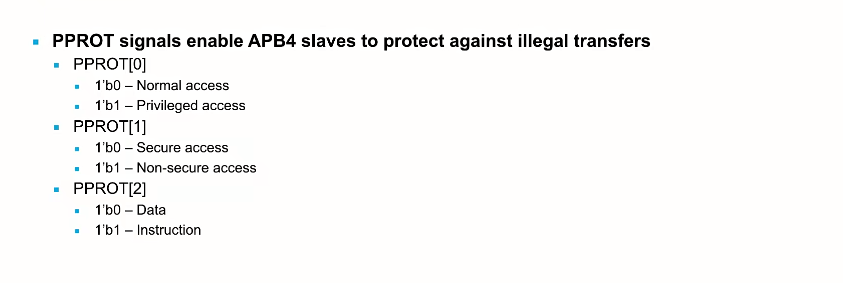

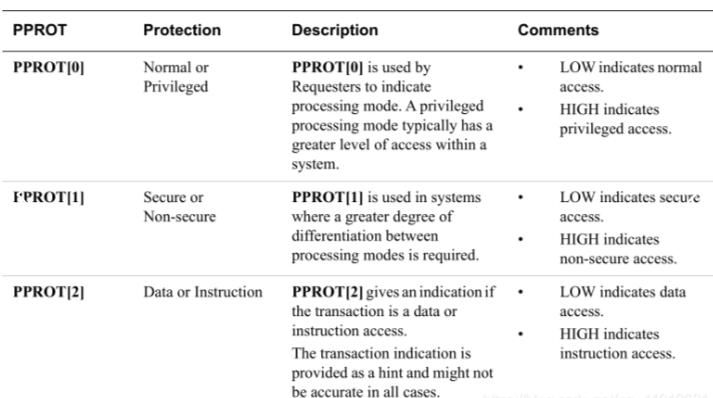

为什么需要APB4

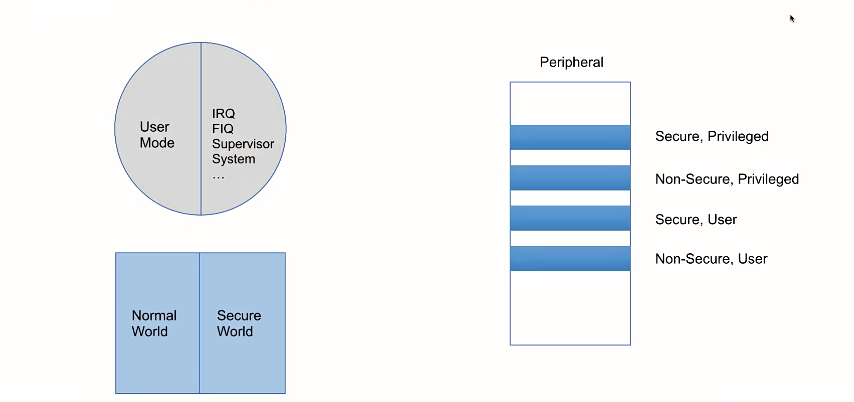

- cpu可以工作在user mode下或者是privilege mode(IRQ\FIQ\Supervisor\System)下

- 对于支持trustzone的cpu而言,cpu可以工作在Normal World下,也可以工作在Secure World下,对于CPU而言,不同secure状态下,发送出去的transaction是不同的

- user mode下发出的transaction就是normal access

- IRQ\FIQ mode发出的是privilege access

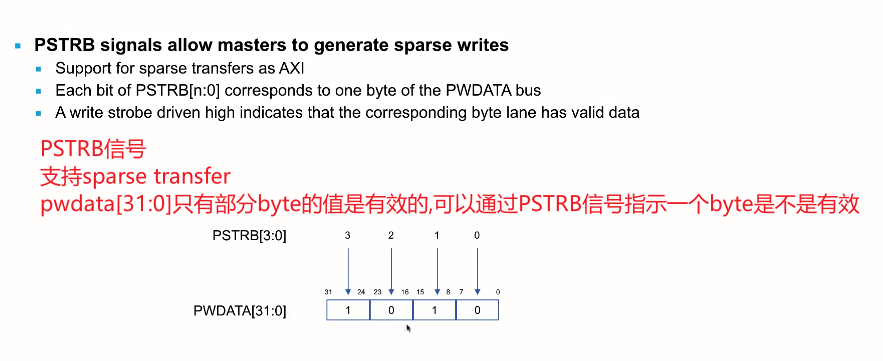

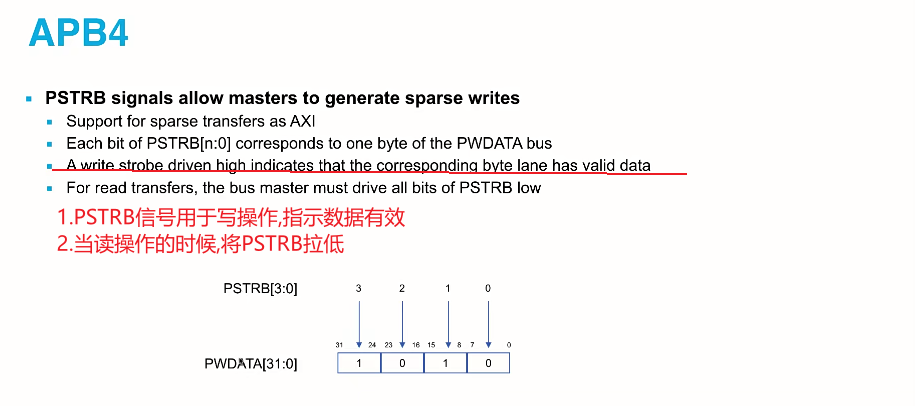

- 写数据总线的每8位有一个PSTRB,因此PSTRB[n]对应于PWDATA[(8n + 7):(8n)]**

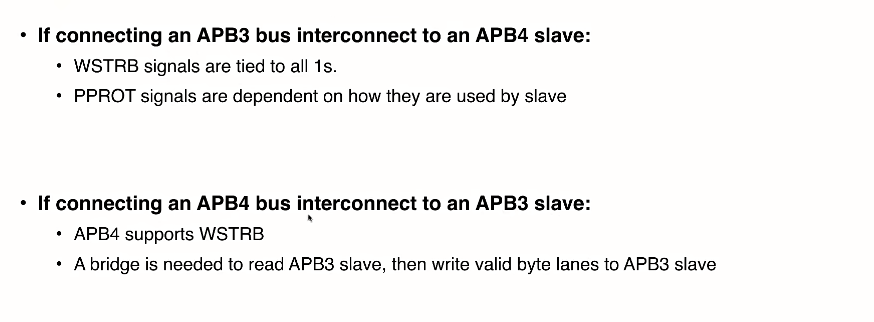

APB3和APB4 compatibility

- 如果将APB3 BUS总线连接到APB4 slave,只需要将WSTRB信号置为1,表示数据有效即可(WSTRB AP3不支持,APB四支持)

- PPROT信号取决于APB4的信号是如何设计的,如果APB4 slave只支持privilege mode的访问,PPROT[0]就要置位特权模式下访问的值;如果APB4 slave只支持secure mode的访问,PPROT[1]就要置位secure mode模式下访问的值

- 如果将APB4 BUS总线连接到APB3 slave,AHB4 BUS支持WSTRB信号,WDATA中有部分有效的数据,有部分无效的数据,但是APB3 slave是不支持的,所以需要设计一个Bridge,先读取APB3 slave地址空间的数据然后把有效的byte写到APB3 slave中