一、Vivado增量编译概述

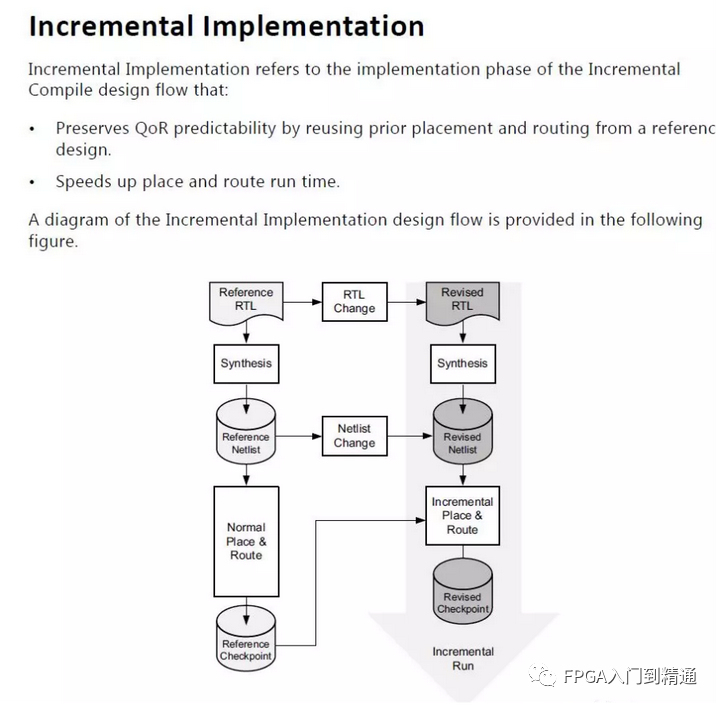

Vivado增量编译 (Incremental Implementation),是指针对设计中已经完成的部分,仅编译修改的部分,并在这些部分重新生成比特流,以加速设计实现的过程。简单来说,就是只更新那些被修改过的代码,而不是每次都对整个设计进行重新编译。

与传统的完全重新编译相比,Vivado增量编译的最大优势在于大幅度缩短了设计重复实现的时间。在设计中,有时只是对某一部分进行了小的修改,但是由于需要进行完全重新编译,再次生成比特流的时间就会非常长。因此,采用增量编译可以有效提高设计开发的效率,同时降低设计开发成本和周期。

二、Vivado增量编译的优点

1、 降低编译时间

Vivado增量编译只编译修改的部分,而不是每次都重新编译整个设计。这样可以大幅度缩短编译时间,提高开发效率。

2.、减少资源消耗

完全重新编译需要占用大量的计算资源,包括硬件资源和人力资源。而使用增量编译可以减少资源的消耗,从而降低开发成本。

3.、方便调试

当设计出现问题时,只需要对修改的部分进行重新编译,而不是对整个设计进行重新编译。这样可以更加方便地定位和解决问题,提高调试效率。

三、Vivado增量编译的使用方法

1. 设置增量编译

在Vivado中启用增量编译操作很简单,以编者的Vivado版本为例(2019.1),不管是综合还是布线,都支持增量编译,两个设置方式基本一样,这里给出布线的增量编译示例:

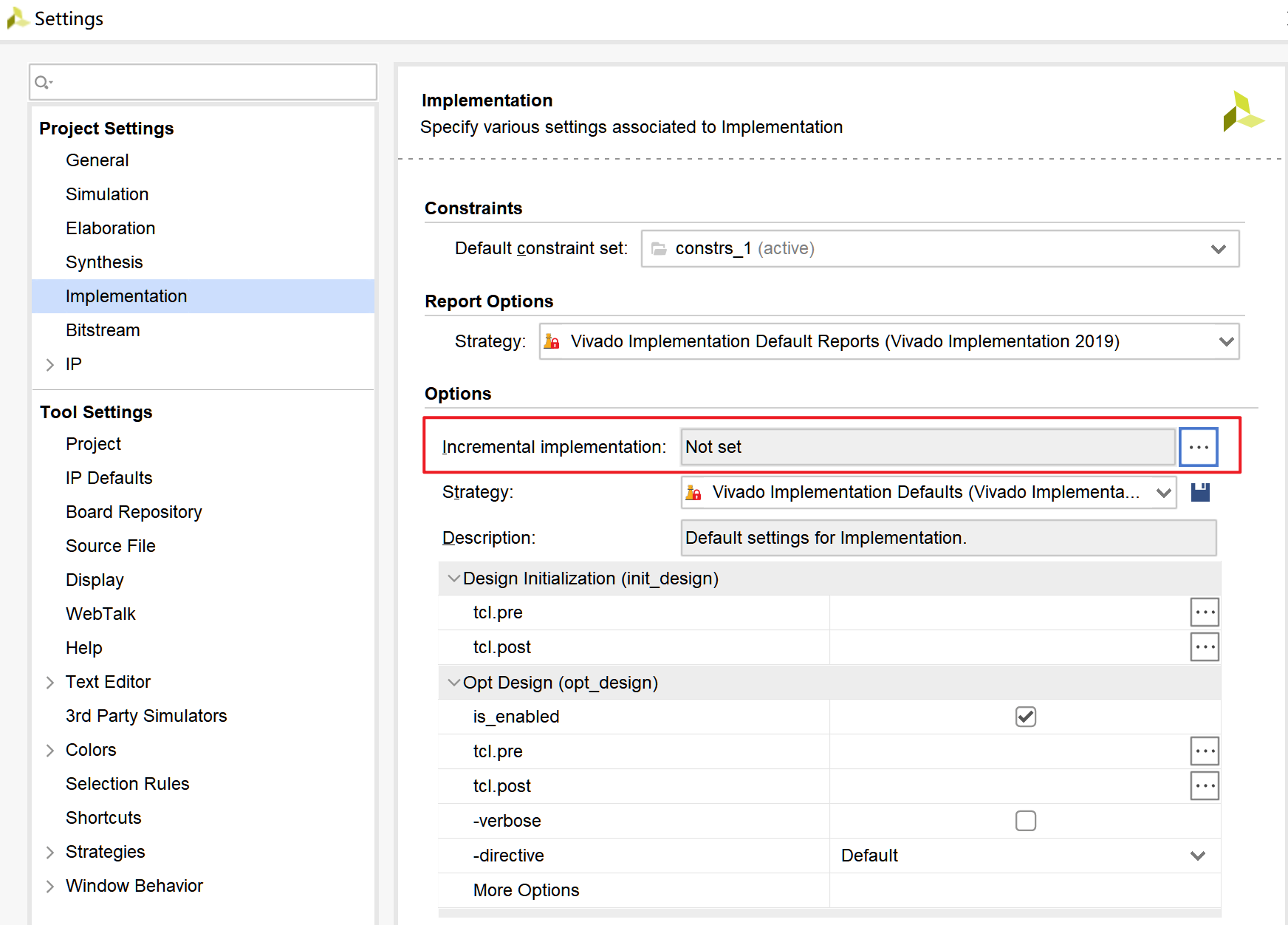

(1)打开“Settings”菜单并选择“Project Settings”下的“implementation”。

(2)在options窗口下,选择“Incremental compile”,点击选择文件窗口,如下图所示:

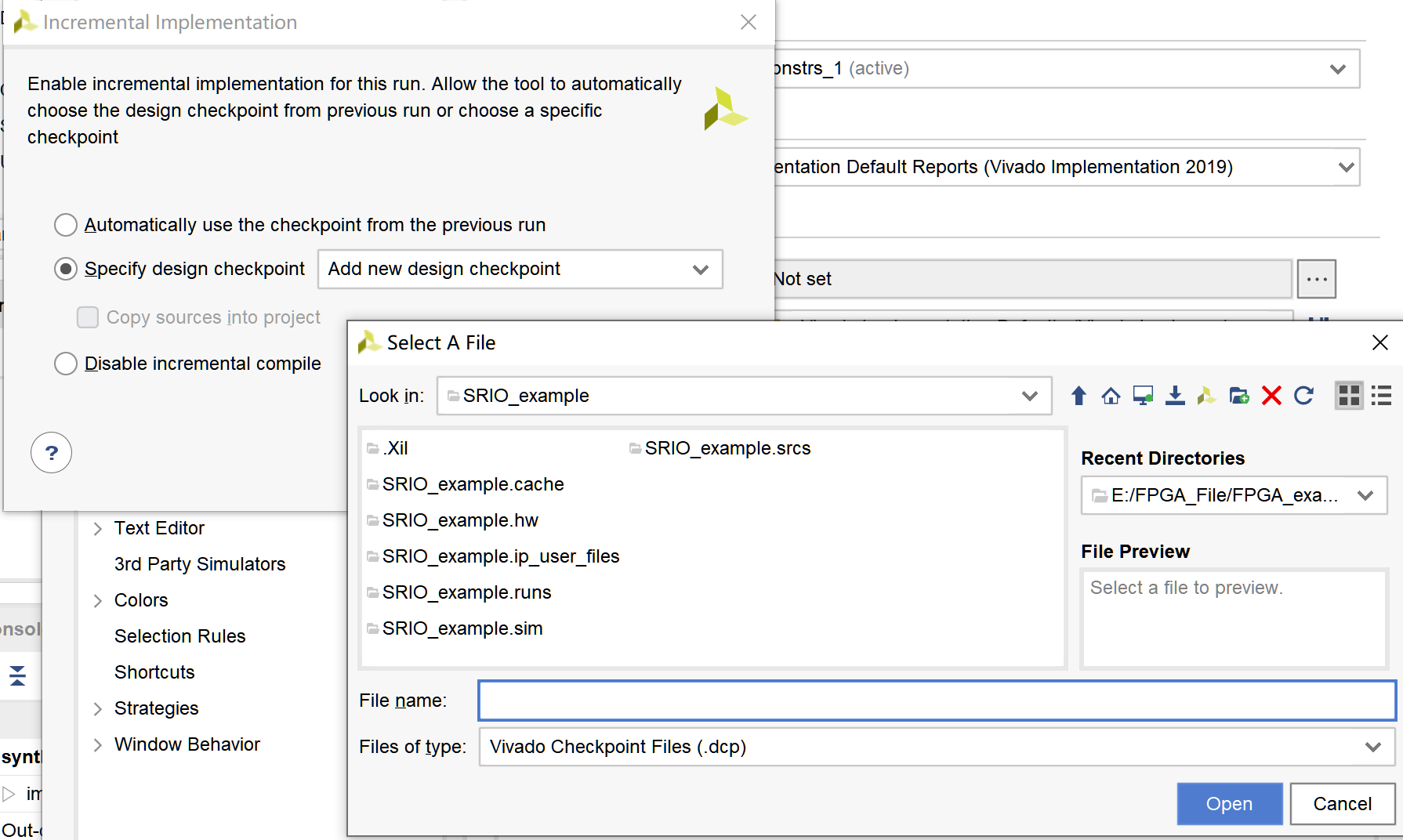

(2)弹出文件选择框,点击“打开当前目录”,再打开“.runs”->“impl”,选择“*dcp”文件。

3、重新执行综合、布线、生成bit文件即可,可以对比下完成时间,

四、Vivado增量编译的注意事项

1、不允许更改FPGA器件类型

如果您在增量编译期间更改了FPGA器件类型,则必须进行完全重新编译。因此,在开发过程中,请确保在编译期间不要更改FPGA器件类型。

2、避免修改顶层模块

顶层模块是设计中最基本的模块之一。如果您修改了顶层模块,则会影响整个设计。因此,建议避免修改顶层模块,以免影响增量编译的效果。

3、注意时序问题

在进行增量编译时,由于只更新部分代码,可能会导致时序问题。因此,在进行增量编译时,请务必注意时序问题,并进行必要的时序分析和优化。

五、总结

Vivado增量编译是一种非常重要的设计流程,它能够大幅度缩短编译时间,提高开发效率,降低设计开发成本和周期。在使用Vivado增量编译时,需要注意不允许更改FPGA器件类型,避免修改顶层模块,以及注意时序问题。只有在合理使用增量编译的前提下,才能够充分发挥其优势,提高FPGA设计的效率和质量。