TB1从verilog到SV的进场

要求1.1

一致,questasim对.v文件是兼容的

要求1.2(如果出现一致,可能是因为cho_margin的位宽问题,给的源文件位宽是5[4:0]不是6[5:0])

一致

要求1.3

一致

TB2方法task和函数function

要求2.1

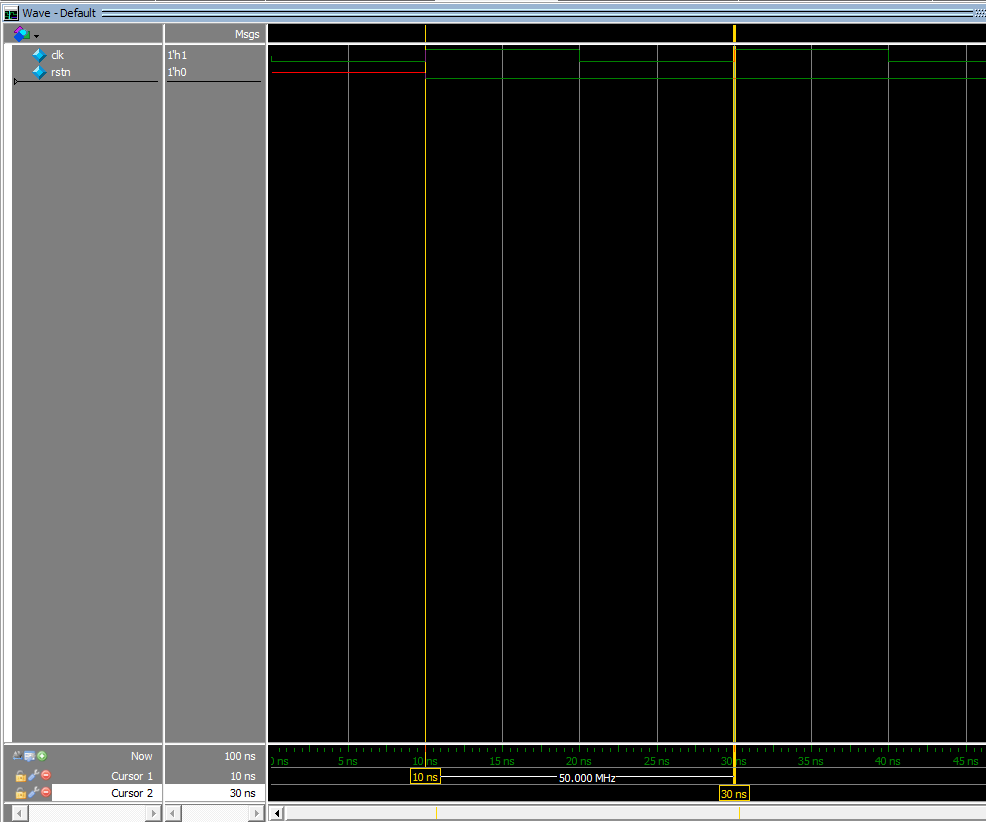

时钟和复位信号出现报红。(因为clk_gen()和rstn()没有被调用)

要求2.2

时钟复位,恢复正常。

要求2.3

在仿真文件中的多个initial块是并列执行的(并列执行时钟和复位),而放到一个initial块中顺序执行,会出现错误。

要求2.4

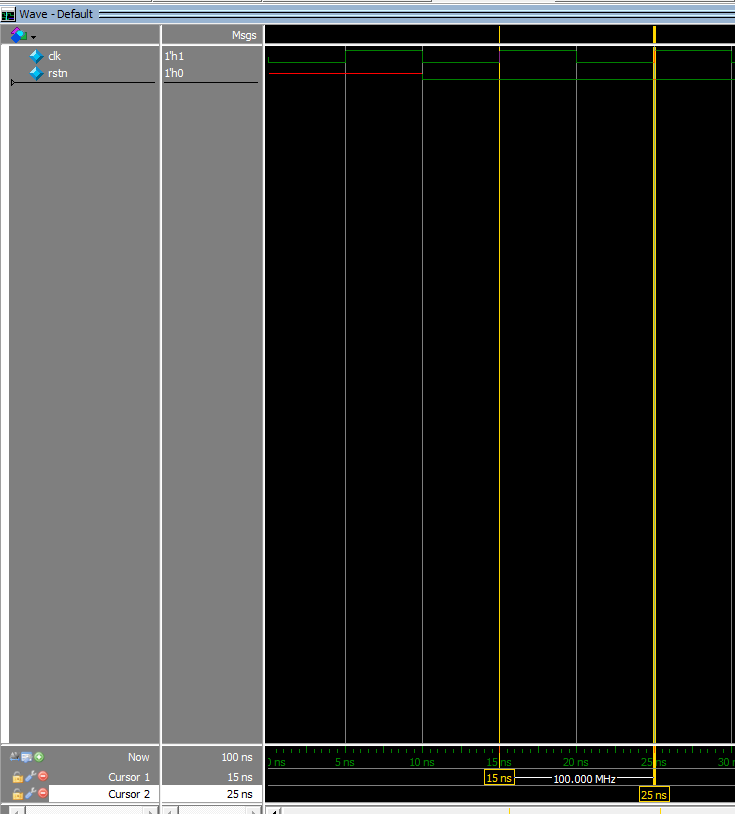

时钟的周期和频率,周期10ns,频率100Mhz。

修改代码为

1 // clock generation 2 // TODO:: please create task clk_gen(int peroid) 3 task clk_gen(int peroid); 4 clk <= 0; 5 forever begin 6 #(peroid/2) clk<= !clk; 7 end 8 endtask 9 10 initial begin 11 clk_gen(20); 12 end 13 14 // reset trigger 15 // create task rstn_gen() 16 task rstn_gen(); 17 #10 rstn <= 0; 18 repeat(10) @(posedge clk); 19 rstn <= 1; 20 endtask 21 22 initial begin 23 rstn_gen(); 24 end

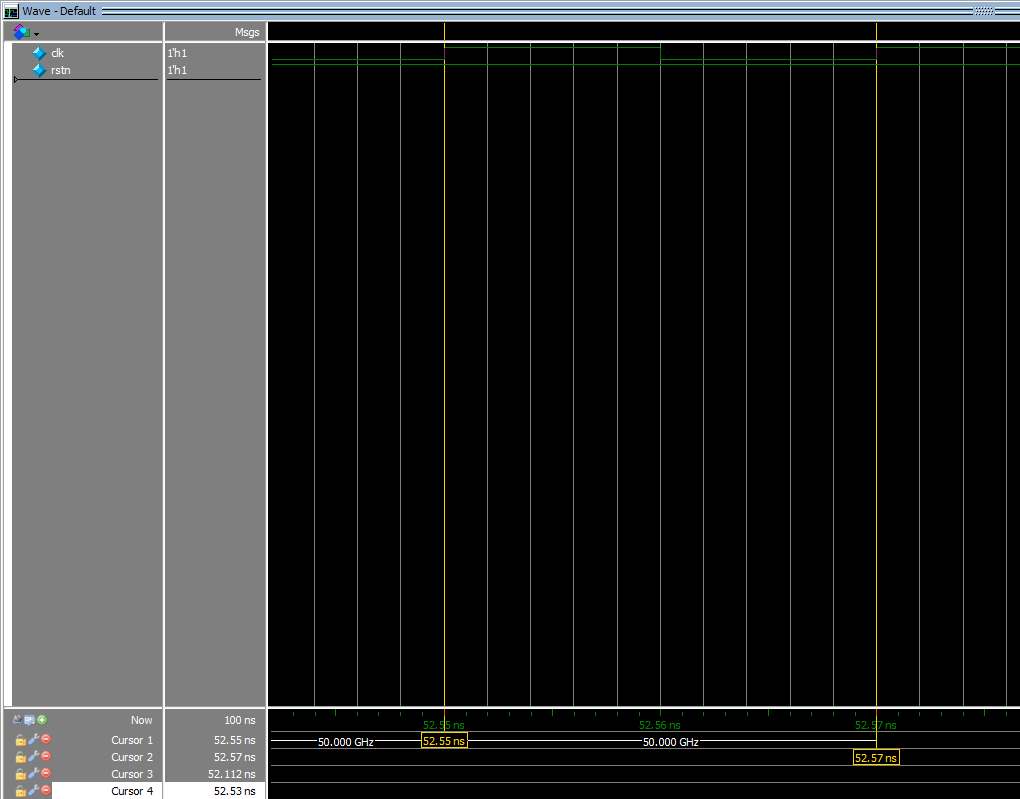

修改代码之后,时钟变为20ns,频率位50Mhz。

要求2.5

timescale 1ps/1ps,前一个1ps是代表的最小时间单位,后一个1ps代表的是精度,这里周期就变成了20ps,频率为50Ghz