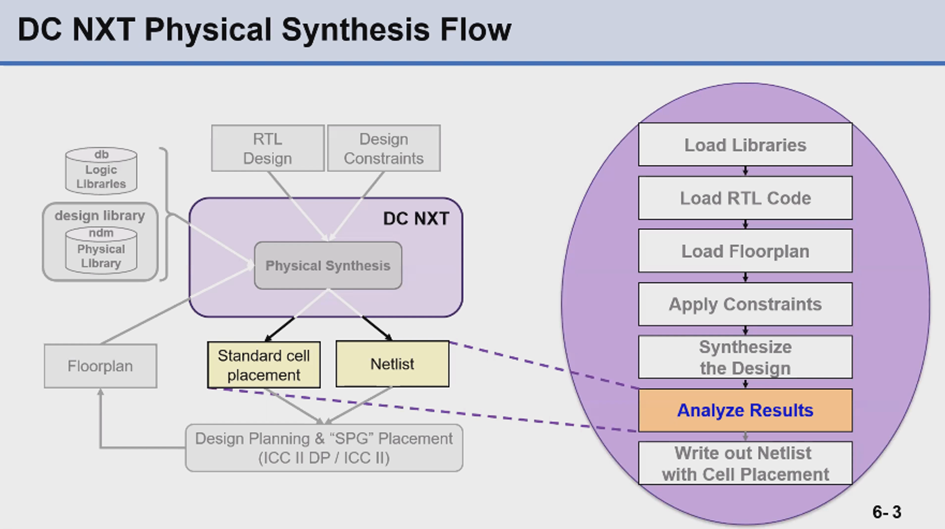

综合后时序分析

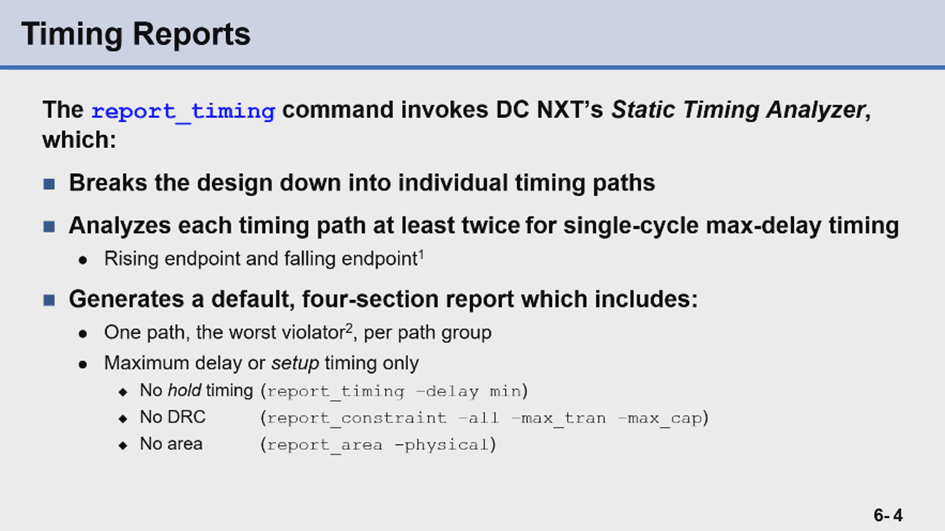

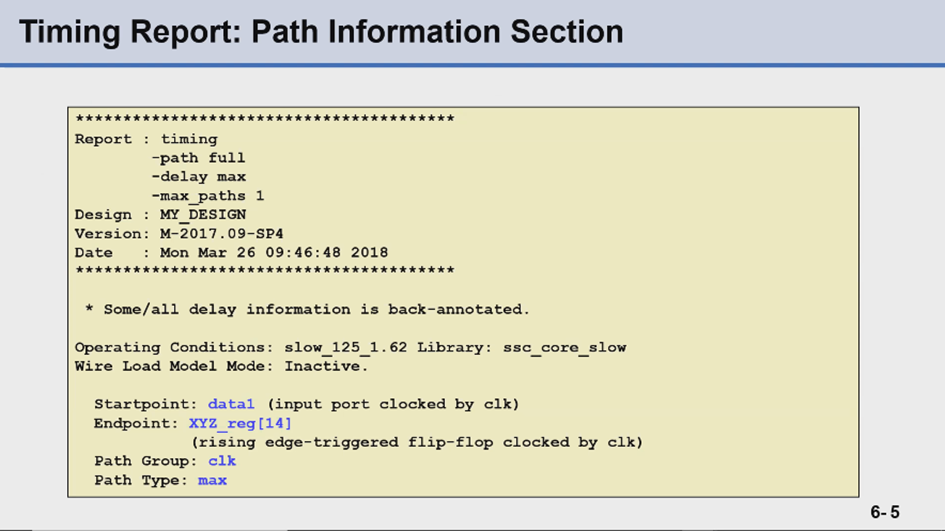

timing reports

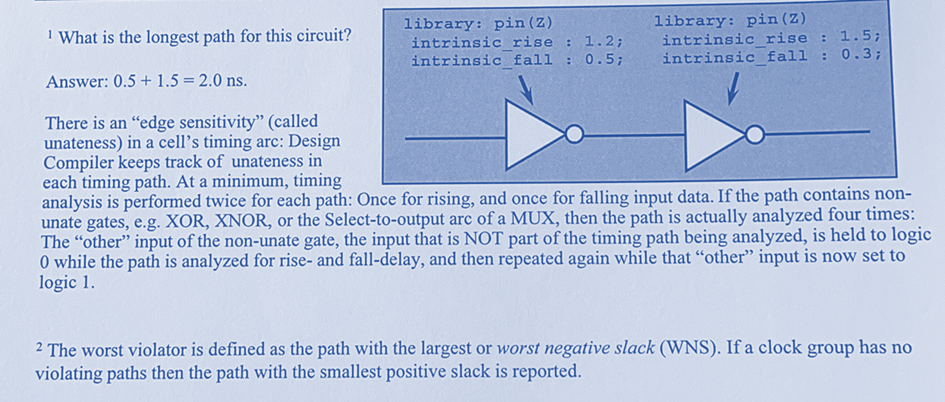

data到达input port的delay等于input port的launch的clock也就是external logic的clock latency值再加上input delay再加上input transition,知道的话,设置具体的值,不知道的话设置driving cell

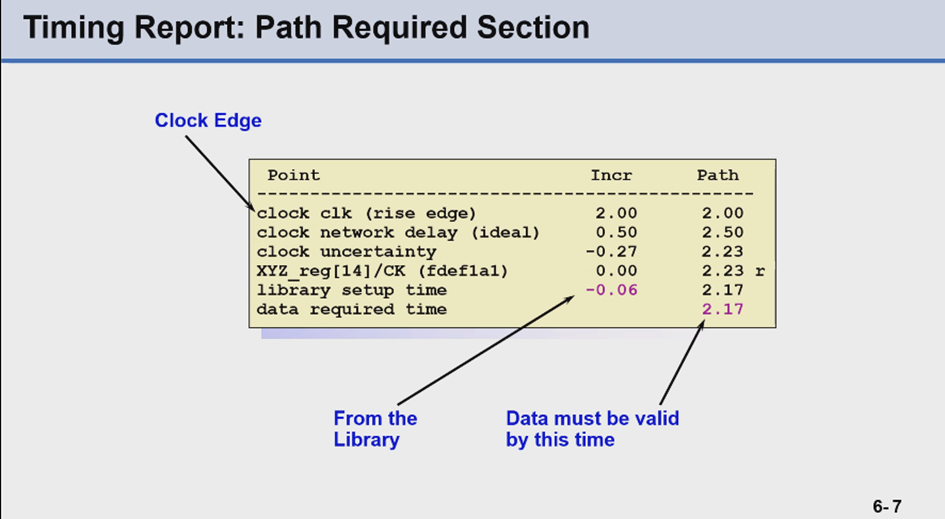

sourcel atency加上network delay显示为clock network delay。

默认情况下,输入端口的data arrival time等于input launching clock的 set clock_latency即:(clock_network_delay:network+source latency)加上 set_input_delay(input external delay),加上与input_transition or set_driving_cell相关的延迟(报告为input port上的增量延迟)。

如果set_input_delay包括-network_latency_included and/or source_latercy_included选项,则DC假设launching cloclk的延迟已经包括在set_input_delay上,因此,在输入数据到达时间上不增加额外的延迟.

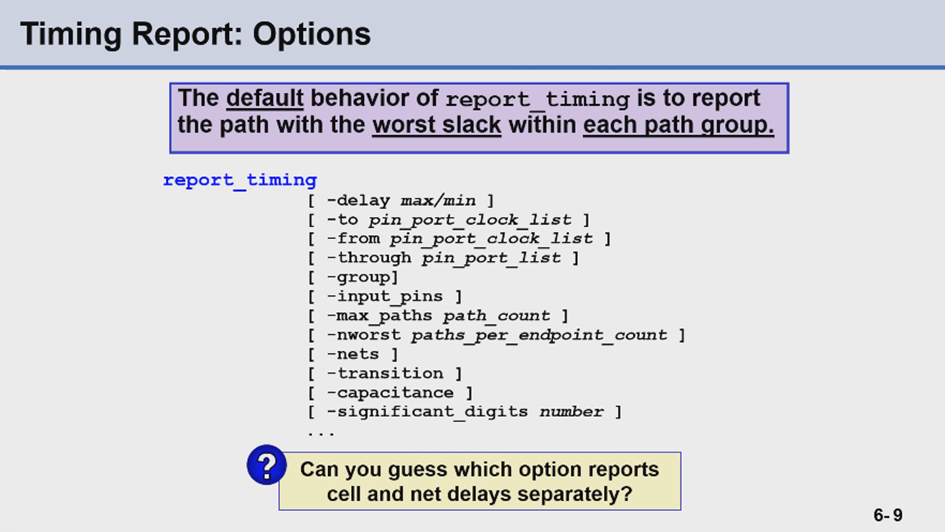

在一个cell的outputpin上的timingreport中显示的增量数字是celldelay和单元的输入引脚上的net的延迟时间之和。要将net延迟与cell延迟分开查看,请加上-input_pins,

使用-significant_digits <#>增加时序报告中的significant digits。

- input pins ! 默认情况下,延迟报告给cell output pins;除输出引脚外,该选项还包括对cell input pins的延迟。从一个单元的输出引脚到下一个单元的输入引脚的时间表示net delay,

report_timing " input_pins -significant digits

此选项显示连接到input pin的delay of the net

-max_paths 2:针对不同的endpoint报出最差的数量: -0.3 和 -0.15

-nworst每一个endpoint可以报的最差的数量-.3和 -0.25

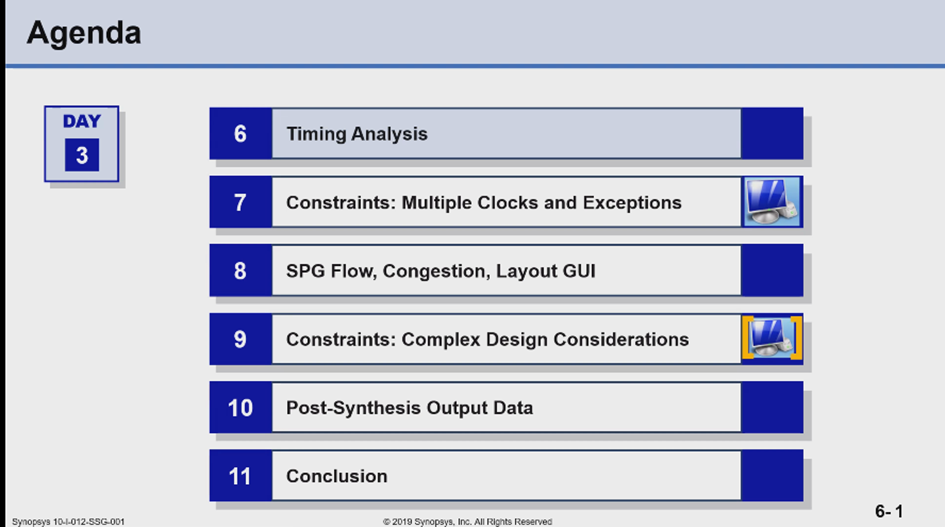

timing analysis

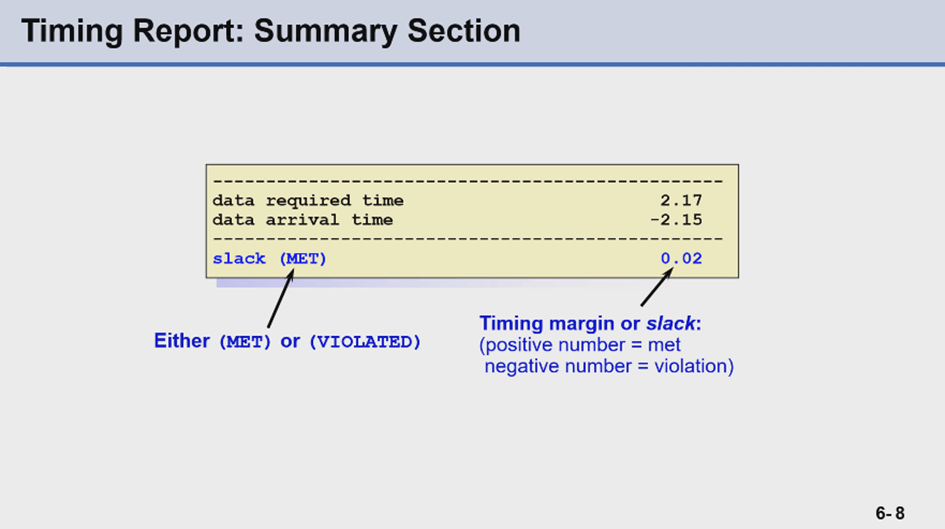

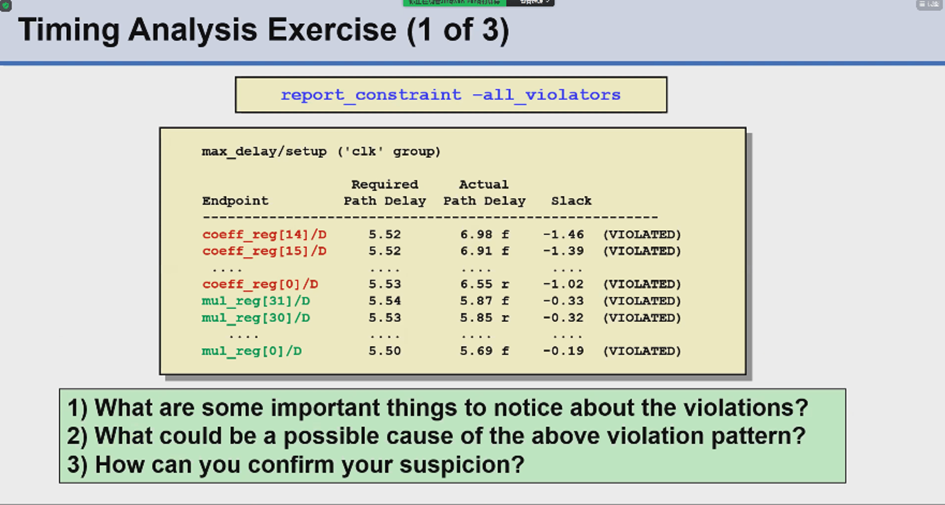

所有violations都在同一路径组中,称为“clk”,WNS violations超过26%(1.46/5.52),这是非常大的。有许多sub-critical violations以“coeff_reg”和“mul_reg”结尾。在“coeff_reg”结束的violations与在mul_reg结束的violations之间存在很大差异:

大的WNSviolations(1.46ns)可能是由于over-constrained input ports。剩余的violations可能是优化过程中“near critical paths”被忽略的结果。

“mul_reg”violations低于所需路径延迟的6%,这更合理。这些可能是由于over-constrained input ports而被忽略的regto regviolations。首先,找出“coeff_reg”和“mul reg”violations对应的路径类型:-input 或者regtoreg路径(它们不能是outputpath,因为endpoints是寄存器inputpin,如果它们是outputpath,则endpoints将是outputport)。这可以通过report_timing命令来显示。

接下来,使用report_path_group检查此路径组的“critical_range”是多少.

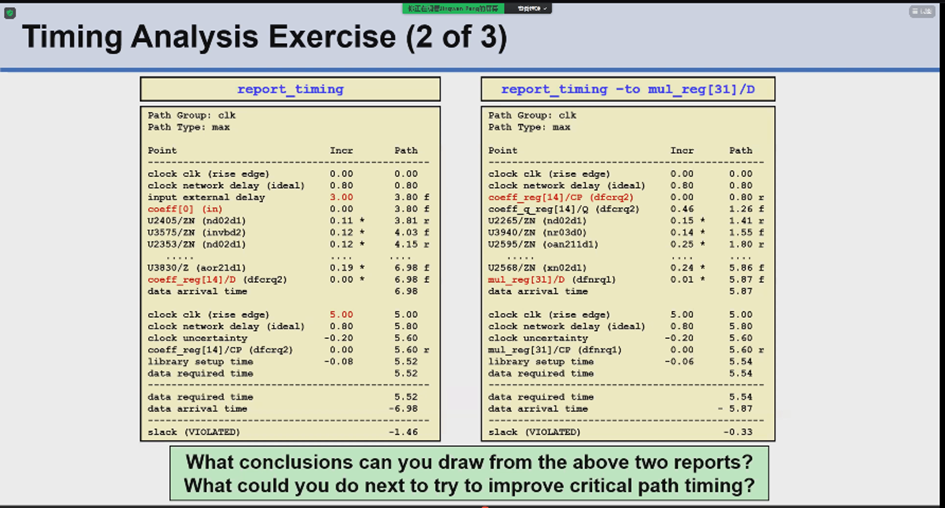

输入延迟设置过大,导致input port到reg的path成为critical path,导致工具不对sub critical path进行优化

1.关键路径为“输入”路径,"input delay"相对较大3ns,占5 ns时钟周期的60%。由此产生的大量违例可能是由于过度约束的input造成的。“mul-reg”路径是reg-to-reg路径。由于此路径与关键路径位于同一路径组中,并且它的最差时隙-0.33 ns远小于路径组的1.46 ns WNS,可能在优化过程中忽略了reg到reg路径

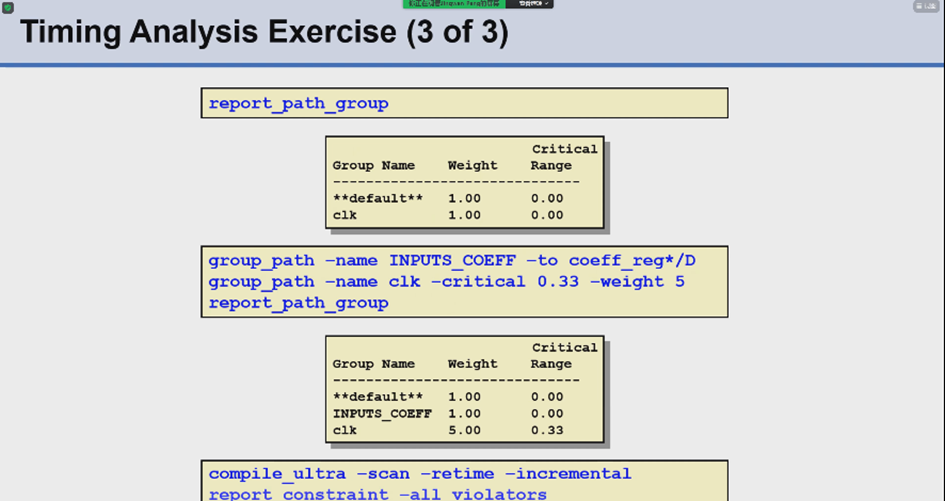

2.所以首先检查是否设置了非默认的路径组(例如非零的“critical range”值)。例如,如果“clk”path group已经具有1.5ns的critical range,那么为输入创建单独的路径组与为regtoreg路径创建单独的路径组可能不会导致显著的改进(非默认的“weight”可能会有所帮助)。接下来,为输入路径创建一个单独的路径组,并将critical range和weight选项应用于clk。

最后,执行增量编译,不必为这些patup创建路径组。由于没有output"or"combo"路径违例,因此不需要为这些路径创建单独的路径组,最后再次执行增量编译。

analysis recommendations

默认情况下,DC 对recoveryandremovetime是不会检查的,pt会set enable_recovery_removal_arcs true